简述SWD下载器通信协议底层原理

模拟技术

描述

基于Cortex-M内核的单片机,目前主流的下载接口就是JTAG和SWD。

SWD 和 JTAG引脚区别:

JTAG:

- TDI: Test Data In。串行输入引脚

- TDO: Test Data Out,串行输出引脚

- TCK: Test Clock,时钟引脚

- TMS: Test Mode Select,模式选择(控制信号)引脚

- TRST: Test Reset,复位引脚

SWD:

- SWDIO: Serial Wire Data Input Output,串行数据输入输出引脚

- SWCLK: Serial Wire Clock,串行线时钟引脚

其中SWD只需要两根线(SWCLK和 SWDIO),在PCB布局有限、引脚资源紧张的情况下,SWD算是一种不错的选择。

SWD简介

SWD:Serial Wire Debug,代表串行线调试 ,是ARM设计的协议,用于对其微控制器进行编程和调试。

市面上支持SWD调试接口的下载器很多,比如:ST-Link、 J-Link、 e-Link、 GD-Link等市面上绝大部分用于Cortex-M内核处理器的下载器都支持。

对于SWDIO,是双向(输入输出)数据引脚,必须在电路板上对线路进行上拉(ARM 建议采用 100 K)。

每次在协议中更改 SWDIO 的方向时,都会插入转换时间,此时线路即不受主机驱动也不受目标驱动。默认情况下,此转换时间为一位时间,但可以通过配置 SWCLK 频率来调整。

调试接口

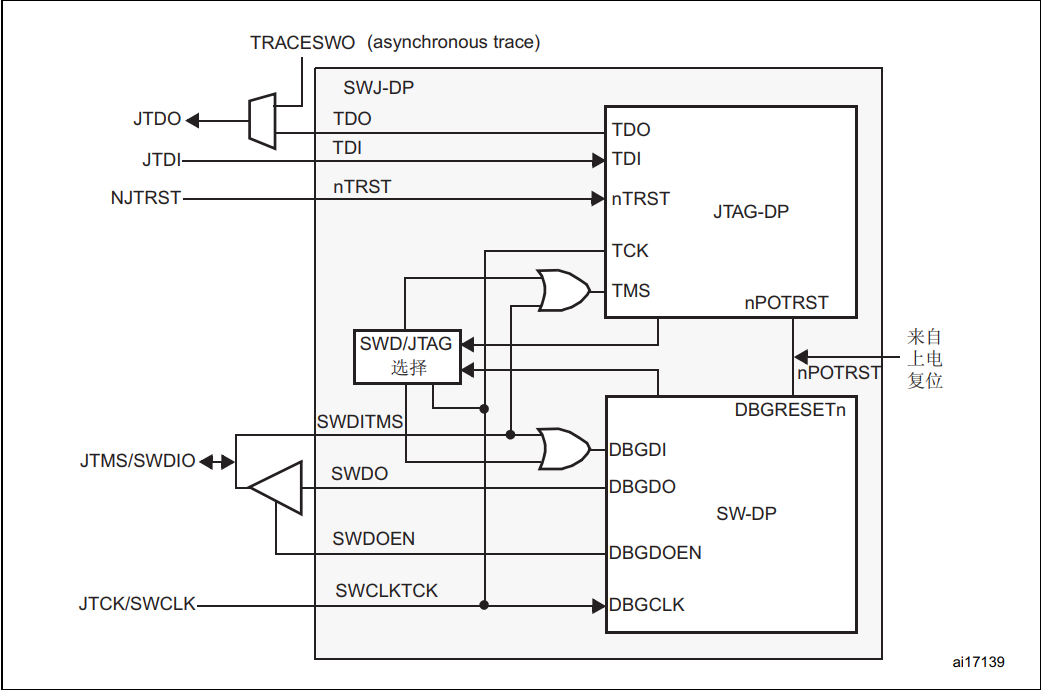

常见的Cortex-M内核处理器都集成了SWD和JTAG 调试端口,在 SWJ-DP 中, SW-DP 的 2 个 JTAG 引脚与 JTAG-DP 的 5 个 JTAG 引脚中的 部分引脚复用 。

JTAG与SWD的切换机制:

默认调试接口是 JTAG 接口,如果调试工具想要切换到 SW-DP,它必须在 TMS/TCK(分别映射到 SWDIO 和 SWCLK)上提供专用的 JTAG 序列,用于禁止 JTAG-DP 并使能 SW-DP。这样便可仅使用 SWCLK和 SWDIO 引脚来激活SWDP。

该序列为:

- 输出超过 50 个 TCK 周期的 TMS (SWDIO) = 1 信号

- 输出 16 个 TMS (SWDIO) 信号 0111100111100111 (MSB)

- 输出超过 50 个 TCK 周期的 TMS (SWDIO) = 1 信号

SW 协议序列

每个序列包括三个阶段:

- 主机发送的数据包请求( 8 位)

- 目标发送的确认响应( 3 位)

- 主机或目标发送的数据传输阶段( 33 位)

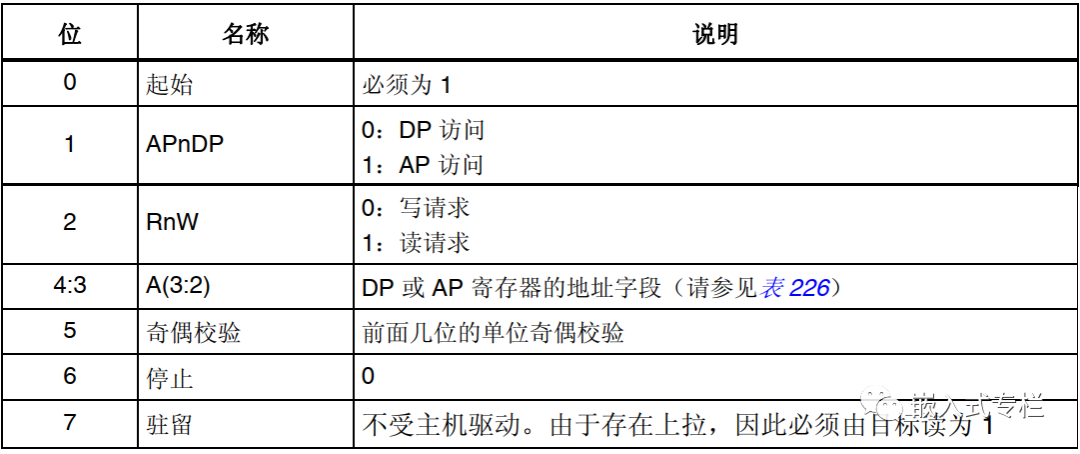

数据包请求( 8 位):

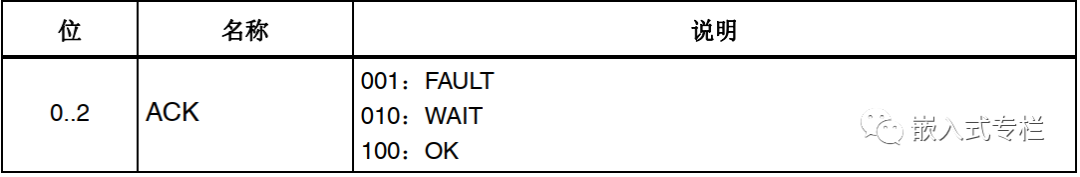

ACK 响应( 3 位):

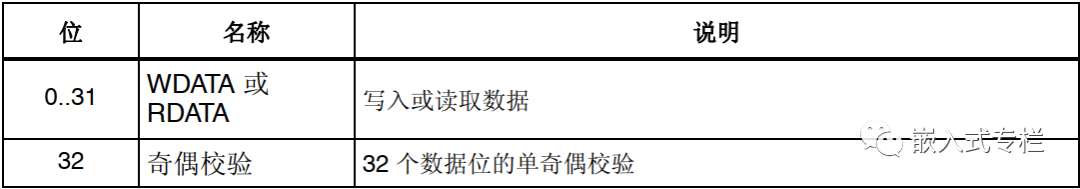

DATA 传输( 33 位)

这种类似于寄存器的一些Bit位操作,底层的一些原理与普通的通信协议也有类似之处。。

SW-DP 状态

SW-DP 的状态机有一个用于标识 SW-DP 的内部 ID 代码,其中主要包含的状态:复位、空闲状态、 ID 代码等。

- 在上电复位后、 DP 从 JTAG 切换到 SWD 后或者线路处于高电平超过 50 个周期后,SW-DP 状态机处于复位状态。

- 如果在复位状态后线路处于低电平至少两个周期, SW-DP 状态机处于空闲状态。

- 复位状态后,该状态机必须首先进入空闲状态,然后对 DP-SW ID CODE 寄存器执行读访问。否则,目标将在另一个事务上发出 FAULT 确认响应。

SW-DP 状态机的更多详细信息,可以参看Cortex-M相关的一些手册。

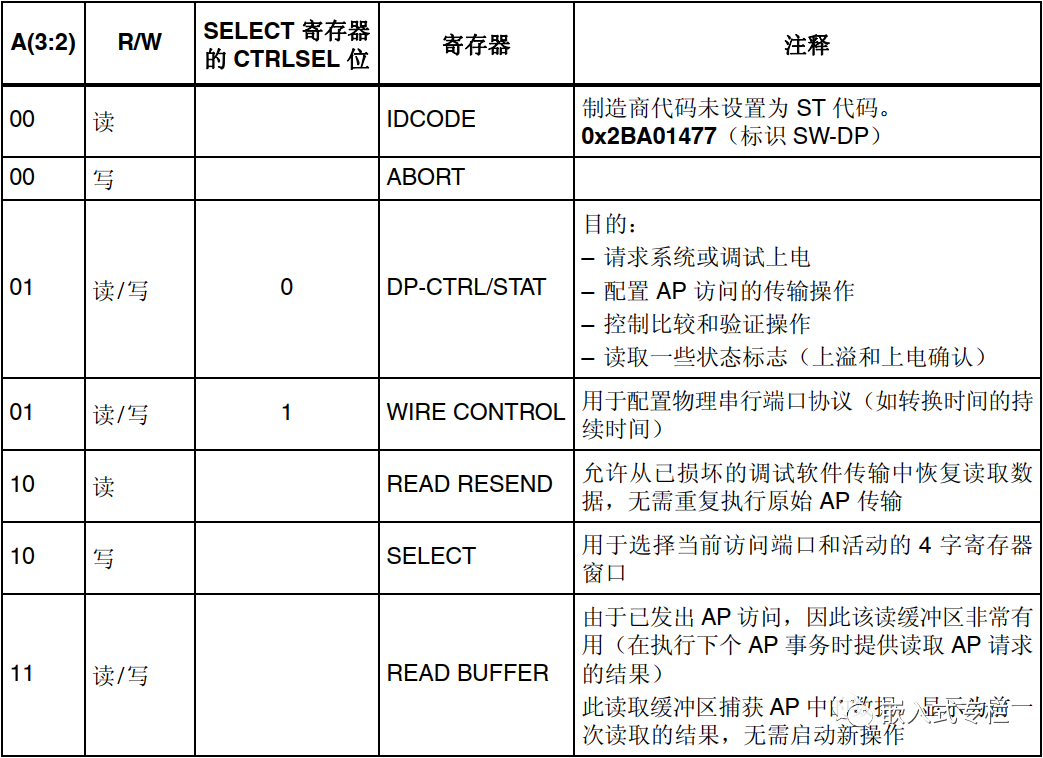

SW-DP 寄存器

SWD类似普通外设,也是有一种寄存器,开发者进行的编程(读写)操作,其实就是操作对应的寄存器。

SWD主要的底层就介绍到这里,更多详情,请参看Cortex-M内核手册

-

SWD调试通信协议2025-12-22 226

-

STM32中的通信协议是什么2021-08-18 2529

-

Modbus通信协议的相关资料下载2022-02-09 1509

-

如何实现基础通信协议的设计?2022-02-14 1854

-

简述一下Modbus串行通信协议2022-02-16 1153

-

串口通信协议的相关资料分享2022-02-22 2377

-

Modbus通信协议教程2015-12-08 1734

-

SCPI通信协议2016-05-04 2852

-

Robin通信协议的程序和工程文件免费下载2020-07-09 893

-

通信协议CANOpen堆栈手册资源下载2021-04-19 1235

-

上位机通信协议PPT课件下载2021-07-20 1230

-

MODBUS通信协议测试软件免费下载2022-04-13 1080

-

SWD下载器通信协议底层原理2023-02-13 5499

-

IP地址、端口号、通信协议的相关知识 TCP和UDP通信协议简述2023-07-18 3798

-

简单认识UART通信协议2024-07-25 3491

全部0条评论

快来发表一下你的评论吧 !