CMOS逆变器的特性/功耗/横截面/电路图

模拟技术

描述

CMOS逆变器

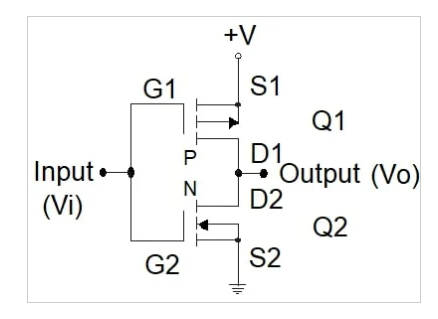

CMOS逆变器非常简单,它将功耗降至最低水平。它由一对增强型NMOS和PMOS组成,作为交换机运行,串联连接,如图所示。请注意,每个晶体管用作另一个晶体管的负载电阻。

CMOS逆变电路

栅极端子的接头是输入端,漏极的接头是输出端。PMOS (Q1) 衬底和源与 +V 绑定,而在 NMOS (Q2) 中,它们接地。

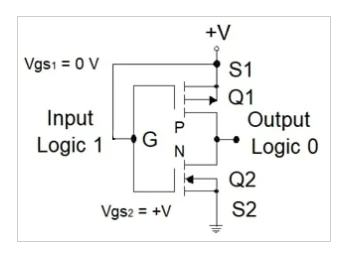

在晶体管Q2中对输入施加+V(逻辑1)Vgs = +V时,它被打开,其源极和漏极之间的电阻变得非常小。相比之下,晶体管Q1中的Vgs = 0 V,使其保持“关断”,漏极和源极之间具有高电阻。通过采用分压器规则计算输出电压,结果接近0 V(逻辑0) 。

输入端具有逻辑1的CMOS逆变器

因此,在输入端施加+V会导致输出端产生约0 V电压,从而建立所需的反转过程。

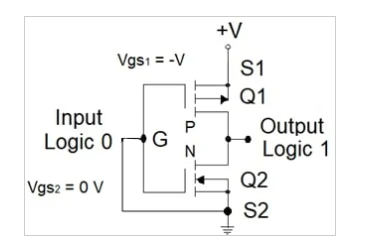

将输入接地,晶体管Q2中的Vgs = 0 V,保持“关闭”,晶体管Q1中的Vgs = -V,并且“导通”。现在,Q1在源极和漏极之间具有低电阻,Q2具有高电阻。因此,输出电压接近+V(逻辑1)。

输入端逻辑为0的CMOS逆变器

NMOS是一个下拉晶体管,因为它将输出下拉到地(零电压),而PMOS是一个上拉晶体管,因为它将输出上拉至+V。

CMOS的横截面

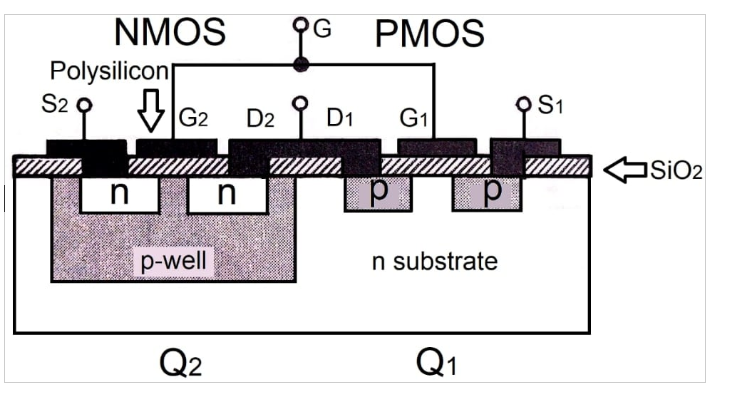

CMOS在基板上制造,用作电气参考并提供机械支撑。横截面将晶圆切开到晶体管的中间,并在其侧面观察。

图是CMOS栅极的粗略横截面,其中NMOS和PMOS晶体管在同一芯片上实现。对于p沟道和n沟道器件,右侧感应p沟道,左侧感应n沟道。

CMOS栅极横截面

在这种布置中,PMOS晶体管直接在n型衬底(体)中进行,NMOS晶体管在通常称为p阱的p型区域中进行。孔是一种重要的低掺杂水平的深扩散,可作为一个装置的基质,并在两种装置类型之间提供隔离。

采用p型底物作为主体并在n孔中形成p型器件也是可行的。未指定与n型体和p型孔的连接。

CMOS逆变器的功耗

CMOS电路的直流输入电流可以忽略不计。两种状态下的功耗都很低,因为“关断”晶体管将漏极电流限制在漏电流。功耗仅在输入切换期间才明显。

虽然CMOS的平均功率要求较低,但其幅度取决于电路的活动。例如,在静态电路中(不发生逻辑变化),CMOS消耗的功耗最小。与TTL相比,此功能使CMOS通常具有高能效。但是当以高频改变状态时,消耗的功率可能会几乎增加到TTL的水平。

CMOS逆变器的直流电压传输特性

直流电压传输特性(VTC)有助于量化逆变器的运行。但是,它只是一个输出电压 (Vo) 与输入电压 (Vi) 的关系图。

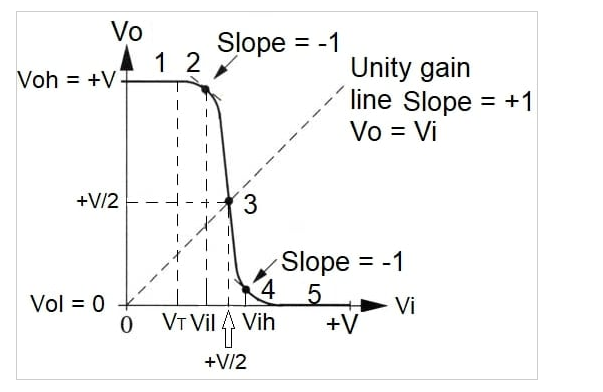

采用CMOS技术的逆变器具有非常接近理想的VTC。例如,图显示了Q1和Q2匹配的CMOS逆变器的VTC。

CMOS逆变器的VTC

在Q1和Q2匹配的情况下,逆变器具有对称传输特性,并在上拉和下拉方向上具有相等的电流驱动能力。CMOS逆变器的一个重要特性是高输出电压摆幅。

如图9所示,VTC根据Q1和Q2的操作模式分为五个部分:

第 1 部分:Q2 关闭

第2段:Q2处于饱和状态,Q1处于欧姆区域

第 3 部分:Q1 和 Q2 饱和

第 4 段:Q1 处于饱和状态,Q2 处于欧姆区域

第 5 部分:Q1 关闭

该图允许我们将逻辑 0 和逻辑 1 电压定义扩大到每个逻辑电平的电压范围。此外,用于定义逻辑 0 和逻辑 1 值的限制对于输出和输入是不同的。有效值是输入电压 Vih 和 Vil、输出电压 Voh 和 Vol 以及阈值电压 VT.

Vih和Vil是VTC点,其斜率(dVo/dVi)为−1 V/V。当Vi》Vil时,逆变器增益增加,VTC进入其过渡区。同样,当Vi《Vih时,逆变器进入过渡区域,增加增益。

VTC的另一个基本要素是单位增益线。这条线的斜率 = 1,并将曲线切割到 Vo = Vi 的点。在VTC的中点,逆变器切换状态。因此,使用上述VTC,输出在地+V(+V/2时)之间精确地改变状态。

当晶体管Q1和Q2不匹配时,VTC将不对称。

-

请问逆变器电路图原理是什么?2019-09-11 2801

-

正弦波逆变器的电路图和相关资料2020-10-26 10520

-

学习逆变器电路图2021-11-27 4118

-

隧道横截面对电磁波传播特性的影响2009-05-14 737

-

逆变器电路图2007-12-08 27476

-

车载逆变器电路图2008-11-28 8870

-

简易逆变器电路图2009-05-13 7939

-

什么是逆变器_逆变器原理_逆变器电路图介绍2018-03-02 32329

-

PCB电镀通孔横截面的典型现象的原理图免费下载2019-04-24 1921

-

简单逆变器电路图2019-10-23 30171

-

横截面流量计的介绍2020-03-22 1930

-

常见的八种逆变器电路图分享2020-10-28 121968

-

漆包线的横截面定义2023-06-25 2769

-

导体的电阻与长度和横截面积的关系是什么2024-02-26 16103

-

影响CMOS逆变器功耗的因素2024-09-12 2051

全部0条评论

快来发表一下你的评论吧 !