用更多选择回应积极的反馈

模拟技术

描述

反馈是一件好事——控制工程师希望反馈为负值,具有不错的增益和相位裕量,但营销人员更喜欢积极的反馈,例如客户要求在 UnitedSiC Gen 750 SiC FETS 的 4V 级别中提供更多选项。该公司凭借其 18 毫欧和 60 毫欧器件引领市场,但在某些应用中,更低的电阻部件和更高的中间值将是有益的。这取决于应用和预算 - 具有最低导通电阻的单个优质SiC FET占用的空间最小,需要最少的组装,但并联,具有相同导通电阻的低成本部件通常同样有效,特别是当有空间将热量分散出去时。但是,这需要设备并联和更多的设计工作。

第 4 代 SiC FET 系列增加了更多器件

为了提供这种灵活性,UnitedSiC 提供了额外的第 4 代 750V SiC FET,导通电阻为 23、33 和 44 毫欧,以及 6、9 和 11 毫欧的部件,这是对已经推出的 18 和 60 毫欧器件的重大改进。现在,客户可以“混合搭配”,以获得针对其特定热和工作条件的价格和性能的最佳组合,也许可以利用低成本部件的批量定价,使它们与不同的设计通用,并根据需要或多或少地并行。

并联SiC FET很容易,栅极驱动功率非常低,因此并联的额外功率通常无关紧要。器件由于其导通电阻正温度系数而自然共享电流,并且还有一个额外的相关优势,即与单个 9 毫欧器件相比,两个 18 毫欧并联的器件总共具有更少的传导损耗。这是因为两个器件中每个器件的一半电流产生的功率是单个器件的一半,并且每个器件的温升更低,并且导通电阻按比例上升得更少。较低的结温自然也会提高可靠性,从而在已经很高的SiC最大值下提供更大的裕量。UnitedSiC FET-Jet基于网络的计算器(现在为版本2)可用于查看效果,并给出各种应用和工作条件下任意数量的并联SiC FET的实际损耗和温升数字。

第 4 代碳化硅 FETS 仍然是同类领先的

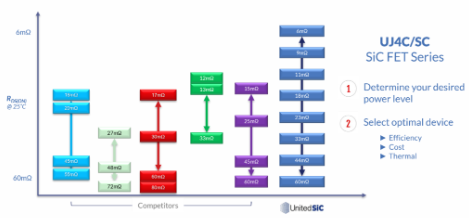

新增系列具有与其稳定产品相同的领先品质因数,并具有相同的先进第 4 代制造功能,例如晶圆减薄以减少基板传导损耗和银烧结芯片连接,以实现最低的结壳热阻和相应的低结工作温度。这些器件采用 TO-247 3 引脚封装和额外的 4 引脚封装,当需要源极“开尔文”连接时。图1总结了新型750V SiC FET与竞争产品SiC MOSFET相比所处的位置,请记住,这些FET的额定电压仅为650V。

图 1:在竞争格局中新增的 UnitedSiC 750V SiC FET 系列产品

UnitedSiC 750V SiC FET 系列具有更多器件选择的灵活性,这意味着它们可以应用于许多应用 - 通过汽车 AEC-Q101 认证,它们可用于牵引逆变器、车载和非车载充电器、DC-DC 转换器和无线充电,与 650V 额定器件相比,可提高效率并改善电压裕量。目前可用的超低导通电阻在交流和直流固态断路器应用中也很有价值,在这些应用中,低传导损耗对于效率和小尺寸至关重要。通常,在工业和IT电源转换产品中,第4代SiC FETS还可以提高硬开关和软开关拓扑的性能。

审核编辑:郭婷

-

集成电路设计在线学习,有更多选择了!!2015-09-24 2744

-

多选按钮2016-11-18 7717

-

怎么为中断向量的生成脚本添加更多选项?2019-03-22 1936

-

IIC通讯失败发送数据无回应2019-04-26 4799

-

用CAD删除选择多选的实体怎么操作?2019-08-06 1385

-

列表框多选2022-05-12 7026

-

选择电压反馈与电流反馈运算放大器的技巧2010-03-25 6527

-

放大电路负反馈的使用及选择2010-05-23 3536

-

中兴首次回应“拒绝令”_全面评估事件影响 积极应对2018-04-29 2531

-

MT-060:在电压反馈和电流反馈运算放大器之间选择2021-04-27 1289

-

借助更多的选项响应正反馈2023-06-15 1189

-

离线语音技术给智能照明带来更多选择2023-06-20 1761

-

鸿海集团回应富士康遭调查积极配合 然工业富联跌停2023-10-23 1280

-

基于PIC单片机的多选择性漏电保护2023-10-30 390

-

SG-8101可编程系列晶振为汽车电子提供更多选择2024-08-07 496

全部0条评论

快来发表一下你的评论吧 !