以太网网口与FPGA连接的常用方案

可编程逻辑

描述

当今,随着互联网技术的迅速发展,采用以太网实现数据采集和控制方面的应用,成为了电子系统设计的热点。以太网具有价格低廉、稳定可靠、传输速度快、传输距离远等特点,以太网技术发展成熟,具有很高的性价比。采用以太网技术的设备,可以通过TCP/IP协议进行数据的传输,不需要进行传输协议转换,使用和维护设备简单。随着技术的发展和各类应用的需求,出现了各种以太网的标准,包括标准以太网(10Mbit/s)、百兆以太网(100Mbit/s)、千兆以太网(1000Mbit/s)和10G(10Gbit/s)以太网[1]。不同类型的以太网有其各自需要遵循的标准,同时其所用的传输介质以及数据吞吐量也各不相同。千兆以太网技术作为新一代的高速以太网技术,它可以提供1Gbps的通信带宽,采用和传统10M、100M以太网同样的CSMA/CD协议、帧格式和帧长、全/半双工工作方式、流控模式以及布线系统,给用户带来了提高核心网络的有效解决方案,这种解决方案的最大优点是继承了传统以太网技术价格便宜的特点。

对于学习者而言,你就是要搞清楚弄明白以太网如何去实现,在实际操作中怎么去做,从这个角度出发的话,你就会发现其实没那么复杂,这就是说起来没那么难。那真正实现起来,到具体的各个接口以及细节的调试以及调通,你会发现还是比较烧脑的。所以呢,咱们先来聊一聊以太网的各个接口,从大体框架来分析如何去学习。

咱们就以千兆以太网举例,千兆以太网,只是说以太网的速率为千兆,也就是1G。除了千兆网,还有百兆网,万兆网,当然这些都是指的以太网的速率。不同速率的以太网,在FPGA端的接口表现形式也是不一样的。下边就来介绍百兆网和千兆网的接口形式。

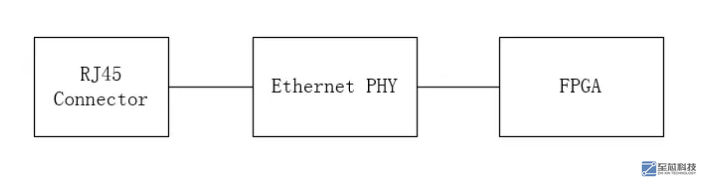

这是网口与FPGA连接的常用方案,RJ45就是咱们平常说的水晶头,Ethernet PHY是以太网的PHY芯片,之后就是Ethernet PHY与FPGA相连。

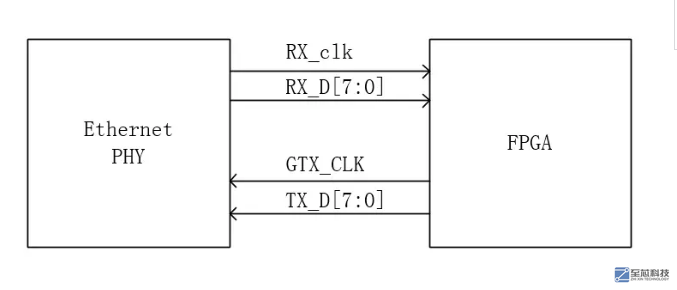

下边是以太网PHY芯片与FPGA连接的简单的架构图(不代表全部的信号输入输出端口)

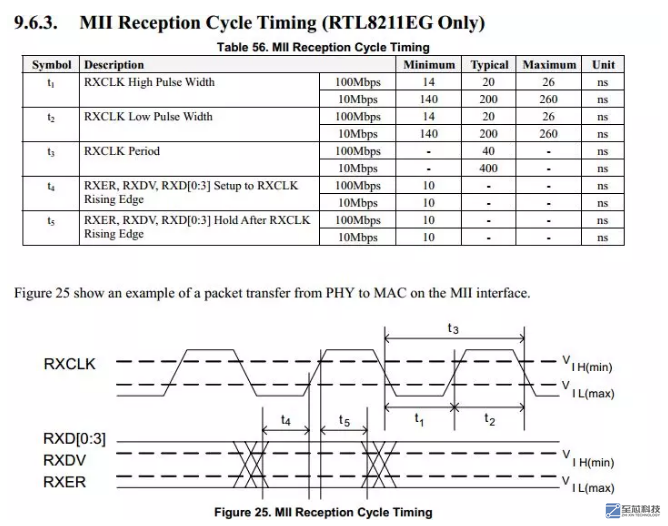

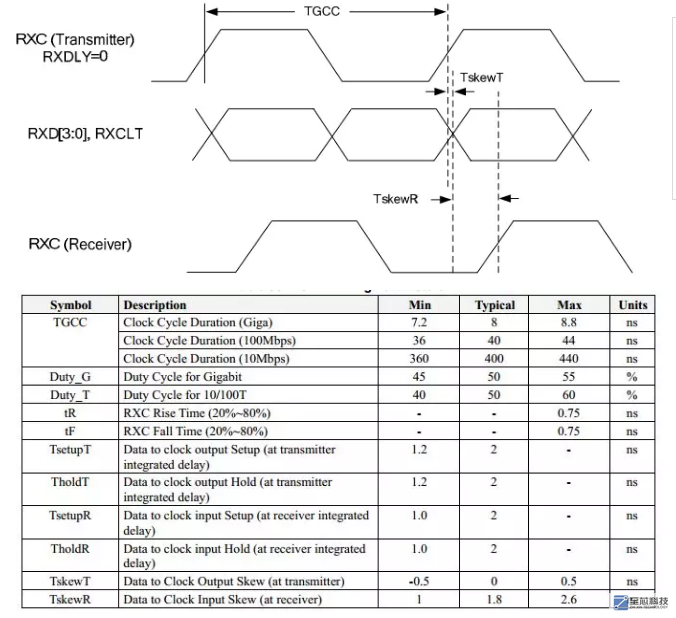

先说百兆网,百兆网的接口一般为MII(Media Independent Interface),当然10M网用的也是MII接口。下图是一块以太网PHY芯片的一些手册资料截图。

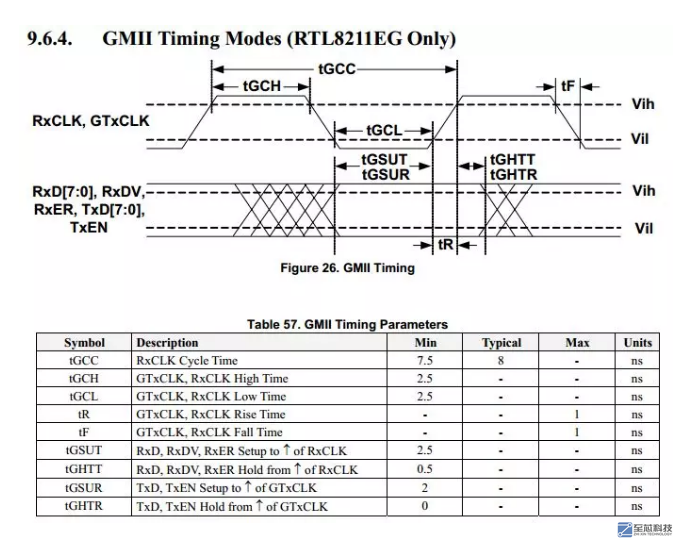

在百兆网模式下,其RXCLK的周期为40ns,也就是25M,数据端口RXD只用了4根线RXD[3:0],然后25M*4 = 100M,这样算出来,就是100M的速率了。接着再来说一下千兆网,千兆网的接口,就目前接触比较多的接口有3种,GMII,RGMII和SGMII。先说GMII,RxClk的周期为8ns,也就是125M,数据端口使用了8bit,125M*8 = 1000M,速率就是千兆网了。

还有RGMII,其时钟频率也为125M,但是它只使用了4个线,不过,RGMII使用的是双沿模式,也就是DDR模式,在时钟的上下沿都可以传送数据。这样算的话,125M*4*2 = 1000M,还是千兆网。RGMII与GMII主要的区别就是双沿采样与单沿采样。

之后还有SGMII,全称为Serial Gigabit Media Independent Interface,也就是串行的以太网接口。RGMII,GMII还是MII,都是使用并行接口,而且还需要随路时钟,而SGMII只需要2组线,一组是发送,一组是接收,当然一组线由两根差分线组成。SGMII也是需要8/10B编码。这样在PCB布线时,就可以节省一些布线的空间。当然,对于FPGA来讲,也节省了FPGA的引脚资源。SGMII一般在公司的项目会用的多一些,像GMII,RGMI在某宝上卖的开发板上一般都有。

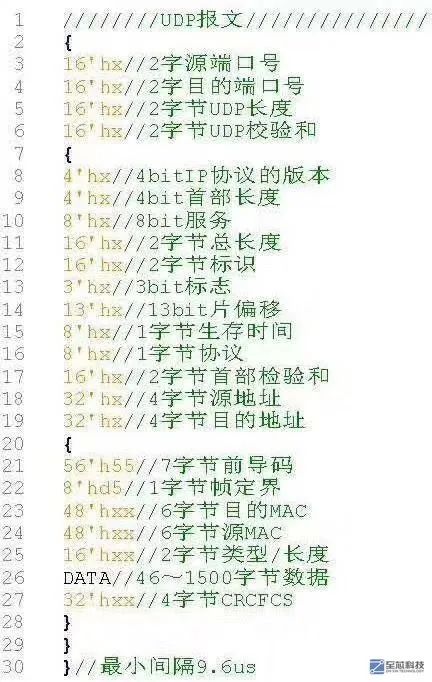

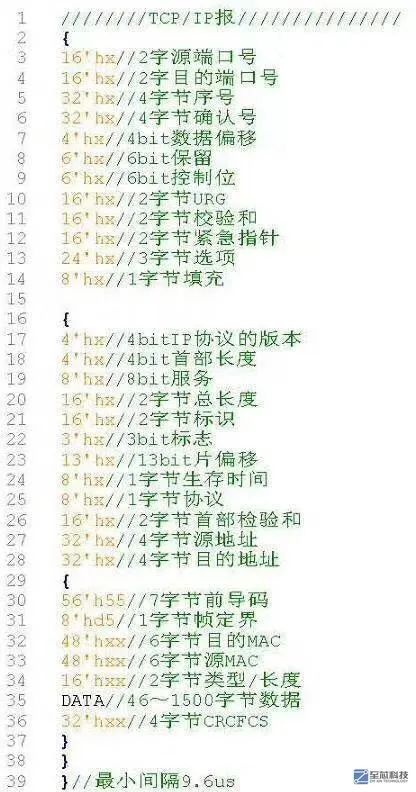

下面就简单的说说以太网数据格式,IEEE.802.3数据格式汇总,帧间隙IFG>=96bittime,10zM/100M/1000M格式一样。如下图简单的端口信号显示截图。

编辑:黄飞

-

CANopen以太网网关怎么用?2024-02-02 4543

-

以太网就是宽带连接吗?以太网口是网线接口吗?2023-08-31 17365

-

以太网口保护方案2023-07-18 2468

-

以太网网口与FPGA是如何连接的2023-06-15 1805

-

以太网网口与FPGA连接的常用方案2023-03-16 3952

-

如何用一台plc物联网网关连接多台以太网PLC?2023-02-02 1989

-

RS485以太网网关2022-08-17 1597

-

请问CH32V307V-R1运行RTT网络例程时以太网网口灯不亮如何处理?2022-05-10 5819

-

以太网网口自协商功能现象2021-12-29 12602

-

采用SAM4S如何参考设计的UART到以太网网关2020-05-20 2254

-

以太网网关目前的趋势2018-03-28 5338

-

BLADE和Voltaire推出高密度10Gb以太网网络方案2010-04-23 1683

-

连接PC与PLC的紧凑型以太网网关2009-04-08 379

-

以太网口的浪涌保护电路2008-10-27 8490

全部0条评论

快来发表一下你的评论吧 !