电容并联后阻抗与频率之间的关系

描述

单电容在电子电路中滤除高频干扰信号往往达不到很好的效果,通常可以通过多个电容并联来解决这一问题。

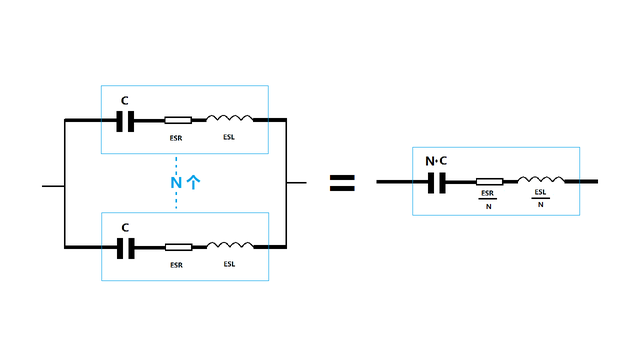

相同电容并联

N个相同电容并联,并联后ESR为原来的1/N,ESL也为原来的1/N,容值为原来的N倍。

相同电容并联后的等效电容

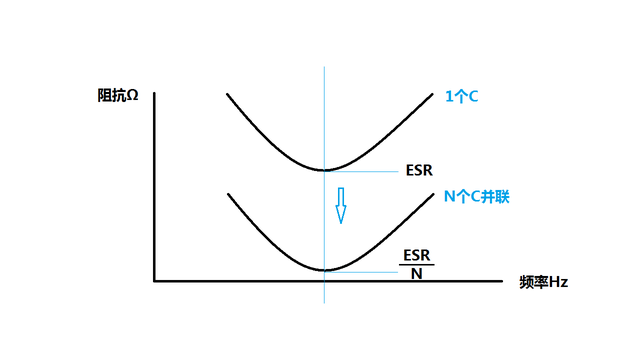

阻抗频率曲线为:

相同电容并联后的频率曲线

多个相同的电容并联后,阻抗频率曲线的整体形状不变,但是各个频率点的阻抗整体下移。

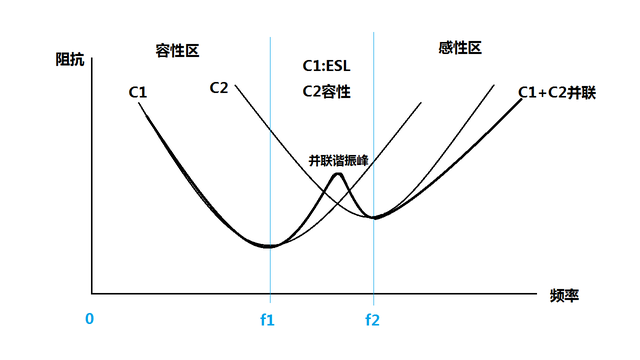

不同电容并联(ESR都较小)

由于每个电容的自谐振频率点不同,两个电容的行为特征存在差异。 并联后阻抗频率曲线如下。

不同电容并联

在0—f1,两个电容都表现为容性,总阻抗曲线会保持原来的变化趋势。

在>f2,两个电容都表现为感性,总阻抗会比任意一个电容的稍小。

在f1—f2,就像是一个电感和一个电容并联,构成了LC并联谐振电路,会在某个频率点发生并联谐振,阻抗达到区间内最大值,我们称之为并联谐振峰

(位于两条阻抗曲线交叉点附近)。 并联谐振峰也叫作反谐振点,可以理解为是由C1的ESL1和C2形成的。

并联谐振峰处阻抗较大,会影响并联后的滤波效果,那么哪些因素会影响谐振峰值的大小。

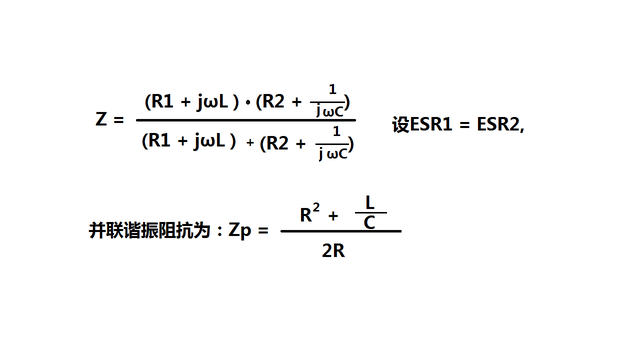

在此,两个电容并联可以等效为:

f1f2之间电容并联等效

则并联谐振峰公式为:

并联谐振峰计算公式

根据公式可得出以下三个结论:

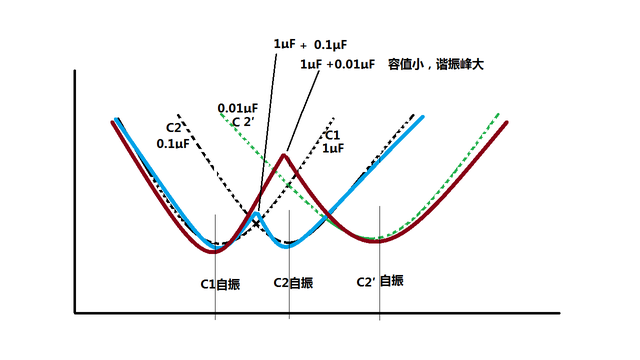

两电容容值差越大,谐振峰越大

当ESR、ESL(分别代入公式中的R、L)一定时,C2容值越小(在图上表现为两电容的距离越小容差越小)并联谐振阻抗(并联谐振峰)越小。

容差不同电容并联

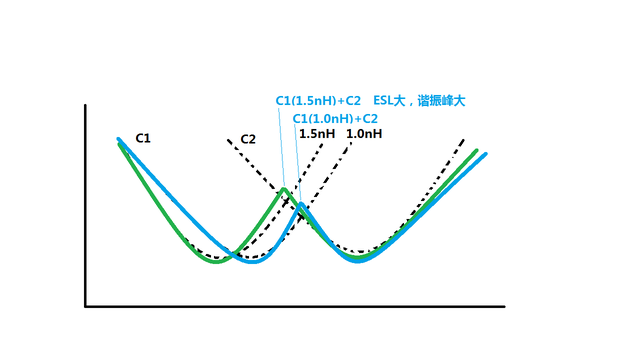

等效串联电感(ESL)越大,谐振峰越大。

当ESR、C2(分别代入公式中的R、C)一定时,ESL1越大并联谐振阻抗(并联谐振峰)越大。

ESL大小对谐振峰的影响

ESL不仅影响电容并联谐振峰值的大小,也影响电容的自谐振频率,ESL变大,使阻抗在自谐振频率点之后增加变快。

ESL越大,并联谐振峰值越大,而且并联谐振频率越低。 一方面,由于并联谐振峰值增大,要想满足目标阻抗的要求,需要增加更多的电容; 另一方面,由于谐振点向低频移动,为了高频处也能满足目标阻抗的要求,需要增加更多的小电容。

通常电容安装电感会影响ESL变大,所以需要通过一些方法来预防,比如体积大的电容用多个过孔并联,使电源过孔和地过孔尽量靠近,电容尽量靠近芯片的供电引脚减小平面的分布电感等。

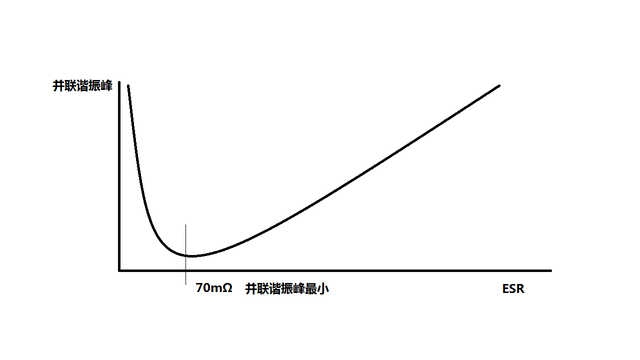

等效串联电阻ESR不宜过大或过小

假设ESL1=0.5nH、C2=0.1uF时,并联谐振峰值Zp与ESR的关系为:

并联谐振峰与ESR

并联谐振峰曲线是一个中间低两头高的形状,所以总有一个中间的ESR值使得并联谐振峰达到最小值,大于或小于此中间值都会使并联谐振峰变大。

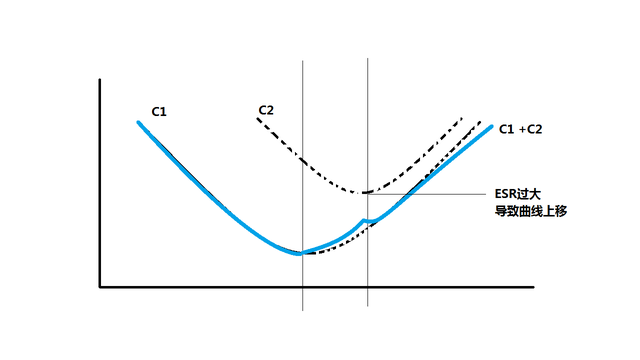

不同电容并联(其中有一个电容ESR过大)

当C2 ESR过大时,阻抗特性曲线可能会落如C1中,此时并不能达到展宽低阻抗频带的目的,电容并联后的曲线与C1的曲线差别不大。

ESR过大并联无效

如果C2为MLCC,ESR会受体积的影响,比如可以将0.01μF 0603更改为0.01μF0402的封装,或者更换更小ESR的电容,便可让曲线不落入C1中。

-

交流电路中电容和阻抗之间的关系,如何计算电容器的阻抗?2023-07-05 35168

-

电阻-电抗-阻抗-电导-电纳-导纳之间的关系2025-03-12 1002

-

【电源设计小技巧】3.并联阻抗和串联阻抗转换2011-12-19 13911

-

请问:LC并联、串联总阻抗与频率的关系2015-10-20 19040

-

晶振、电容和电阻之间的关系?2017-04-13 3647

-

石英晶体的等效模型是什么?石英晶体阻抗与频率之间有什么关系?2023-02-20 8400

-

损耗与频率之间的关系2009-10-22 9838

-

电解电容并联的效果2017-10-28 34706

-

分立器件等效模型 电阻阻抗绝对值与频率的关系2018-04-02 9315

-

串联谐振和并联谐振之间的区别2021-08-20 44674

-

天线阻抗与频率的关系解析2023-06-08 6411

-

太阳诱电 | 电容器阻抗的频率特性是什么?什么是电容器的ESR,ESL?2023-10-20 1843

-

并联电路中总电阻与分电阻的关系 并联电路电流分配规律2024-01-11 17012

-

电容电感并联阻抗的计算方法2024-07-17 15299

-

电容电感的阻抗与频率的关系2024-08-25 10487

全部0条评论

快来发表一下你的评论吧 !