为何要组合使用低通滤波器和模数转换器驱动器?

描述

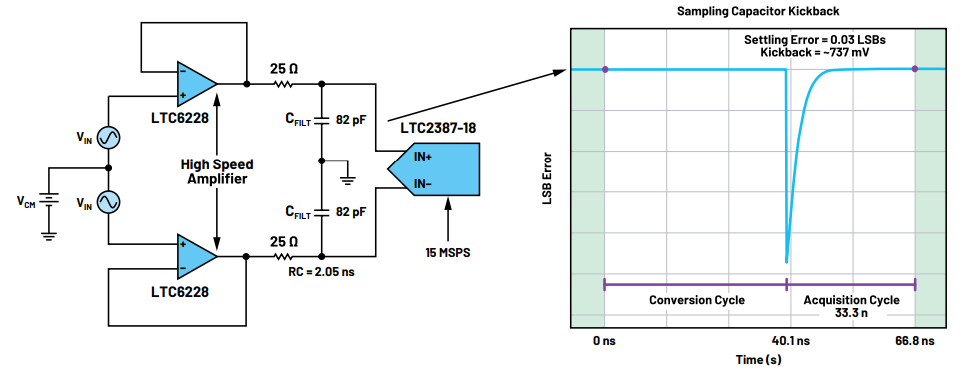

通过驱动ADC实现优化的混合信号性能,这是一大设计挑战。图1所示为标准的驱动器ADC电路。在ADC采集期间,采样电容将反冲RC滤波器中指数衰减的电压和电流。混合信号ADC驱动器电路的最佳性能受到多个变量影响。驱动器的建立时间、RC滤波器的时间常数、驱动阻抗,以及ADC采样电容的反冲电流在采样时间内相互作用,导致产生采样误差。采样误差随着ADC位数、输入频率和采样频率的增大而增大。

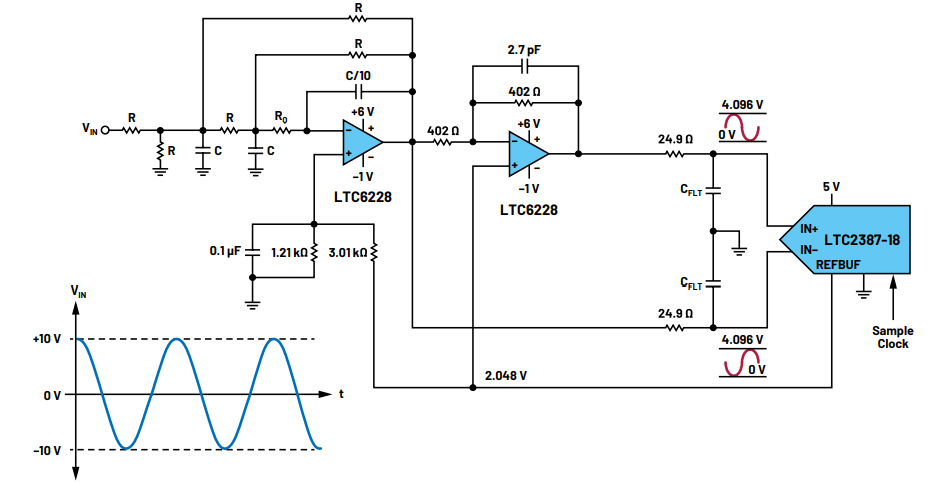

标准ADC驱动器具有大量实验数据样本,可用于可靠的设计流程。但缺乏实验数据来引导进行驱动ADC的低通滤波器设计。本文介绍集成模拟低通滤波、信号压缩和ADC驱动器的LPF驱动器电路(参见图2)。表1列出了图2所示电路的性能变量。下方的实验室数据和分析旨在引导说明,给出图2所示的电路的时间和频率响应限值。

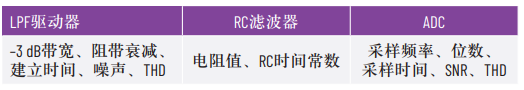

表1.图2所示电路的性能变量

实验室数据和分析

信噪比(SNR)和总谐波失真(THD)是衡量系统动态性能的两个重要参数。能否实现最佳性能,取决于ADC和信号调理级的组合,在本文中,后者包括三阶低通滤波器和单端至差分转换器。图2所示的LPF驱动器电路的–3dB带宽和建立时间会有所不同,有关SNR和THD的测量值,请参见表2至表5。本文将会探讨受测变量和这些变量对系统性能的影响。

1 低通滤波器–3dB带宽

比较信号带宽为1MHz与2MHz和0.5MHz时系统的性能。当–3dB点分别为558kHz、1MHz、和2.3MHz,其性能如表2所示。将截止频率降低至558kHz,LPF噪声带宽随之降低,但SNR提高。将截止频率增大至1MHz或2.3MHz,LPF驱动器建立时间缩短,THD降低。

图1.标准ADC驱动器和RC滤波器。

图2.LPF驱动器和ADC电路。

表2.R=750Ω时三种截止频率对应的LPF驱动器性能

更改图2所示的R或C可以更改截止频率。使用C电容来设置截止频率时,LPF驱动器THD更低;R电阻值降低,有助于略微改善SNR;如表3所示。

表3.R=412Ω时三种截止频率对应的LPF驱动器性能

2 设置RQ电阻(图2)

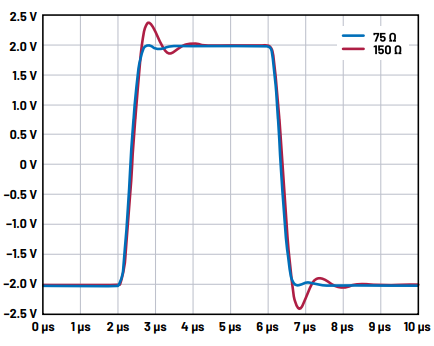

LPF的RQ电阻可设置时间响应。RQ越高,过冲越大,建立时间越长。RQ越低,过冲越小,建立时间越短。图3显示使用150Ω和75ΩRQ电阻时对应的LPF瞬态响应。我们测试了使用不同的RQ时LPF驱动器的性能,测试结果如表4所示。

图3.不同的RQ值对应的过冲和建立时间。

表4.不同的RQ值对应的LPF驱动器性能

根据实际测量得出的数据,使用75Ω和150ΩRQ对SNR和THD性能没有明显影响,只是影响过冲和建立时间的一个因素。

3 ADC采样速率

表5中的数据显示,如果使用LTC2387-18,在10MSPS时系统的THD性能低于15MSPS时(在10MSPS时,图2中的RC驱动器电容C3和C4的值为180pF)。

注:在10MSPS时,LTC2387-18和LTC2386-18的采样时间分别为61ns和50ns。

表5.采样速率为10MSPS和15MSPS时的LPF驱动器性能

4 RC滤波器

驱动器和ADC之间的RC滤波器用于限制带宽,确保实现宽带宽低噪声,且实现更优的信噪比。RC数值决定–3dB截止频率。降低R有时可能导致响铃振荡和不稳定。增大R会增大采样误差。使用更低的C值,会导致更高的电荷反冲,但充电时间更快。使用更高的C值,可以降低电荷反冲,但充电时间会变慢。此外,设置RC值是确保在给定的采样时间内获取稳定样本的关键。使用数据手册的推荐值和精密ADC驱动器工具给出的建议值会是一个非常不错的起点。

精密ADC驱动器工具是一款综合工具,可以帮助预测在驱动器和ADC之间使用不同的RC值系统的性能。可以使用这款工具检查的参数包括电荷反冲、采样误差和采样时间。

使用25Ω和180pFRC实现更低的–3dB截止频率时,输入信号建立时间和电荷反冲会受到影响。要实现更低的–3dB截止频率,并确保输入信号在采集时间内正确建立,我们可能需要使用更低的采样速率。根据LTC2387-18数据手册,采样时间通常是周期时间减去39ns。在15MSPS使用LTC2387-18时,采样时间为27.67ns,在10MSPS使用此器件时,采样时间为61ns。

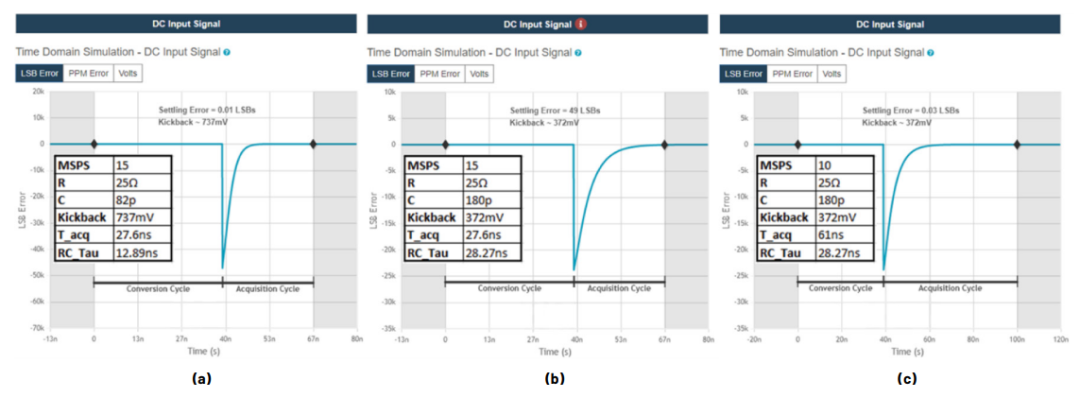

图4.使用不同采样速率时的电荷反冲、RC_Tau、采样时间:(a)15MSPS采样速率,LTC2387-18使用建议的RC值(25Ω和82pF),(b)15MSPS采样速率,LTC2386-18使用建议的RC值(25Ω和180pF),(c)10MSPS采样速率,LTC2386-18使用建议的RC值(25Ω和180pF)。

借助精密ADC驱动器工具,图4a至4c汇总列出了使用不同的RC值时对应的反冲差值和RC时间常数(Tau),以及采样速率为10MSPS和15MSPS时的采样时间。图4a显示LTC2387-18在15MSPS采样速率下,使用推荐RC值(25Ω和82pF)时的建立响应。图4b显示在C为180pF时,得出的RC时间常数更高,这导致在15MSPS采样速率、27.6ns采样时间内输入信号无法建立。图4c使用与图4b相同的RC值(25Ω和180pF),但在使用10MSPS采样速率、采样时间增加至61ns之后,信号能够建立。

5 LPF驱动器电阻选择

可以通过更改R或C来实现LPF驱动器的–3dB截止频率。电阻噪声是系统总噪声的组成部分。根据噪声计算公式,从理论上来说,降低电阻值可以降低电阻噪声。为了进行验证,我们尝试了两个不同的电阻值作为LPF驱动器R,分别是750Ω和412Ω。从理论来说,R更低时得出的SNR应该更佳,但从实际获得的数据来看,如表2和表3所示,SNR并无很大改善,相反,这会对THD性能产生更大影响。

LPF电阻(图1中的R)越低,放大器所需的电流越大。使用更低的电阻值时,运算放大器的输出电流高于最大线性驱动电流。

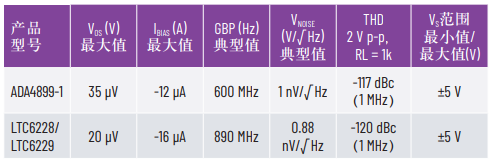

6 放大器驱动器选择

在选择要使用的ADC驱动器时,实现器件最佳性能所对应的规格至关重要。我们使用两个ADC驱动器来收集数据,分别是ADA4899-1和LTC6228。这些ADC驱动器非常适合用于驱动LTC2387-18,后者用于进行实验室测量。在选择ADC驱动器时考虑的一些规格包括带宽、电压噪声、谐波失真和电流驱动能力。根据已完成的测试,从THD和SNR这两个方面来看,ADA4899-1和LTC6228的性能差异可以忽略。

LPF设计和应用指南

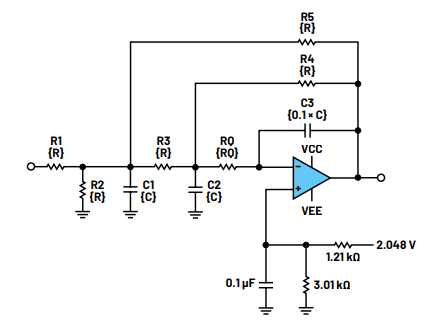

图5显示LPF电路。5个相同电阻(R1至R5)、1个用于调节LPF时间响应的电阻(RQ)、2个相同的接地电容(C1和C2),以及1个数值为接地电容1/10的反馈电容(C3),这些器件构成了LPF无源组件(±1%电阻和±5%电容)。

图5.LPF电路。

简单的LPF设计流程(注1)

R1至R5=R,C1和C2=C。

要尽量降低失真,电阻R1至R5的值必须在600Ω至750Ω范围内。

-

设置R=750Ω

-

C=1.5E9/f3dB(最接近标准的5%电容pF),f3dB为LPF–3dB频率(注2)

-

例如:如果f3dB为1MHz,那么C=(1.5E9)/(1E6)=1500pF

-

C3=C/10

-

RQ=R/5或R/10(注3和4)

注1.简单的滤波器设计只需要一个计算器,无需使用非线性s域公式。

注2.如果R=619Ω,那么C=1.8E9/f3dB,f3dB为LPF–3dB频率。

注3.RQ=R/5,用于实现最大阻带衰减,RQ=R/10,用于实现低过冲和快速建立时间。采用RQ/5和RQ/10时,在10×f–3dB时,阻带衰减分别为–70dB和–62dB。

注4.如果RQ=R/10,–3dB频率比RQ=R/5时低7%,也就是说,R1至R5等于RQ/5时R的0.93。

注5.LPF驱动器差分输出至ADC输入的PCB线路距离为1''或更低。

注6.LPF运算放大器的VCC和VEE分别为6V和–1V,输出线性电压摆幅为0V至4.098V。

结论

根据表2至表5的SNR和THD数据,我们可以了解图2所示电路的性能。通过增大电容来降低LPF带宽,这会增大SNR(降低LPF噪声带宽)。LPF带宽越低,失真程度越高(因为LPF建立时间比实现最低采样误差所需的时间长)。此外,如果LPF电阻值太低,THD会随之降低,因为LPF运算放大器需要驱动反馈电阻和反相运算放大器输入电阻(运算放大器输出电流更高时,失真程度降低)。

LTC2387-18ADC采用10MSPS采样频率时,LPF通带必须为1MHz或高于1MHz,以尽可能降低THD。将LPF设置为1MHz,是对SNR、THD和足量ADC混叠抑制的任意妥协。

设计参考:ADI的精密ADC驱动器工具

精选器件_运算放大器

精选器件_模数转换器

原文标题:为何要组合使用低通滤波器和模数转换器驱动器?

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 亚德诺

-

精密SAR模数转换器的前端放大器和RC滤波器的设计2023-11-24 635

-

如何组合使用低通滤波器和ADC驱动器获取20 V p-p信号2023-04-23 992

-

Δ-Σ模数转换器数字滤波器类型:正弦滤波器2023-04-13 2199

-

高通滤波器和低通滤波器的关系2023-02-17 6058

-

正弦滤波器到底为何物2022-01-26 3116

-

如何设计一个带宽150 kHz、16 bit∑-△模数转换器中的降采样滤波器?2021-04-12 1840

-

LTC1564滤波器驱动LTC1608 16位500ksps模数转换器2020-03-09 2151

-

AD9288BSTZ-100模数转换器2018-11-06 1525

-

AD9276BSVZ模数转换器2018-10-26 1406

-

讲述Δ-Σ模数转换器数字滤波器最常用的正弦滤波器2018-08-30 6873

-

Σ-Δ模数转换器 数字滤波器类型2017-04-17 797

-

精密SAR模数转换器的前端放大器和RC滤波器设计2016-01-07 1231

全部0条评论

快来发表一下你的评论吧 !