如何降低形式验证的复杂度?

描述

当计数器和内存处于我们所需要证明断言的逻辑锥中,它们可能是Formal无法完成证明的根本原因。

因为形式分析算法很难适应非常大的状态空间,而计数器和存储器都会引入很多的状态空间和时序深度。针对这个问题,我们可以在不影响验证完备性的条件下减小计数器和存储器的大小或者用抽象模型替换。

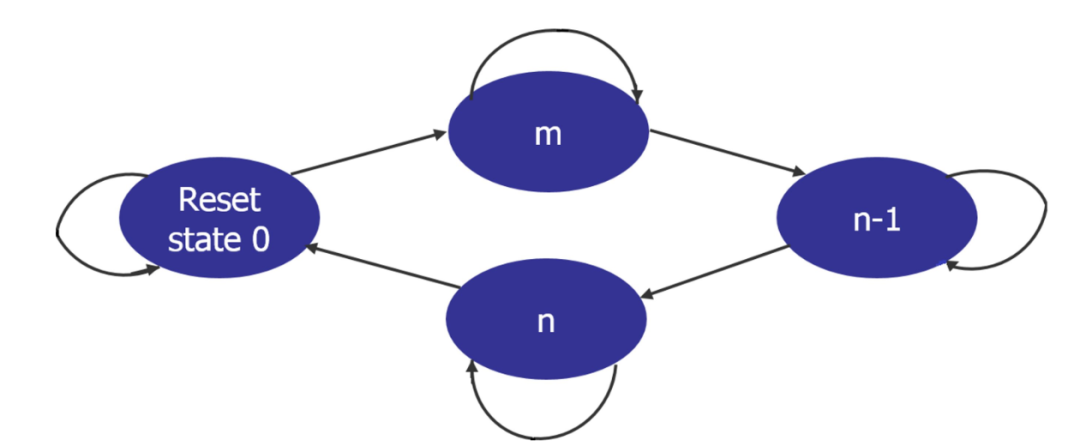

Formal验证中优化大计数器的一种流行且有效的方法是将它们替换为小型的状态机模型(状态空间小),该模型仅考虑会触发设计操作的计数器临界值。例如,假设计数器的值“m”、“n-1”和“n”很关键。考虑以下状态机作为替代:

为了用这个抽象模型替换原始计数器,我们首先绕过真实设计的驱动逻辑(用cutpoint的方式“切割”原始计数器输出信号,使其变成一个自由随机变量,然后向其添加约束)

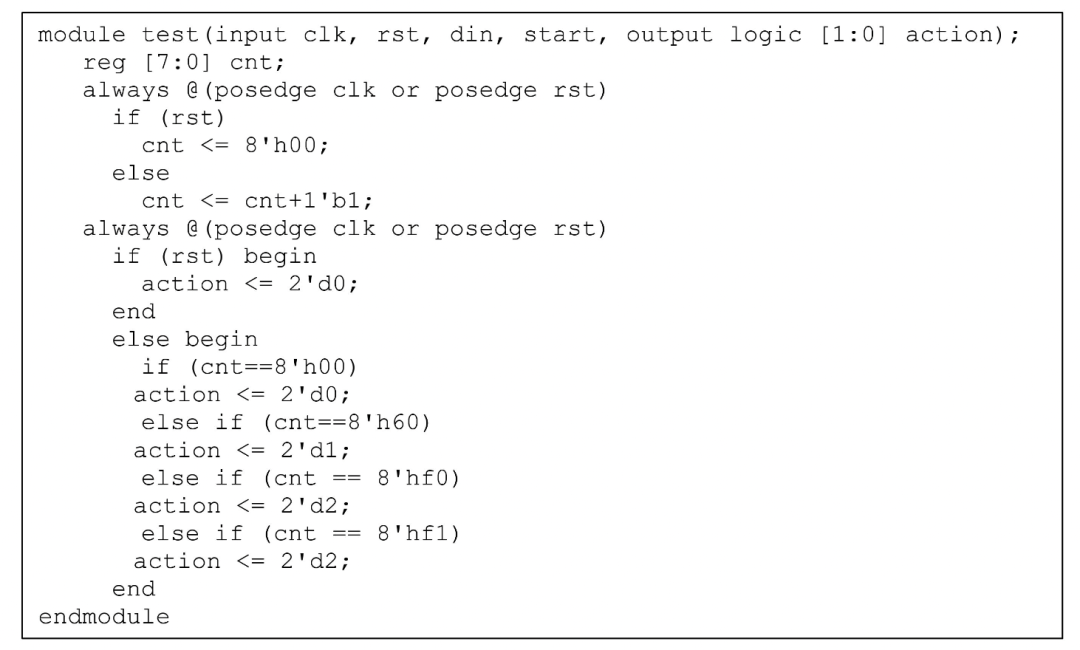

下面是一个计数器示例

这种办法主要还是用于bug-hunting,而且如果RTL中的其他部分实际就需要计数器延迟特定周期,那么这个优化方法就不适用了,所以说此时就没法用作formal full prove。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB与PCBA工艺复杂度的量化评估与应用初探!2024-06-14 11580

-

基于纹理复杂度的快速帧内预测算法2010-05-06 3735

-

JEM软件复杂度的增加情况2019-07-19 2089

-

如何降低LMS算法的计算复杂度,加快程序在DSP上运行的速度,实现DSP?2021-04-12 2755

-

时间复杂度是指什么2021-07-22 1889

-

降低高条件数信道下的球形译码算法复杂度的方法2009-11-21 651

-

图像复杂度对信息隐藏性能影响分析2017-11-14 1075

-

商汤联合提出基于FPGA的Winograd算法:改善FPGA上的CNN性能 降低算法复杂度2018-02-07 10456

-

深度剖析时间复杂度2022-03-18 2732

-

如何求递归算法的时间复杂度2022-07-13 2326

-

算法之空间复杂度2022-08-31 2583

-

可以通过降低约束的复杂度来优化Formal的执行效率吗?2023-02-15 1625

-

如何计算时间复杂度2023-10-13 5117

-

如何降低SigmaDSP音频系统复杂度的情形2023-11-29 491

-

降低Transformer复杂度O(N^2)的方法汇总2023-12-04 2982

全部0条评论

快来发表一下你的评论吧 !