AN-2003: ADI公司AD7380系列SAR ADC的片内过采样

描述

Jonathan Colao

本应用笔记讨论了逐次逼近寄存器(SAR)、模数转换器(ADC)中的片内过采样。两种常见的过采样技术是正态平均值和滚动平均值。这些技术在AD7380/AD7381及其高吞吐速率SAR ADC系列中执行,因此可以直接获得平均转换数据,从而减轻数字控制器的负担,这是数据采集系统的优势。

在精密数据采集系统中,信噪比(SNR)和有效位数(ENOB)越高,系统在存在宽带噪声的情况下测量信号功率的能力就越好。

噪声会降低系统性能。降低噪声的一些方法是用更高分辨率的ADC(如Σ-Δ ADC或SAR ADC)代替系统,或者过采样并使用数字滤波技术。

过采样技术在Σ-Δ型ADC架构设计中有着悠久的历史。Σ-Δ型ADC由Σ调制器和后续数字信号处理模块或数字滤波器构成。Σ调制器可以小到一位量化器,以收集数千个样本,然后抽取这些样本以实现高分辨率转换结果。平均样本越多,可实现的分辨率就越高,从而使转换更接近采样值。一些常见的Σ-Δ应用是温度监控和电子秤测量系统。

Σ-Δ型ADC架构依赖于以远高于目标带宽的速率对较小的电荷进行采样。采集更多样本,但咬合量较小。典型Σ-Δ型ADC的过采样范围在目标信号的32×至1000×之间。过采样与噪声整形(调制方案)相结合的结果将带内噪声移出目标带宽。噪声移动到更高的带宽,然后以数字方式滤除。结果是目标带宽的噪声更低,分辨率更高。Σ-Δ ADC的每个转换结果都是由于采样事件更小但更频繁。

SAR ADC使用逐次逼近来确定结果。SAR ADC采用循序渐进的方法来确定单个采样时刻的数字表示的每个位。SAR采用电荷再分配电容器和数模转换器(DAC)阵列。将采样数据与每个二进制加权电容阵列进行比较。二进制加权电容的总数决定了SAR ADC的位数或分辨率。转换过程由高速内部时钟和电容式DAC阵列控制,电容式DAC阵列能够快速转换变化的信号。SAR ADC用于需要宽带宽的数据采集系统。

SAR ADC通常会及时转换单个实例,提供与特定时间时刻相关的数字答案。随着更快的SAR转换器的出现,过采样的使用越来越多,以提高目标关键带宽的分辨率。目前,SAR ADC通常使用过采样技术,该技术通过微控制器或现场可编程门阵列(FPGA)上的后处理来执行。ADI公司为其SAR ADC系列提供内置的过采样功能。这种过采样特性提高了噪声性能,简化了接口要求,并允许用户开箱即用,而无需对FPGA或微控制器进行设计和资源密集型平均。过采样功能还可以以可管理的数据速率最大限度地提高数据处理性能。

| 输入类型 | 16 位 | 14 位 | 12 位 |

|

差分 单端 |

AD7380 AD7386 |

AD7381 AD7387 |

AD7388 |

过采样

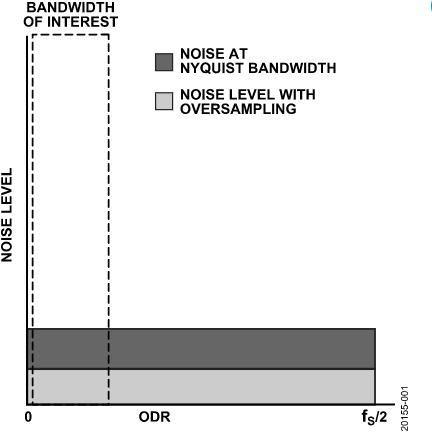

在模数转换期间,模拟信号由ADC数字化。过采样是一种技术,用于通过对模拟信号进行采样,并以比非过采样解决方案高得多的速率对该信号进行数字转换来提高有效的数字化信号分辨率。过采样允许用户在更宽的带宽上平均转换器的噪声。当平均和/或滤波到特定带宽时,每过采样2×噪声就会以√3或2 dB的速率改善,前提是噪声不相关,宽带(白)噪声和零(0)均值。其他频谱成分(如相关噪声或谐波)不会通过平均来减少。图1显示了ADC(深灰色)的噪声电平,该噪声来自分布在奈奎斯特带宽上的量化噪声、热噪声和外部噪声(如驱动器、时钟和基准电压源)的组合源。

图1.平均滤波噪声

根据奈奎斯特理论(f采样≥ (2 × F在)),输入信号必须以至少两倍于最大目标频率的速率进行采样,以便准确重建信号,并且存在发生过采样的相同标准。过采样降低了信号噪声,从而增加了系统SNR,从而提高了分辨率(假设没有明显的失真成分)。

过采样是一种数字信号处理技术,其中收集多个样本,然后取平均值。数据样本平均的作用类似于低通滤波器。

ADI公司的AD7380系列是同步采样SAR ADC系列,能够进行片内过采样。该SAR ADC系列可以执行两种过采样技术:正常平均值和滚动平均值。

正常平均过采样

在正态平均过采样中,平均算法实现为一个简单的平均值,将 M 个样本相加,然后将结果和除以相同的 M 因子。在这种方法中,为每个平均结果收集一组新的 M 样本。

表 2 显示了该算法工作原理的一般表示形式。在此示例中,数据有 12 个样本。当 M = 2 时,平均样本数为 1,导致每两个样本产生一个新输出,因此有效采样率的一半。结果是样本 2 和样本 3、样本 4 和样本 <> 的平均值,依此类推。

| 样品编号 | 示例结果 | 平均结果 | |

| M = 2 | M = 4 | ||

| 1 | 0.200 | 0.2500 | 0.2400 |

| 2 | 0.300 | ||

| 3 | 0.230 | 0.2350 | |

| 4 | 0.240 | ||

| 5 | 0.260 | 0.2300 | 0.2500 |

| 6 | 0.200 | ||

| 7 | 0.240 | 0.2700 | |

| 8 | 0.300 | ||

| 9 | 0.270 | 0.2600 | 0.2450 |

| 10 | 0.240 | ||

| 11 | 0.250 | 0.2300 | |

| 12 | 0.210 | ||

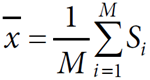

同样,应用M = 4的平均因子,对第一组四个样本进行平均,然后对另一组四个样本(样本5到样本8)进行平均。简化的正态平均方程如下:

其中:

x 是 M 个样本的平均值。

M 是要取平均值的样本数。

Si是第 n 个采样值。

在AD7380 SAR ADC系列中,芯片内实现正常平均过采样,最多可收集32个平均采样。只要启用此技术,AD7380就会自动收集M个转换样本,然后输出平均转换结果。转换结果的可用性取决于收集的M个样本数,该数量由AD1系列CONFIGURATION7380寄存器中OSR位的过采样比决定。M 示例转换完成后读取结果。

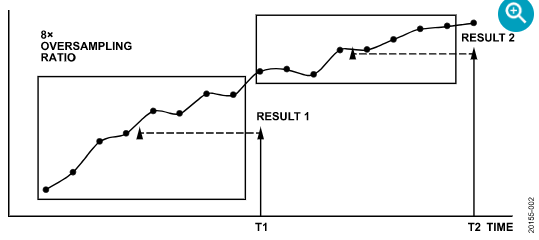

图2显示了AD7380如何执行该算法。在此示例中,假设 M = 8 或过采样比 (OSR) 为 8,从而收集和平均 7380 个样本。当转换在内部启动时,AD2会执行一系列转换和采集过程,直到完成请求的采样数(M)。然后,对捕获的数据执行平均过程。因此,引入了一些处理延迟,如图1所示,在T2时,平均结果可用,并在SDOx引脚上时钟输出。此时,启动新的平均运算,导致新的转换突发以获取下一个 M 个样本。图<>显示,应用该技术可降低取样系统的有效ODR。ODR 的降低与样本计数 (M) 或 OSR 的增加成反比。对于需要最佳性能但ODR速度较慢的应用,建议使用正态平均过采样方法。

图2.正常平均过采样操作

滚动平均过采样

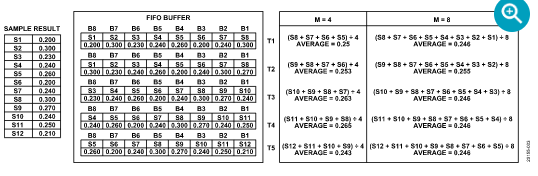

滚动平均过采样技术使用缓冲区来存储平均过程的样本。滚动平均算法选择存储在缓冲区中的最新 M 个样本,并将结果总和除以 M。在数字设计中,缓冲器需要额外的空间来创建额外的存储空间。在滚动平均过采样技术中,小型ADC的缓冲存储容量有限,并采用先进先出(FIFO)算法。当缓冲液已满且有新样本可用时,缓冲液中最早的数据将被丢弃,如图3所示。使用前面的示例采样数据,前八个样本结果填充 FIFO 缓冲区(S1 到 S8)。当新的样本数据 (S9) 可用时,S1 从缓冲区中掉落,S9 插入缓冲区。当新样品存储在缓冲液中时,相同的过程也会进行。

如前所述,滚动平均过采样技术将最新的 M 个样本相加,并通过除以 M 来计算结果平均值。在图 3 所示的示例中,M = 4,该算法将 FIFO 缓冲区中可用的四个样本 B1 相加到 B4,它们是最新的四个样本,然后除以 4。在下一个平均值期间,将平均相同的FIFO缓冲区位置,但这些缓冲区中的内容会发生变化。在 M = 8 的情况下,FIFO 缓冲区中的所有样本都包含在求和运算中,随后除以 8。

图3.滚动平均过采样缓冲区示例

要在AD7380系列中启用滚动平均过采样,请将OS_MODE位设置为逻辑1,并且CONFIGURATION1寄存器的OSR位中必须有一个有效的非零值,才能在FIFO缓冲器中存储多达8个样本。FIFO 缓冲区会在转换发生后立即更新。当滚动平均过采样启用时,其算法从FIFO缓冲区收集最新的M个样本数并除以M,其中M是OSR。然后,平均结果在AD7380的SDOx引脚上时钟输出。

图4显示,一旦缓冲器中的样本可用(在本例中为M = 8),过采样结果就可以在随后的转换周期中使用。因此,即使M(样本数量)增加,输出数据速率(ODR)也更快。滚动平均过采样技术在需要高ODR和高性能的应用中非常有用。此技术可实现的性能提升受到可用缓冲区存储的限制。简化的滚动平均方程如下:

其中:

x 是 M 个样本的平均值。

M 是要取平均值的样本数。

Bi是特定缓冲区位置的样本。

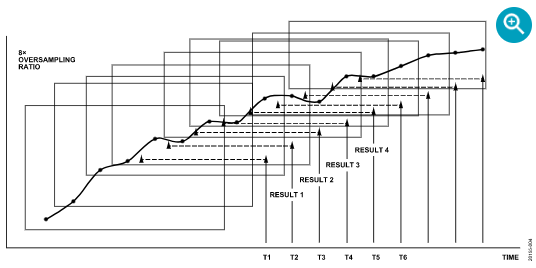

图4.滚动平均过采样操作

过采样优势

噪音改善

ADC可以通过过采样实现更高的动态范围。过采样的工作原理是假设噪声源不相关且均值为零,因为样本将白噪声视为整个频谱中均匀分布的噪声,或者以相邻代码为中心的高斯噪声分布视为可以通过平均来减少的信号。

图5是使用AD7380生成的快速傅里叶变换(FFT)曲线示例,无过采样,应用滚动平均过采样,OSR = 8。

图5.利用AD7380改善噪声

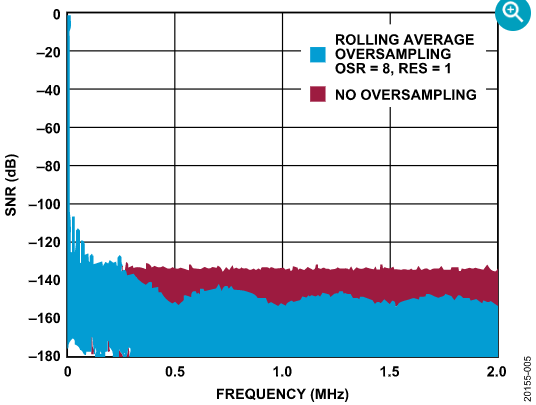

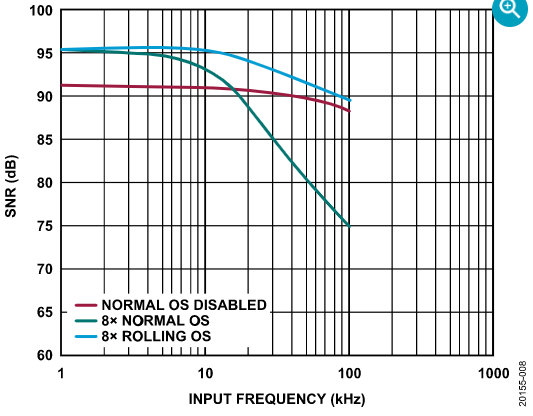

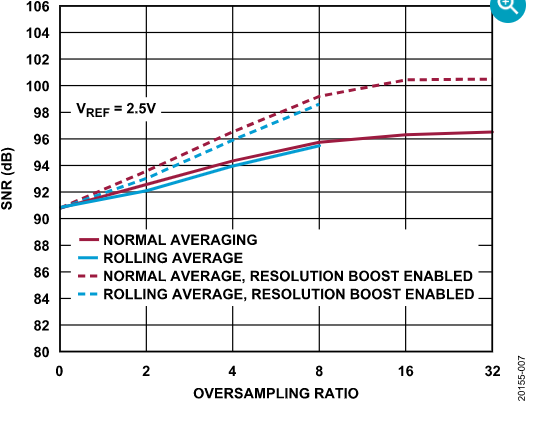

观察到本底噪声的显著改善,对应于SNR的增加(见图6)。在本例中,SNR分别提高到96 dB和95 dB,同时启用正常平均过采样和滚动平均过采样。

图6.AD7380 信噪比与过采样比

要估计应用过采样技术的SNR改进,请使用以下公式:

其中:

N 是 ADC 分辨率。

fs 是采样频率。

带宽是感兴趣的带宽。

10log(fs/(2 × BW)) 是过程增益。

fs/(2 × BW) 是采样比或奈奎斯特比。

请注意,包括过程增益是为了考虑采样超过2 × BW的额外过采样过程。在下式中,将采样频率增加系数k,其中k是平均采样数或过采样率,导致SNR增加。

理想情况下,将k的值加倍会导致SNR增加3 dB。

表3和表4详细介绍了不同过采样率下对SNR的典型正常和滚动平均过采样影响。随着过采样率的增加,信噪比也会增加。

| 过采样率 | 信噪比 (分贝) | 输出数据速率 (kSPS) | |

| 参考电压 (V裁判) = 2.5 V | V裁判= 3.3 V | ||

|

残疾人 2× 4× 8× 16× 32× |

90.8 92.6 94.3 95.8 96.3 96.5 |

92.5 94 95.4 96.3 96.8 97 |

4000 1500 750 375 187.5 93.75 |

| 过采样率 | 信噪比 (分贝) | 输出数据速率 (kSPS) |

|

残疾人 2× 4× 8× |

90.3 91.7 93.37 94.66 |

4000 4000 4000 4000 |

AD7380系列通用器件均提供这两种平均技术。每种技术都推荐用于一系列应用。但是,每种技术都有自己的属性,必须针对特定应用程序考虑这些属性。正态平均过采样技术提供以下功能:

最佳性能,因为此技术对其他数据进行采样以进行平均。

ODR 速度较慢,因为样本或 OSR 的数量增加,使应用程序能够使用较低的 SCLK 频率,从而降低总体成本。

信号带宽明显低于转换速率(见图7)。请注意,带宽限制归因于有效的低通滤波器。

图7.SNR 与输入频率的关系,过采样频率响应

滚动平均过采样技术提供以下功能:

采样速率可以变化,由应用通过CS引脚进行控制。

采样速率快,最大采样速率为 4 MSPS。

由于缓冲区约束,对平均 8 个样本数的限制。

更宽的信号带宽(见图7)。

提高分辨率 (N)

如前所述,两种过采样技术的性能都有显著提高。使用以下公式,SNR限制为ADC的N分辨率。

使用以下公式计算 N:

在给定理想的16位ADC的情况下计算SNR,最大SNR为98 dB。

最大SNR改进受ADC位数的限制,如图6所示,过采样比大于8时,SNR性能几乎没有提高。为了获得过采样的优势,必须提高N分辨率,这就是AD7380分辨率提升特性的重要性。

提升分辨率

即使存在限制,AD7380系列也可以通过过采样有效提高分辨率,从而扩展可实现的SNR。要启用片内升压分辨率,请写入 CONFIGRATION2 寄存器的 RES 位(位 1)。

要了解过采样如何提高SNR,请使用前面的公式计算17位ADC的SNR。结果是信噪比为104.1 dB。

将此值代入SNR方程,得到将分辨率提高1位所需的过采样因子k。

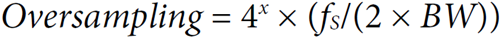

要将分辨率提高1位,ADC过采样比必须至少为4。提高分辨率所需的过采样因子总结为以下公式:

其中 x 是附加分辨率。

表5总结了不同过采样率的分辨率提高。

| 过采样率 | 位数增加 |

|

2× 4× 8× 16× 32× |

0.5 1 1.5 2 2.5 |

图8显示了使能分辨率提升时AD7380的SNR性能。SNR 性能超过 100 dB。额外的2位分辨率提升改善了量化噪声,并提高了SNR。分辨率提升是一种增加系统动态范围的方法,无需额外增加2位分辨率的更高成本。此功能的缺点是,它需要在串行端口接口(SPI)SCLK中额外增加2个时钟周期才能输出平均转换结果。

图8.SNR与过采样比,使能AD7380的分辨率提升

应用实例

光学编码器用于电机控制应用,以捕获准确的位置测量值。例如,编码器的正弦和余弦输出是插值的,必须同时捕获。对于此类应用,建议使用同步采样SAR ADC,例如高总速率AD7380。角位置θ(θ)由捕获的正弦和余弦信号的反正切获得。当这些信号理想时,结果是准确的。在实际应用中,这些信号会受到噪声的影响,从而导致读取错误。这些偏差会导致编码器角度位置的误差。

高编码器精度要求示例是当电机以较慢的速度运行时,即电机开始减速然后到达目标位置时。利用AD7380的片内过采样技术,可以对正弦和余弦信号进行数字滤波,从而实现高动态范围。增强的正弦和余弦转换可提高角度位置精度,这是应用中的要求,例如用于将微小组件安装到印刷电路板 (PCB) 中的拾取和放置机器或工业机械中的机械臂,用于将负载运输和移动到特定位置。

结论

过采样是一种数据处理技术,可在ADC上提供精密转换结果。SAR ADC历来通过微控制器、DSP或FPGA在后处理中采用这种技术。ADI公司的高速SAR ADC系列(如AD7380)已将此功能集成到两种片内过采样技术(正常和滚动平均)中。SDOx引脚可直接快速访问平均转换结果,从而产生明显的效果,这些效果立即体现在ADC参数中,例如SNR和完整的动态范围。

普通平均过采样技术适用于需要更高性能且可以接受较低时钟速度和输出数据速率的应用。滚动平均过采样技术适用于要求速度和性能的应用。

随着分辨率的提高,过采样性能得到进一步改善。请注意,结合所讨论的两种过采样技术,可以直接通过AD2系列中的分辨率提升功能增加额外的7380位分辨率。AD7380泛型器件是高速SAR ADC,可减轻微控制器上SPI的额外数据处理负担,AD7380系列器件具有高度可靠性,可提高ADC转换精度。

审核编辑:郭婷

-

AD7380 - 4 ADC:高性能模数转换器的全面解析2026-03-27 254

-

AD7380上电测量异常的原因是什么?2024-03-06 2606

-

AD7380 SPI读取都是0x0000的原因?2023-12-04 563

-

使用过采样增加SAR ADC的动态范围2023-01-08 4494

-

AD7380/AD7381:双同步采样、16位/14位、4 MSPS SAR ADC、差分输入数据表2021-05-23 1184

-

UG-1304:评估AD7380 16位和AD7381 14位、2通道、同步采样、逐次逼近ADC2021-03-22 1135

-

AD7380/AD7381: What oversampling method is best for an application?2021-02-02 1475

-

寄存器型模数转换器中的片内过采样2021-01-06 1808

-

ADI公司AD7380系列SAR ADC的片内过采样2020-11-11 2945

-

采用Δ-Σ和SAR ADC的过采样模式提升ADC动态范围2019-09-14 4825

-

AD7380模数转换器的性能及应用2019-06-14 9088

-

2812片内ADC采样时间计算2011-09-05 3929

全部0条评论

快来发表一下你的评论吧 !