解读ADC采样芯片(EV10AQ190A)的采样(工作)模式(双通道模式)

描述

工作模式有三种:分别为四通道模式、双通道模式以及单通道模式,这里先简单讲述双通道模式(由于工程中用过双通道模式);

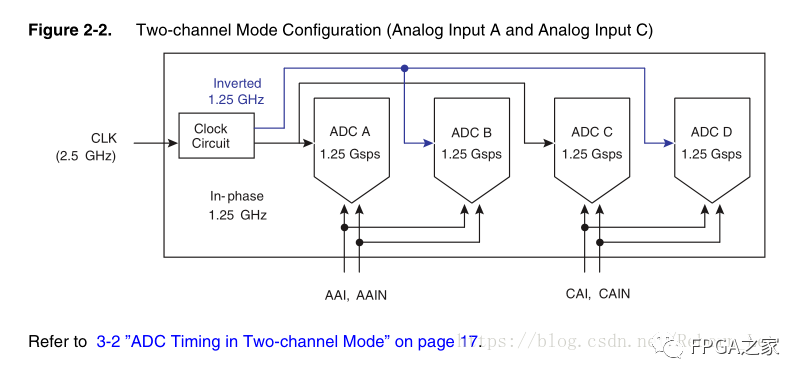

双通道模式组态:

从这张图中可以得到的信息是什么呢?

首先有两个模拟输入,分别为AAI,AAIN(这是一个模拟输入 Analog Input A)和CAI,CAIN(Analog Input C),根据实际工程需要,选择使用A输入端口,或者C输入端口,或者两个都用。

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态内部时钟电路(Clock Circuit)为ADC A通道提供内部采样时钟,该时钟反转180°为ADC B通道提供采样时钟。这两个时钟的关系是由同一个外部时钟源产生时钟,因此时钟频率一致,但是相位完全相反。

当外部信号从C输入端口输入时,分析方法一致。

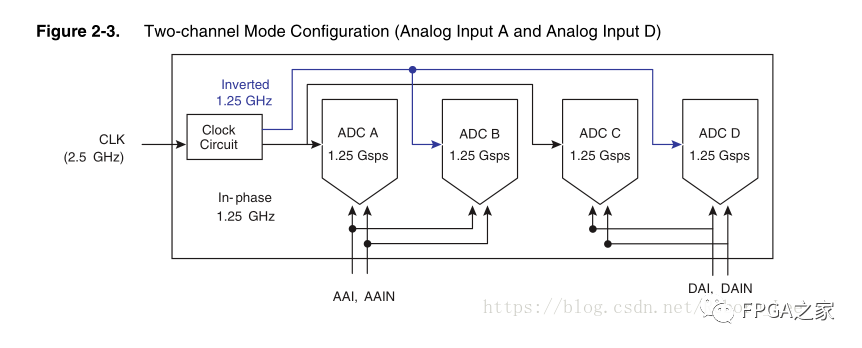

上图和图2-2是类似的,都是双通道模式的构造,不同的仅仅是模拟输入端口变成了A和D;

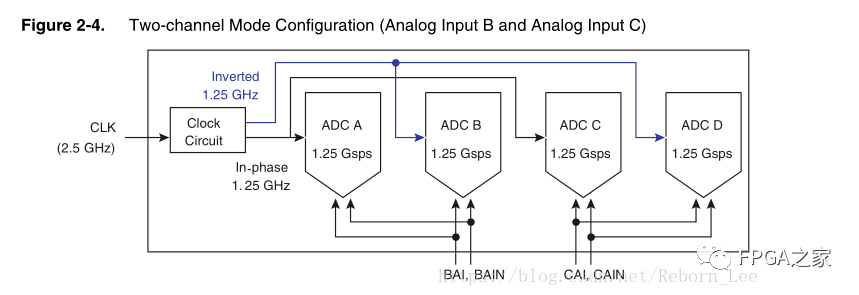

同理,见下图:

模拟输入端口分别为B和C;

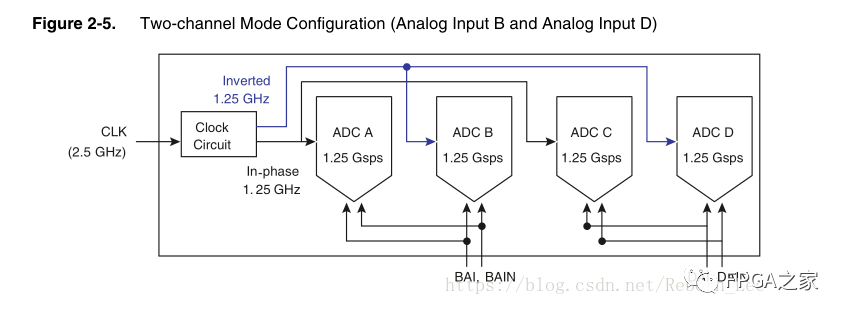

还有:

模拟输入端口为B和D;

好了,双通道模式框架就这些。

接下来的问题是信号是如何采样的?以及采样后的信号是如何同步的?

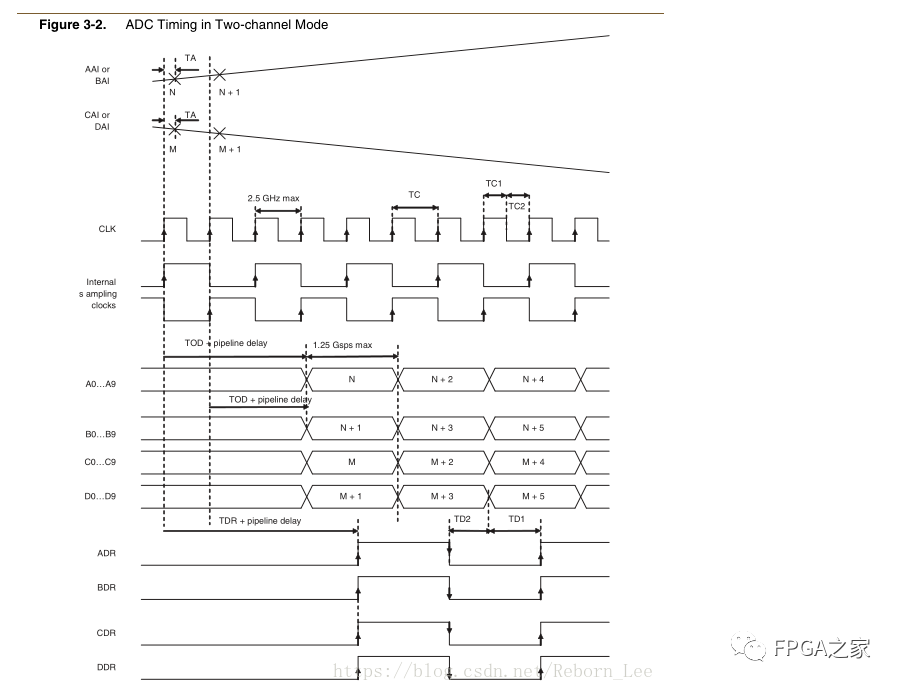

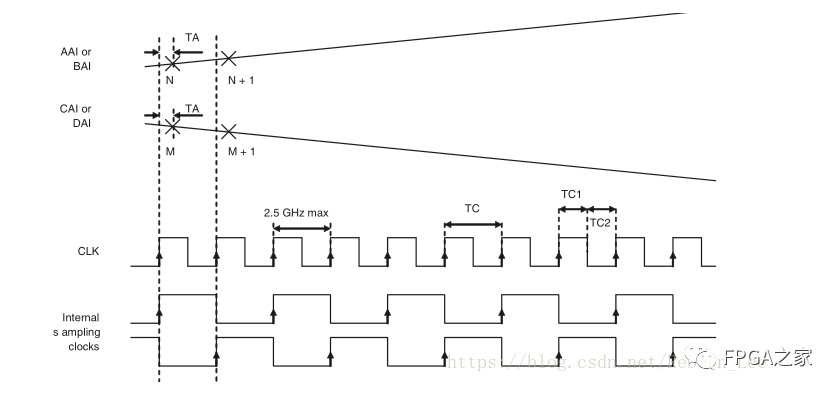

见下图:

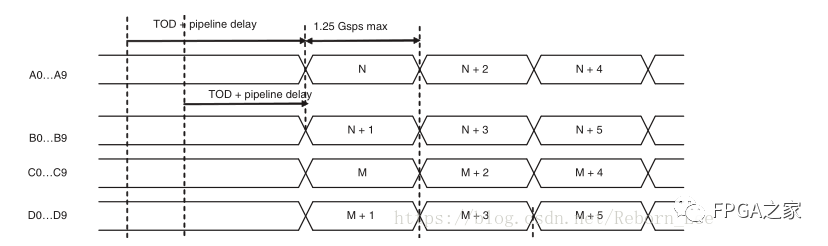

双通道模式的ADC时序图

(作为一个对硬件一窍不通的萌新小白,以前看到这种图基本上都是略过,我不知道它画的是什么,也就是不能从图中得到需要的信息,这里不得不感谢我的师兄,他耐心地教会了我很多有关硬件的东西,让我的知识从此处的空白变得不在苍白,我想我会触类旁通,通过这次机会学会更多的东西。也要感谢我的导师,他给了我机会,平台去接触这方面的知识。说实话,真的很感谢这些帮助过我的人,我觉得自己很幸运,我会珍惜。也许有时候说话的方式不对,还请见谅!还有已经毕业的师兄,你给我提出了很多真诚的问题,让我认识到时间的紧迫性以及自身的差距!)

我将详细地将我知道的把这张图分解开来认识:

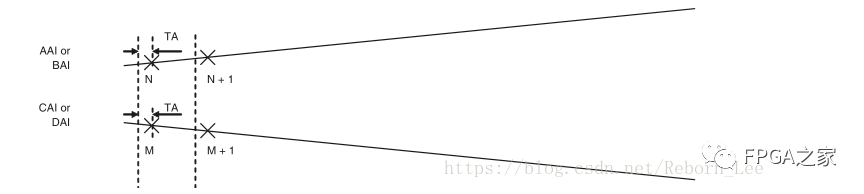

首先是这两条斜线,代表模拟输入的信号,很容易地可以知道上方的模拟输入是从A或者B输入端口输入的模拟信号,下面的斜线代表C或D端口输入的模拟信号;

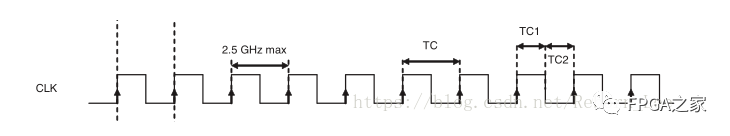

接着便是基准时钟CLK:

该时钟最大的频率为2.5GHz;

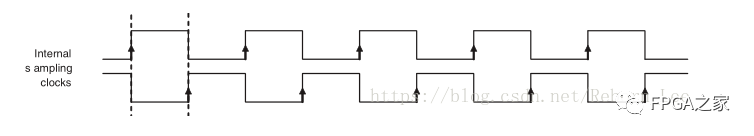

该时钟经过二分频,得到如下两个时钟,称为内部采样时钟,这样内部采样时钟的频率变为最大1.25GHz:

这两个时钟频率相等,相位相反;

时钟上升沿到达时采样;

这两个内部采样时钟的上升沿采样,合起来最大采样频率相当于2.5GHz了。

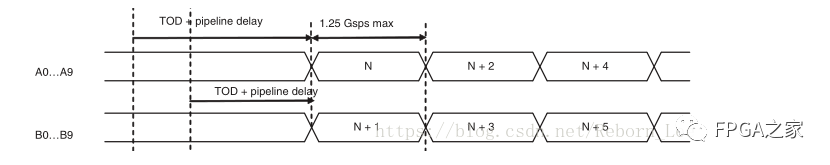

再整个看下面这幅图:

假如模拟信号是从A或B端口输入的,内部采样时钟上升沿到达时,对模拟信号进行采样,第一个上升沿到达时采样数据为N,第二个上升沿到达时,采样数据为N+1,以此类推即可。

假如模拟信号是从C或D端口输入的,采样原理同上,采样数据表示为M,M+1等。

不如将内部时钟标记为clk1和clk2(上下),clk1的第一个上升沿到达时,采样数据为上图的N,clk2的第一个上升沿到达时,采样数据为N+1,clk1的第二个上升沿到达时,采样数据为N+2,clk2的第二个上升沿到达时,采样数据为N+3,以此类推!

好像这样描述会更加的详细!

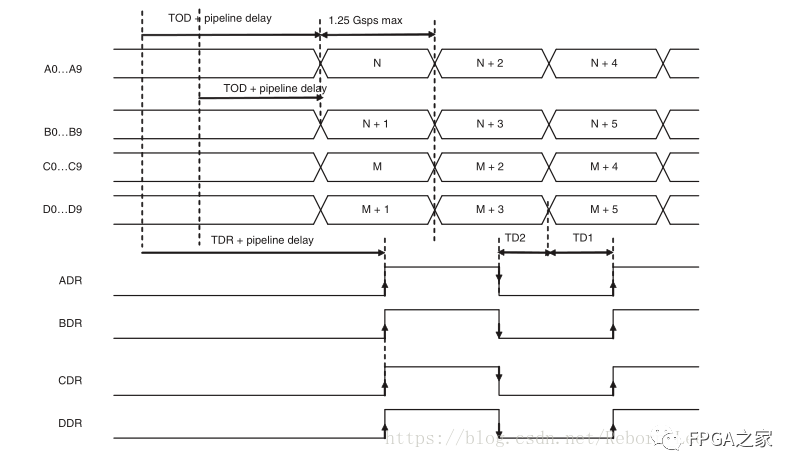

ADC采样芯片采取流水线模式,当采样到信号时,芯片内部发出一个同步使能信号,表示有了采样数据,该同步了数据了,数据同步到哪里呢?例如可以同步到FPGA内部,以供测量或处理!

所谓的流水线结构,就是边采样边同步,这样可以加快处理速度,提高效率!

同步时钟有效时,进行数据同步:

从这幅图也可以看出,同步时钟是内部采样时钟频率的1/2,也就是外面基准时钟频率的1/4,可以认为这个时钟是基准时钟4分频得到的。

若采用的是A或者B输入端口输入,假设是A端口输入,则上面同步时钟有效(ADR/BDR),理想情况下ADR与BDR是一样的,数据同步上升沿和下降沿都有效,即上升沿到来时同步一个数据,下降沿到来时同步一个数据,具体的过程是这样的,ADR的上升沿到来时,同步数据N,BDR的上升沿到达时,同步数据N+1,ADR的下降沿到达时,同步数据N+2,BDR的下降沿到达时,同步数据N+3,如此继续下去。

虽然自己做的工程,没有涉及单通道、以及四通道,但是我想还是有必要去写一下这方面的理解,看看能不能触类旁通,还有想法把单通道以及四通道的部分模块Verilog HDL代码写一下。

为了方便大家看到原汁原味的英文数据手册,这里贴出来吧,想了解更多的可以直接看数据手册!数据手册

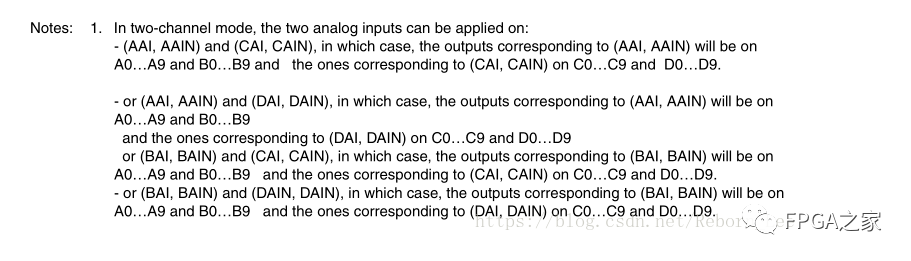

实际上,数据手册中也说了:

简单地解读一下就是,双通道模式中,两个模拟输入可以是以下这几种情况:

(AAI,AAIN)和(CAI和CAIN),在这种情况下,相对于输入(AAI,AAIN)端口的采样输出是(A0...A9)和(B0...B9),在根据上图:

从中可以看出,(A0...A9)和(B0...B9)不就是N,N+1,...吗?只不过每一个采样数据用10位二进制数来表示罢了。

第二、第三、第四中情况我就不多说了,几乎一模一样!

审核编辑 :李倩

-

解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)2023-02-23 5322

-

如何使用ADC08D1000的芯片进行1G双通道采样或2G单通道采样?2025-01-21 468

-

EV12AQ600模数转换器性能如何?2025-03-05 4930

-

EV10AQ190AVTPY 模拟多路复用器现货2018-11-14 2474

-

解读ADC采样芯片(EV10AQ190A)的工作模式(单通道模式)2020-05-07 3061

-

ADC10模块的寄存器及其工作模式2021-11-29 1210

-

请问CH582的ADC DMA多通道采样如何配置?2022-07-26 1576

-

一种高速ADC接口电路设计方案2019-04-12 14327

-

高速adc四路光纤2020-04-24 4454

-

EV12AQ600/EV12AQ605数模转换器介绍2021-08-27 1667

-

STM32F4时钟触发ADC双通道采样DMA传输进行FFT+测频率+采样频率可变+显示波形(详细解读)...2021-12-01 2194

-

STM32的ADC多通道采样2021-12-24 1517

-

解读ADC采样芯片EV10AQ190A的工作模式2023-02-24 2830

-

ADC12DJ3200系列射频采样模数转换器(ADC)规格书2023-06-16 1239

-

ADC12DJ2700 12位、双通道2.7GSPS或单通道5.4GSPS、RF采样模数转换器技术手册2025-11-06 761

全部0条评论

快来发表一下你的评论吧 !