EDA和IP市场出现的三大技术趋势分析

EDA/IC设计

描述

在全球半导体价值链上,EDA和IP可能只占1/30的营收份额,但对整个半导体行业的无形价值却是无法估量的,从Arm和Synopsys在半导体行业的举足轻重地位即可看出。EDA和IP的前沿技术研究和创新对半导体的长期增长有着巨大的影响力,我们在此总结出当前EDA和IP市场出现的三大技术趋势。

01 趋势一:EDA Cloud和AI

相对于维护企业自己的服务器和数据中心,云计算服务具有固定投入低、可扩展、弹性计算使用和无限制存储容量等优势。然而,EDA行业在上云方面是相对落后的,主要原因在于IC设计公司和晶圆代工厂商担心云平台有可能危及自己的IP和设计保密信息。随着云平台服务商针对EDA云计算的专门安全防护让EDA供应商和IC设计公司更为放心,以及IC设计和验证的复杂度不断提升,迫使EDA行业上云步骤加速。

此外,针对特定应用场景(design-for-context)的IC设计和系统设计逐渐成为主流,这要求EDA工具更紧密地与IC设计厂商协作,唯有通过云端部署的高性能计算才能支持这种设计合作。

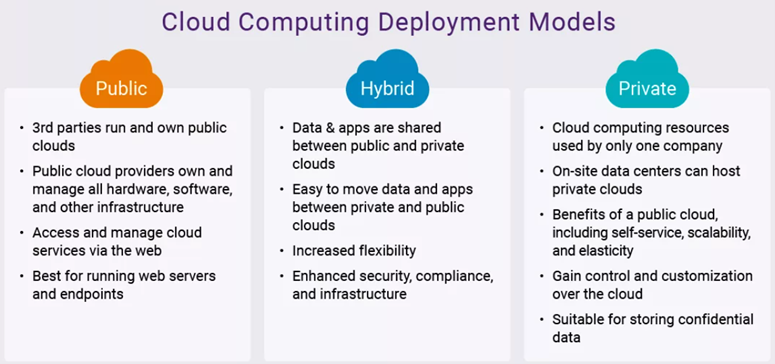

在云端部署云原生EDA工具和预先针对IC设计而优化的硬件平台,以及灵活的EDA使用授权模式,让云端EDA成为很有吸引力的选择。云计算部署模式有三种形式:公有云、私有云和混合云,各自的特点如下图所示。

云服务的三种常见应用方式包括:

基础设施服务(IaaS):云平台服务商提供和维护数据中心服务器等IT基础设施,并作为一种服务提供给各种客户使用;

平台服务(PaaS):云平台服务商提供一个计算平台,让用户开发、运行和管理自己的应用,而不必自己部署和维护复杂的服务器网络;

软件服务(SaaS):在云平台上提供按需使用的软件授权和交付模式,用户不必安装自己的硬件即可使用相应的软件,按使用量付费即可。

云端EDA对IC设计和验证带来的具体好处如下:

可伸缩性强:云端EDA系统可以根据需求即时扩容,比如验证需要算力峰值时;

网络分割:大型IC设计公司的设计中心往往部署在全球多个地方,法律或合同条款可能要求特定IP限定在指定地域内。云端网络可以按照规则划分以避免潜在的合规风险;

冗余备份:云平台服务商的冗余服务器部署在全球多个数据中心,一个地方发生的系统灾难不会导致IC设计数据丢失;

避免单点故障:传统EDA系统网络一般有多个故障点,通过一个节点进行控制管理。如果这个节点出现故障,整个EDA系统网络就会瘫痪,EDA授权、配置和版本管理服务器也不能幸免。云端网络基于微服务模式,不会因为单点故障和影响整个EDA系统;

投入成本低且易于使用

IC设计流程的效率更高:云计算平台的网络延迟更低,分布在多个地方的IC设计团队之间的项目协作更为流畅。

EDA三巨头在EDA上云方面都很积极,分别与亚马逊AWS、围绕Azure和谷歌云服务合作,将自己的IC设计和验证工具搬到云端,以争抢EDA下一波市场高地。例如,新思科技的云服务采用FlexEDA模式,可以为用户提供不受限制、按需使用的EDA软件授权。用户可以选择其SaaS模式,也可以选择BYOC模式,让新思帮助部署自己的云计算网络。

Cadence云服务包括三个部分,分别是:

CloudBurst平台:为用户提供IC设计、验证和实施的云环境,包括授权软件和支持、EDA优化的云计算设施、服务和支持等;

Palladium云验证:托管在由Cadence管理的数据中心,为用户提供按需使用的验证服务,让客户轻松增加所需的峰值容量;

Cloud Passport:将客户私有工具连接到云端,为客户提供自主管理的混合工具。

西门子EDA的Calibre云服务提供与传统签核验证一样的性能和结果,同时让用户根据自己的需要调整EDA资源使用情况。其好处包括:优化的Calibre引擎和经过代工厂商确认的规则检查汇总;采用分层归档方式,降低数据量及缩短最终签核运行时间;Calibre HDB分层数据库模式等。

国内云端EDA服务商也开始活跃起来,值得关注的两家公司包括:

楷领凌云电子设计云平台:为用户提供一站式开箱即用的云上IC设计环境,包含完整的EDA和云IT资源,其中EDA工具由美国EDA全方案和国产EDA产品组合而成,可弹性授权使用主流EDA工具,以及专业的自动化与定制化芯片设计流程服务。该平台可适用于各种规模的数字SoC、模拟芯片或数模混合IC产品设计,如电源管理芯片、驱动芯片、CPU/DSP/GPU等各类计算型芯片、4G/5G基带芯片、光通讯芯片、无线蓝牙等射频芯片、汽车电子控制和娱乐类芯片、MCU和工业控制芯片、加密解密等安全类芯片等。

英诺达:提供基于EDA硬件仿真加速器的云平台,底层采用Cadence的Palladium(帕拉丁)系统,致力于解决复杂芯片的验证资源问题,缩短芯片开发周期。通过向厂商提供安全的EDA验证硬件云入口,客户可以按需使用,既可以满足峰值需求,也可以实现设计全过程的验证需求。

在利用AI/ML进行IC设计的技术创新方面,新思科技和Cadence走在前列。新思科技发布的DSO.ai(Design Space Optimization AI)软件,可以让IC设计工程师更自主地确定在芯片上排列布局的最佳方式以减少面积和降低功耗,由此开始了EDA设计的AI化进程。利用强化学习(reinforcement learning),DSO.ai 可以根据设计目标来评估数十亿个替代方案,并快速产生优于优秀工程师的设计方案。DSO.ai能够解决的问题/方案包括:在芯片上排放各种组件的可能方案数量大约有10的9万次方个(1090,000)。相比之下,谷歌AI在2016 年掌握的围棋走法只有10的360次方个(10360 )。据称DSO.ai的早期试验结果令人印象深刻,实现了18% 的工作频率提高,而且功耗降低了 21%,同时将工程时间从六个月缩短到一个月。

Cadence推出的智能芯片探索器Cerebrus可通过强化学习来优化物理设计流程,它在功能上与新思的DSO.ai 类似,专注于物理设计。Cadence Cerebrus的发布似乎进一步验证了强化学习技术作为芯片设计方法论的下一个重大转变。随着设计师越来越习惯让机器决定布局,以及竞争压力的增加,AI将逐渐渗透到IC设计流程的各个部分。

Cerebrus建立在大规模计算和机器学习架构之上,并充分利用了完整的 Cadence数字全流程解决方案。Cerebrus借助独特的强化机器学习引擎来提供更好的设计 PPA 结果(性能、功耗和面积)。通过使用完全自动化、机器学习驱动的 RTL-to-GDS 全流程优化技术,Cerebrus 可以比手动调整的流程更快地交付这些更好的 PPA 结果,从而极大提高工程设计团队的生产力。

02 趋势二:Chiplet互联与高速接口IP

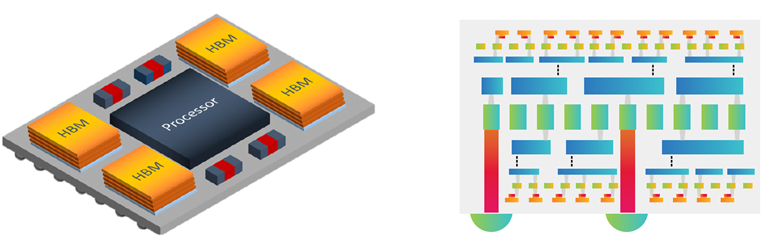

基于Chiplet架构,芯片设计师可将不同功能和工艺节点的芯片通过2D或2.5D/3D的封装方式,异构集成在一起。此外,Chiplet架构还可以将数字、模拟或高频工艺的不同裸片集成到一起,甚至在设计中加入高度密集的3D内存阵列,比如高带宽内存(HBM)。这样,IC设计公司就可以将来自不同IP供应商的Chiplet像搭建LEGO积木一样,拼装出不同的芯片产品,从而以较低的成本开发出更强大的芯片。

Chiplet架构和理念对IP开发商也很有吸引力,因为他们可以根据自己的专长开发具有特定功能的标准化Chiplet,就像现在的IP一样授权给多家IC设计公司,从而最大化其专利技术的价值。据Omdia预计,Chiplet市场规模今年将达到40亿美元,而到2030年有可能增至1000亿美元。

问题是,这些Chiplet之间及其它类型的裸片之间如何实现高速数据传输?如果没有业界统一的通用互联标准,Chiplet积木只是梦想罢了。

在众多Chiplet互联标准中,由Intel提出的通用Chiplet互联标准(UCIe)在很短时间内就引起了业界广泛关注,目前来看最有希望成为业界统一的互联标准。UCIe是唯一具有完整裸片间接口堆栈的标准,其他标准都没有为协议栈提供完整裸片间接口的全面规范,大多仅关注在特定层。此外,UCIe不但支持有机衬底或层压板等传统封装,也可以支持2.5D和桥接等先进封装,如硅衬底、硅桥或再分配层(RDL)扇出等形式,预计未来还会支持3D封装。

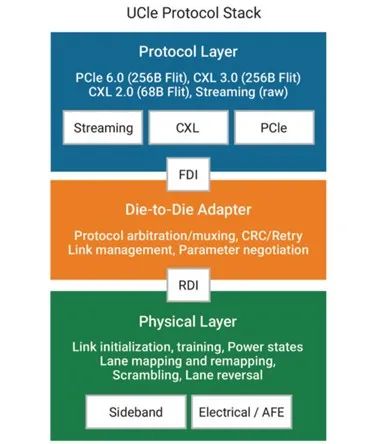

UCIe协议栈本身有三层:

最上端的协议层通过基于流量控制单元(FLIT)的协议实现,确保最大效率和最低延迟,并支持多个主流协议,包括PCIe、Compute Express Link(CXL),以及用户定义的流协议。

中间的D2D适配层用于对协议进行仲裁与协商,以及通过裸片间适配器进行连接管理。基于循环冗余检查(CRC)和重试机制,该层还包括可选的错误纠正功能。

最下面的物理层(PHY)规定了与封装介质的电气接口,是电气/模拟前端(AFE)、发射器/接收器以及边带通道(Sideband)在两个裸片之间进行参数交换与协商的层级。逻辑PHY可实现连接初始化、训练和校准算法,以及测试和修复功能。

UCIe协议栈示意图

UCIe协议具有如下优点:

UCIe的Sideband、DDR、Forward Clock设计使得UCIe单个应用场景下的模块设计复杂度相对更低,模块验证也更加容易;

UCIe传输时延和功耗更低、速率更高、BER更低,在功耗和性能的平衡方面做得比其他协议好;

由于和PCIe/CXL的无缝对接,可以利用PCIe现有的强大生态,轻松地将板级互联扩展到封装内部;

UCIe不但支持PCIe向CXL的扩展,还支持用户自定义的Raw mode,一个D2D Adaptor 可持架接多个协议栈。

目前已经有不少国内厂商加入UCIe联盟,其中包括:阿里云、日月光、长电、华为、芯原、灿芯、芯耀辉、超摩科技、合见工软、芯和半导体、长鑫、牛芯、芯云凌、芯瑞微、芯来科技和奎芯等。

此外,由中国计算机互连技术联盟(CCITA)发起的Chiplet标准《小芯片接口总线技术要求》在中科院计算所、工信部电子四院和国内多个芯片厂商合作推动下,也已经发布。小芯片接口总线技术的体系架构主要包括数据链路层(Data Link Layer,DLL)、物理适配层(Physical Adaptation Layer,PAL),以及物理层(Physical Layer,PHY)等。

此标准列出了并行总线等三种接口,提出了多种速率要求,总连接带宽可以达到1.6Tbps,以灵活应对不同的应用场景以及不同能力的技术供应商。通过对链路层、适配层、物理层的详细定义,实现在小芯片之间的互连互通,并兼顾了 PCIe 等现有协议的支持,列出了对封装方式的要求。小芯片设计不但可以使用国际先进封装方式,也可以充分利用国内通用封装技术。

无论IC设计公司、EDA和供应商、晶圆制造和封装测试厂商,纷纷拥抱Chiplet,原来采用BoW或其它互联协议的设计也开始转向UCIe。以EDA/IP供应商为例,EDA巨头都在积极与TSMC等晶圆代工厂商和封装厂商合作开展Chiplet相关技术开发;Synopsys和Cadence等接口IP供应商也都将Chiplet作为实现业务快速增长的契机。

Chiplet作为一种新型IP形式,必将推动一波新的IP开发热潮,造就一批IP新锐公司。其中有三家IP公司值得关注,分别是Eliyan、Alphawave和奎芯科技,详情参见文章:Chiplet(芯粒)互联:从一团乱麻(BoW)到统一互联标准(UCIe)。

03 趋势三:2.5D/3D-IC设计

过去50年来,封装技术虽然没有像IC设计和晶圆制造发展得那么快,但也经历了几次重大的技术飞跃,比如70年代出现的多芯片模组(MCM)封装;2000年出现的系统级封装(SiP);2010年出现的硅Interposer(即2.5D封装);以及2020年出现的3D-IC先进封装。系统级芯片(SoC)的设计成本高昂、晶圆工艺接近物理极限,以及市场对性能/功耗/面积(PPA)的严格要求迫使半导体行业寻求新的技术突破,其中融合Chiplet、异构集成和先进封装的技术方向似乎带来了超越摩尔定律的希望,同时也为封装测试(OSAT)厂商在整个半导体产业链上创造了提升价值的机会。

左边的硅Interposer(即2.5D封装)和右边的3D集成封装。(来源:Cadence)

相对于传统单个裸片SoC设计,2.5D/3D-IC具有如下优势:

降低芯片设计成本:高性能复杂芯片内部的处理器和逻辑单元可以采用先进的晶圆工艺,而模拟和存储器单元则可以采用相对便宜的成熟工艺,从而降低整体设计成本,并缩短开发周期;

封装内的裸片、chiplet和其它单元之间的互联可以实现很高的数据传输速度和带宽,比如对高性能的存储器和SerDes速率可以达到200Gbps;

裸片的3D堆叠可以减少I/O驱动和互联、降低阻-感-容(RLC)、芯片尺寸和整体功耗;

更多采用可以IP复用的chiplet,让模拟/RF单元使用较为成熟的工艺,并可以集成光电单元和MEMS器件。

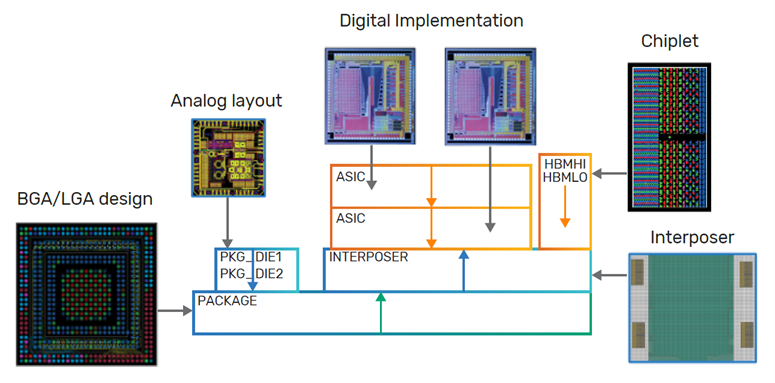

系统级3D设计涉及数字实现、模拟布局、Chiplet和Interposer的综合规划和优化。(来源:Cadence)

要实现以上这些价值,不但需要晶圆制造厂商和封装厂商的技术创新,EDA工具和设计流程也面临极大的挑战。具体表现在:

顶级/系统级异构设计的规划和优化,需要从D2D到封装甚至PCB的优化网表,以及准确的电磁和热分析;

从裸片、chiplet、封装和PCB等不同阶段,都需要贯穿数字、模拟和RF域的协同设计和协调分析;

目前的EDA点工具都有各自的接口和模型,只能提供碎片化的2.5D/3D方案,但无法实现电源/信号/散热/电磁干扰/时序等综合性的自动化抽象、分析、验证和测试。

领先的晶圆代工厂商和封测厂商都在开发和推广各自的2.5D/3D IC设计工艺,比如TSMC 的3DFabric(包括CoWoS和INFO);Intel的EMIB和Foveros;三星的I-Cube;日月光的FOCoS;Amkor的SWIFT;以及长电的多维扇出封装集成(XDFOI)等。2.5D/3D IC设计要成为主流,让Fabless、OEM厂商和互联网巨头在做复杂的芯片设计规划时考虑采用,就需要产业链各个环节携手打造3D-IC生态,其中全流程的EDA设计工具是重要一环。

编辑:黄飞

-

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 全书概览2026-01-20 2203

-

eda的两种设计方法 ip与eda技术的关系是什么2023-04-10 8574

-

EDA工具市场发展趋势分析2021-06-12 3996

-

谈谈LED技术趋势及市场动态2021-06-03 1719

-

基于现场可编程门阵列技术和EDA技术实现IP核的设计方案2020-08-10 1355

-

EDA技术发展概况_EDA技术的发展趋势2020-07-09 4868

-

思源科技挑战EDA市场旧格局2020-07-07 2487

-

EDA技术从何而来?EDA技术发展历程2019-02-21 4157

-

eda是什么技术_eda为什么又叫单片机2018-03-12 22370

-

针对示波器市场出现的5个流行趋势进行分析2017-12-10 1032

-

芯片IP授权市场还将增长15年,接口IP将成最大黑马?2017-10-24 3772

-

EDA和FPGA厂商布局IP市场,半导体产业链影响几何?2013-04-09 10570

-

网络视频监控与IP存储发展趋势分析2012-12-20 1576

-

EDA技术在数字系统设计分析中的应用2008-06-12 5827

全部0条评论

快来发表一下你的评论吧 !