TI的片上系统SoC实现SAR成像设计

描述

高性能航空电子和国防应用(包括雷达),对大多数机载系统的功耗限制都非常敏感。在功率有限的情况下,处理性能和功耗之间建立最佳平衡对每个嵌入式系统都至关重要。这些系统拥有业界最长的产品生命周期,通常以几十年而不是几年来衡量,因此可靠性和寿命也是选择嵌入式系统的关键因素。

电子战,信号情报,军事、监视和气象雷达,军用飞机和通用航空控制系统等应用都需要高吞吐量、高速的数据采集和处理。在将数据实时分发给终端用户之前,这些系统需要能够从信号中提取巨大的数据量,在原始数据上应用强大的信号处理算法,以提高准确度和精度。

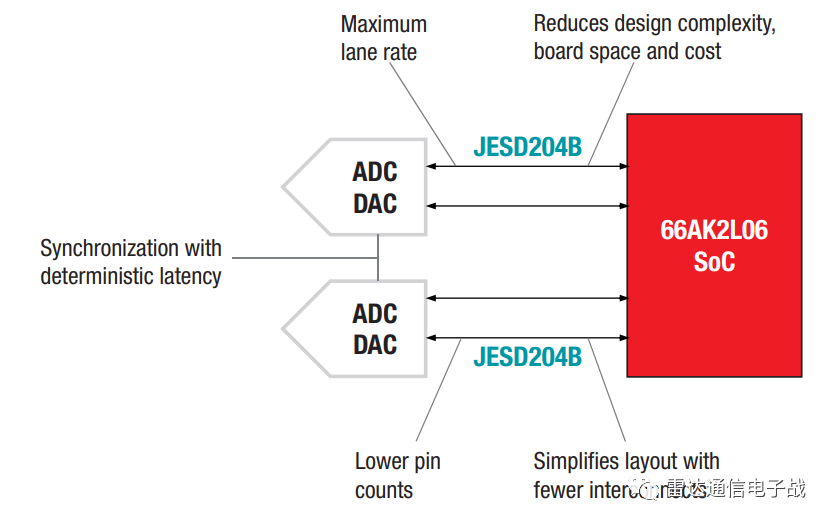

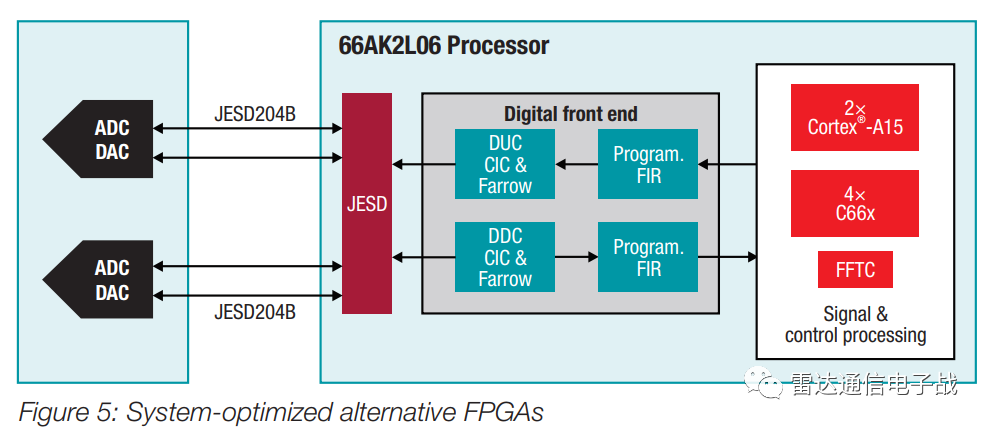

TI的66AK2L06片上系统(SoC)使雷达应用程序的设计者能够在系统成本、尺寸、重量和功率(SWaP)方面在当前解决方案的基础上提高性能。 JESD204B接口与66AK2L06 SoC的集成不仅降低了系统设计的复杂性,而且还减少了雷达应用的空间需求。

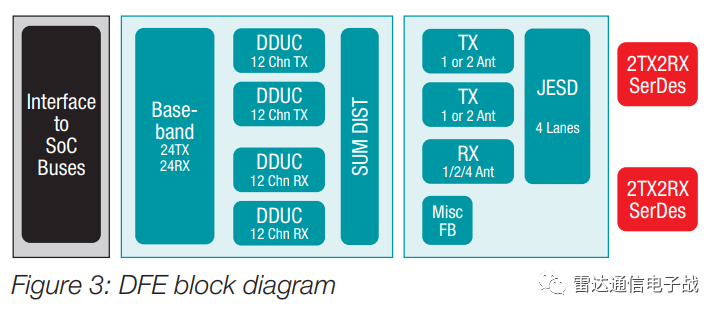

SoC集成了可编程数字前端(DFE),使得适应性和可扩展性能够满足不断变化的高速数据采集和生成的需求。 开发人员可以利用SoC上的快速傅立叶变换协处理器(FFTC)进一步优化SAR算法的延迟问题。总之,增强的性能、更低的功耗、更小的占地面积可以将整个系统成本降低50%,面积降低66%。

如何消除SWaP限制?

合成孔径雷达由于其灵敏度高、精度高、不受天气和大气条件的影响以及探地能力,已成为飞机或航天器成像的首选传感器。SAR系统由于信号处理的密集性,需要很大的数字处理能力。客观条件下SWaP的限制对数字信号处理(DSP)算法的实现提出了很高的效率要求。随着SAR设计和数据使用需求的不断发展,适应性在实现中也至关重要。

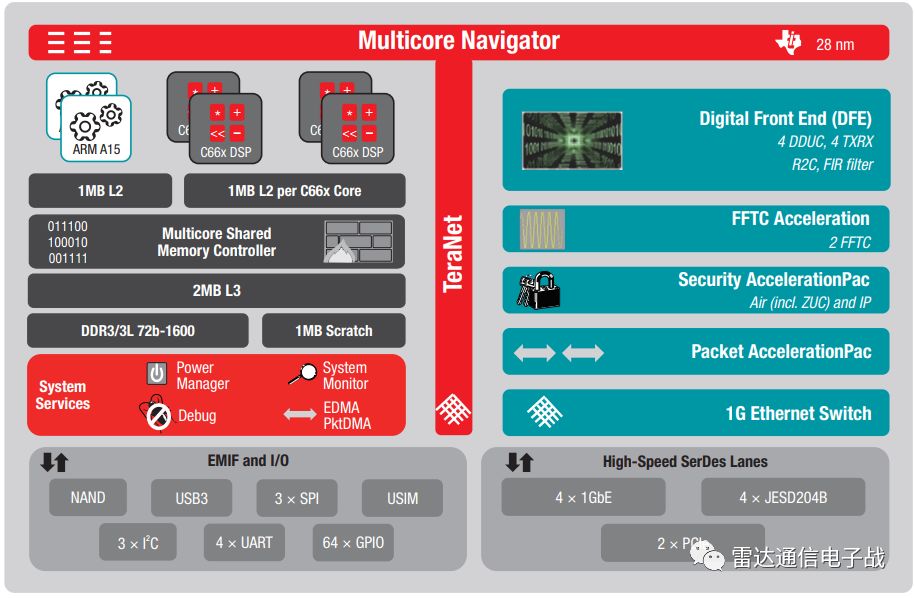

更高的实现效率和适应性要求,让可编程DSP核与专用加速器相结合的片上系统(SoC)成为了首选的处理平台。SoC解决方案在非常低的功率水平下提供了很强的信号处理能力,可支持航空电子和国防(包括雷达)、测试和测量、医疗和其他工业应用。 基于TI新的KeyStone II多核架构,66AK2L06 SoC集成了多种处理元件,包括TI固定和浮点型TMS320C66x数字信号处理器内核、最快的ARMCortexA15内核和高级加速器。 66AK2L06 SoC配备高速JESD204B直接连接到TI高速模数转换器(ADC)、数模转换器(DAC)和模拟前端(AFE)的接口。集成了用于数字转换和数字滤波的软件可编程DFE,进一步减少了功率和空间,在较小的占地面积内产生每瓦最佳功率。

获得浮点精度不牺牲性能?

多DSP核的使用是一项关键技术,它有助于使越来越复杂的信号处理算法朝着波形密集型应用的前沿发展,如航空电子、雷达、声纳、测试和测量以及波束形成。多核功能,加上扩展的AccelerationPacs阵列和多核DSP的开发工具,使得在非常低的功率下以紧凑的外形实现高性能。 航空电子和国防应用需要多核DSP来满足这些任务关键型应用的发展要求,包括更高的处理吞吐量、更好的分辨率,提高精确度和先进接口的集成度。这些需要依赖于浮点计算来达到所需的精度。 KeyStone II体系结构的关键是其多核导航器、TeraNet和多核共享内存控制器,从而为JESD附加应用程序提供了一种高度灵活和可扩展的解决方案。

66AK2L06主要特点:

•两个ARM Cortex-A15 RISC核@1.2GHz,8400 DMIPS;ARM核以超低功耗水平提供高性能RISC处理,以处理控制和管理功能

•四个TMS320C66x数字信号处理器核@1.2GHz,带定点和浮点处理,提供76GFLOPs和153GMACS

•集成DFE技术(可编程滤波器、IQ不均衡校正、上采样/下采样等)减轻信号处理负担

•先进的集成网络协处理器将IP路由和IP终端从ARM/DSP核移开,从而实现更大的系统和对加密和安全的有效支持。

•FFTC将FFT/iFFT执行的延迟提高到8K个点,与定点 DSP实现相比具有更好的性能

•集成多核共享内存控制器(MSMC),核和加速器共享2兆字节内存

•多核导航器为多核SoC软件设计提供单核简单操作

•带4×1GbE端口的以太网交换机

•两个单通道PCIe Gen2接口,最多支持5 GBaud

•高度集成的SoC降低了物料清单(BOM)成本、系统规模和功耗

•高速JESD204B到芯片的接口优化了电路板布局(更少的通道和管脚),并降低了多个ADC/DAC/AFE的最多四通道(最高SerDes速度为7.37 Gbps)接口的功耗。

JESD204B

除了在硅片层面的更大集成度外,66AK2L06 SoC还实现了更小的BOM,降低了电路板生产成本。通过使用JESD204B串行通信链路接口,简化了电路板的设计和布局。JESD204B在数据转换器(ADC/DAC)、现场可编程门阵列(FPGA)、DSP、SoC和专用集成电路(ASIC)等板载逻辑器件之间提供高吞吐量、低管脚数量的串行链路。

通过在数据流中嵌入时钟并包含某些嵌入式算法以优化数据位的采样,JESD204B简化了设备之间的路径,板上需要的通道明显更少。 相比之下,要实现与JESD204B相同的吞吐量,更突出的SerDes接口(例如PCI Express)将需要更多的线路。更少的线路意味着设备上的I/O通道数量也会减少,从而降低管脚数,允许更小的封装尺寸。

除了简化系统设计外,JESD204B还通过减少通常在其他SerDes接口(如PCIe和LVDS)使用的更多线路上执行的设置和保持时间来缩短电路板bring-up。JESD204B是一个灵活、可扩展的串行链路接口,可以适应多种数据传输速度和数据交换,例如一个JESD差分对上的多个ADC或DAC。

数字前端(DFE)

通过集成数字前端(DFE),66AK2L06 SoC将所有的高通量数字处理集成到一个优化的软件可编程处理单元中,该单元包括控制、基带和DFE。因此,SoC能够在芯片上完成各种功能,从基本信号处理(包括信道化/抽取和重采样)到指数复乘法、滤波和FFT/IFFT,这些都是合成雷达处理算法所必需的。 雷达系统的设计者现在可以从片上数字上/下变频、滤波和高效的高速连接以及最新的高速ADC/DAC中获益。

信道化和数据转换器接口功能,是大多数应用必须具备的信号处理功能:

•符合频谱发射的载波滤波

•单频和通道的聚合和分发

•TI高速ADC和DAC的JESD204B SerDes接口

•基带(BB)模块提供:

每个通道传输数据的可编程复增益

数据传输的可编程环路限幅器

接收数据的可编程后端自动增益控制(BeAGC)

TX和RX通道的可编程功率测量选项

最多支持24个接收通道和24个发送通道

提供闭环功能

•数字上/下变频(DDUC):

多通道上/下变频

灵活的输入/输出采样率

可编程重采样选项

可编程FIR,以满足频谱滤波要求

每个通道的增益、相位和分数延迟调整

FFTC

FFTC模块可在66AK2L06 SoC上的所有四个C66x核上访问,该模块可用于加速各种应用中所需的FFT和IFFT计算,从而为其他处理腾出DSP核心周期。

FFTC提供了以下特性:

•IFFT和FFT可处理的大小:

2a×3b,2≤a≤13, 0≤b≤1 最大为8192

12×2a×3b×5c ,12到1296之间

•16位I/Q输入和输出

•吞吐量根据FFT大小略有变化。例如4096点的FFT,对于1.2 GHz设备,它可以由单个FFTC以525 Msps的吞吐量进行处理。

•信噪比从84dB到100dB,取决于FFT的大小

•动态和可编程配置模式

•动态配置模式可返回块参数

•支持“FFT移位”(可选左/右半部分)

•支持循环前缀(添加和删除)

•乒乓输入、输出缓冲区

•输入数据随移位可配置

•输出数据可配置

•可补零

SAR系统实现

SAR系统通常安装在一个移动平台上,如飞机或航天器,通过发射一串脉冲信号来工作,接收机收集反射回雷达的每个脉冲的回波并记录下来。

SAR系统利用SAR天线在目标区域上移动的距离来“合成”更大的天线孔径(天线的“尺寸”),比传统的波束扫描雷达提供更高的空间分辨率。然后,对记录的雷达回波进行信号处理,将来自多个天线位置的记录合成起来,以生成图像。

由于雷达的波长比可见光或红外光的波长长得多,因此SAR可以透过云层、烟雾、湿度和黑暗而“看到”。选择合适的频段,可生成穿透树叶的图像,从而绘制树丛下面土地的像,或者穿透地表以下或浅水。

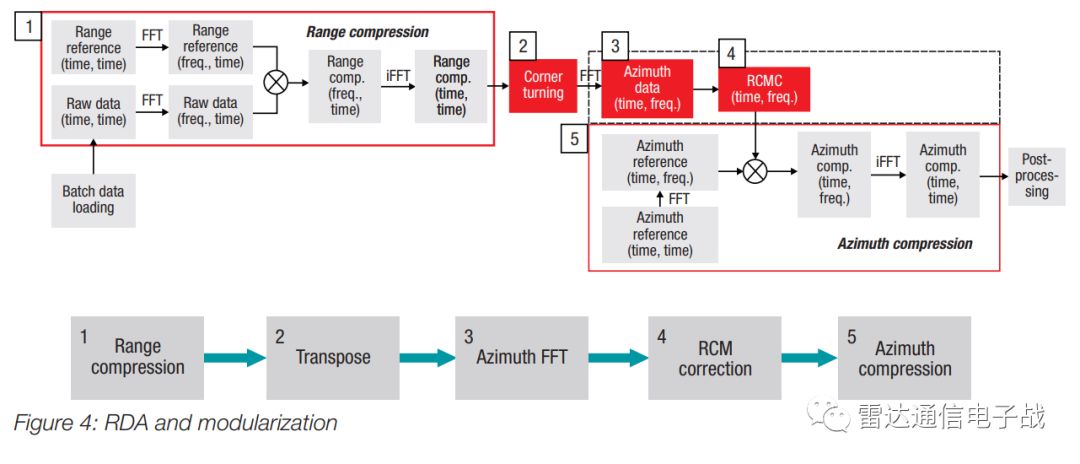

SAR数据在时间域采集,变换到频率域和距离多普勒域,并应用匹配滤波。

SAR处理方法有多种,但各有优缺点。 距离多普勒算法(RDA)是一种一维傅立叶变换。另一种类似于RDA方法的是chirp scaling算法(CSA)。第三种方法是二维傅里叶变换算法,称为波动方程(WE)算法。这种二维WE算法同时处理距离和方位数据,而距离多普勒处理算法先进行距离压缩处理,再进行方位压缩处理。

RDA适合低斜视场景成像,其主要步骤是:

1. 距离FFT

2. 距离压缩

3. IFFT

4. 方位FFT

5. 距离单元徙动校正(RCMC)

6. 方位压缩(方位滤波)

7. 图像重建

距离和方位压缩都是相关处理,进行了二次一维匹配滤波运算。第一次匹配滤波作用于各个脉冲的雷达回波,第二次匹配滤波作用于多普勒维。图4显示了基于距离多普勒处理算法的合成孔径雷达处理的基本概念,该算法是在C66x DSP多核上实现的低功耗合成孔径雷达。

数据被采集并使用JESD204B的RX接口装载到66AK2L06 SoC中。设S0(τ,η)为接收数据,其中:

•η=k/fa是“方位时间”(脉冲之间的慢时间),fa是方位采样率;

•τ=m/fr是“距离时间”(脉冲内的快时间),fr是距离采样率;

数据存储在内部共享存储器(MSMC)中,直到一个触发信号发送到66AK2L06平台,以表示单个脉冲采集的结束。一旦接收到完整的脉冲序列,就会触发距离压缩处理。

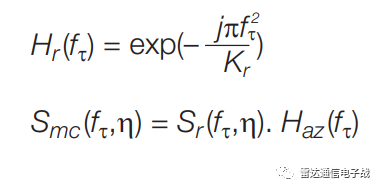

距离压缩是将接收到的脉冲沿距离方向压缩,将主要能量集中到较窄的持续时间内。它通过在频率(距离)-时间(方位)域中原始数据和参考信号之间的快速卷积来执行。因此,首先沿距离向执行FFT,然后执行匹配滤波的乘法和距离IFFT。匹配滤波在频域中实现为复数相乘。

距离压缩在66AK2L06平台上的步骤:

1. 用(“行”)执行“距离”FFT来变换数据,在一个C66x内核(浮点操作-约28us处理4K点 FFT)或在FFTC加速器上(块浮点操作-约8us处理4k FFT)得到的数据是Sr(fτ,η)矢量,fτ是距离频率。

2. 使用C66x数字信号处理器内核应用距离匹配滤波器:

3. 执行“距离”IFFT变换到时域中,得到的数据是S2(τ,η)向量。 转置用于重新排列压缩数据,使其可以按方位线顺序读取,以便沿方位向进行处理。存储器中的距离压缩数据被按块分组,最好是平方大小,这是因为当加载/写入数据的行大小不小于行数时,存储器访问可实现更高的效率。

为了有效地在外部存储器和内部存储器(L2)之间加载/写入数据,66AK2L06 SoC上的增强直接存储器访问(EDMA3)可应用于服务数据传输。EDMA3是TI KeyStone架构的独特设计,其特征在于在三个维度上具有完全正交传输,可实现二维同步、灵活传输定义、多DMA通道和存储器保护。

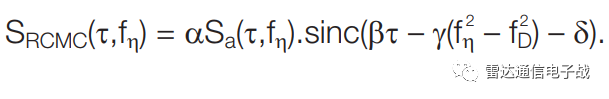

距离单元徙动是由平台运动引起的距离变化导致(遵循双曲线规律)。距离单元徙动校正是将存储器中的数据重新排列,使轨迹变直,从而可以沿每个平行的方位线进行方位压缩。RCMC可以通过基于插值核的距离插值操作来实现,例如sinc函数或样条曲线。

在TI公司的TMS320C6678多核DSP上,采用16组8抽头sinc滤波器作为内插滤波器。16组滤波器的系数按常数存储。选择哪种滤波器的索引由小数部分决定。每个距离单元使用相同的滤波器。TMS320C66x利用DSP独特的双浮点加载、写入和运算指令,提高了插值计算效率。

RCMC在66AK2L06平台上使用的步骤:

•沿方位方向(“列”)执行“方位”FFT,以在DSP或FFTC上将数据变换为距离多普勒域。

•得到的数据是Sa(τ ,fη)向量,fη是方位频率。

•在估计多普勒频率fD后,“sinc”函数适应于信号(驻定相位原理)

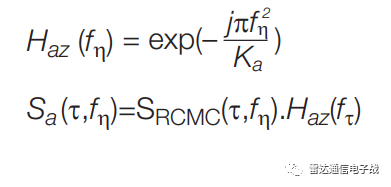

方位压缩是将轨迹中的扩展能量压缩到方位向上的单个单元。此过程与距离压缩类似,只是方位参考函数与距离有关。也就是说,每一条距离线的方位参考函数是不同的,这导致了比距离压缩更复杂的过程。

与RCMC类似,方位压缩也是在距离多普勒域进行的。通过将方位压缩后的信号变换回时域,再进行后续处理,得到最终的图像。

1. 在66AK2L06平台上使用C66x数字信号处理器内核应用方位匹配滤波器:

2. 执行“距离”IFFT变换,得到的数据是S3(τ,η)向量。

距离多普勒算法在片上的实现

在66AK2L06 SoC中,利用四个C66x的DSP核,每个核处理不同部分的数据,可以实现距离多普勒算法的并行计算,可以使用openMP在不同的内核上高效地部署处理任务,以实现负载平衡并最小化处理延迟。

利用66AK2L06 SoC上的硬件加速器提供了多种好处,从释放DSP核上的额外处理周期到减少应用程序总延迟。在处理SAR算法之前,DFE可以减少多种类型的处理。

从ADC接收到的信号是实信号,可以在SAR处理的第一阶段之前进行调理。在高达368Msps的流处理下,DFE可以使用其R2C模块以18位精度的输入和输出将实信号转换为复信号。使用可编程滤波器,DFE可以执行复FIR滤波,最多有79个系数。

对于SAR算法本身,距离/方位压缩需要很多FFT和IFFT。这些功能可以分到66AK2L06 SoC的两个FFTC加速器上。有文献指出在单个DSP核上执行SAR算法以处理4K×4K图像的延迟将耗费1404 ms,其中假设50%的延迟是由于FFT/IFFT。在处理4K点时,FFTC的吞吐量为525Msps,处理延迟降为约8us。

文献中的方位FFT由4096个4K点的FFT组成,当用浮点数在DSP核上执行时,占总延迟(252ms)的18%。如果使用66AK2L06 SoC中的两个FFTC,同一方位FFT将花费约16ms延迟。 考虑到访问外部存储器的影响,在本SAR算法实现实验中,使用两个FFTC可以使FFT/IFFT处理延迟至少提高5倍。这使得总延迟从1404ms下降到842ms,下降了40%。延迟的减少将释放大量的周期资源来处理其他算法,从而提高最终SAR成像的性能。

另外两种SAR处理方法CSA和WE也是信号处理驱动的算法,其中需要大量的FFT/IFFT运算、滤波和复乘法运算,这表明66AK2L06 SoC是处理这些算法的适合平台。

如何倍速开发?

合成孔径雷达(SAR)系统和专用软件开发工具已被广泛应用于军事和非军事领域,包括探测、监测、绘制地图和测量陆地、海洋、冰以及地球和其他行星大气中的现象。

现代雷达设计在雷达系统前端(激励器/接收器)集成了信号处理功能,包括波形生成、滤波、矩阵逆/转置操作、FFT/IFFT和信号相关。雷达系统中也有数学函数,包括指数复数乘法和其他数学运算。

许多设计者在基于C的处理器中实现了这些功能(定点/浮点操作)。这些类型的设计可以利用66AK2L06 SoC中提供的小尺寸和四个定点和浮点C66x DSP核来满足系统需求,同时减少延迟和提高系统功耗。

基于TI的高通量KeyStone II架构,新的66AK2L06 SoC是一个可扩展的低功耗解决方案,集成了DFE和高速JESD204B接口,满足更严格的系统成本和航空电子和国防(包括雷达)应用的要求。

这个集成的系统解决方案可以将开发时间从几周缩短到几天,从几天缩短到几小时。

开发人员可以利用TI设计的优势,使用多个ADC、DAC和AFE对66AK2L06 SoC进行预验证。所有这些都能加快时间,让开发人员的开发速度提高三倍。

审核编辑:刘清

-

SoC片上系统详解2024-07-29 2237

-

什么是片上系统soc?soc如何工作的?2024-03-28 4148

-

什么是片上系统SoC?2024-03-19 2378

-

什么是片上系统(SoC)?SoC是如何工作的?2024-03-08 12093

-

519.soc片上系统小凡 2022-10-04

-

片上系统(SoC)基本原则和参考书2021-03-26 1105

-

如何使用FPGA实现微型SAR成像的量化显示2021-01-26 1239

-

SOC片上系统的解决方案2018-06-26 6920

-

德州仪器(TI)推出CC2541蓝牙低功耗片上系统(SoC)2012-01-18 4706

-

Aptina推出AS0260 SOC(片上系统)成像解决方案2011-12-16 3883

-

片上系统(SOC)的UEFI开发与创新2011-12-07 1151

-

片上系统(SoC),片上系统(SoC)原理结构是什么?2010-03-26 3116

-

TI推出多核片上系统架构 实现5倍性能提升2010-02-24 1170

-

片上系统(SoC)的VoIP 网关的研究2009-12-17 772

全部0条评论

快来发表一下你的评论吧 !