解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)

描述

昨天即上篇博文讲了EV10AQ190A这种ADC芯片的工作模式:双通道模式

我十分重视这些内容,因为这是我认识硬件工作模式的起点,当然这也只是理论上的内容,实际采样过程中也6许会遇到这样那样的问题,那就需要自己慢慢探索了,理想与工程还是会有一定的差距的!

这篇博文主要讲四通道模式:

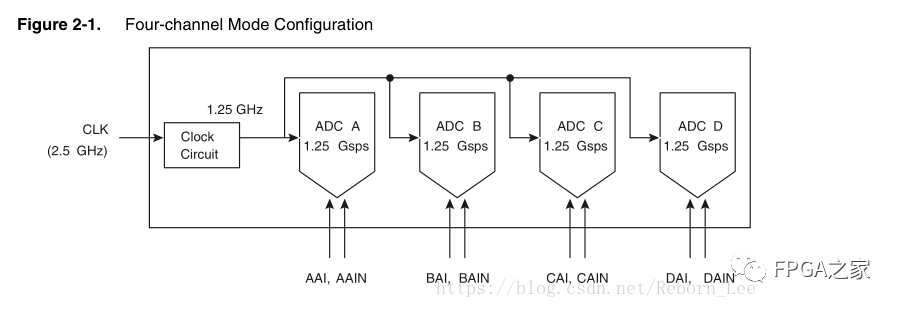

这种模式的框架或者组态(configuration)(我真的不知道这个单词如何用中文准确的翻译处理,我总感觉应该是原理框图),算了以后就叫做组态吧,强行翻译。

由上图可知,四通道模式有4个输入端口,我们分别称其为A端口,B端口,C端口,与D端口,四个端口分别对应四个通道,也就是说四个输入端口中每个端口分别对应一个ADC采样通道,例如当模拟输入从A端口输入时,就有ADC A进行采样。

从上图我们还可以得知,外部2.5GHz的时钟为该ADC芯片提供时钟源,进入内部时钟电路(Clock Circuit),内部时钟电路相当于一个二分频的作用,产生1.25GHz的时钟信号分别输入四个通道,为其提供时钟信号。

每个通道都是一个ADC核,所以说这个ADC有四个核,(有关这里的时钟关系等我单独一篇博文研究吧!)。

每一个ADC核采样速率都是1.25Gsps,也就是说每秒采样1.25G个点!

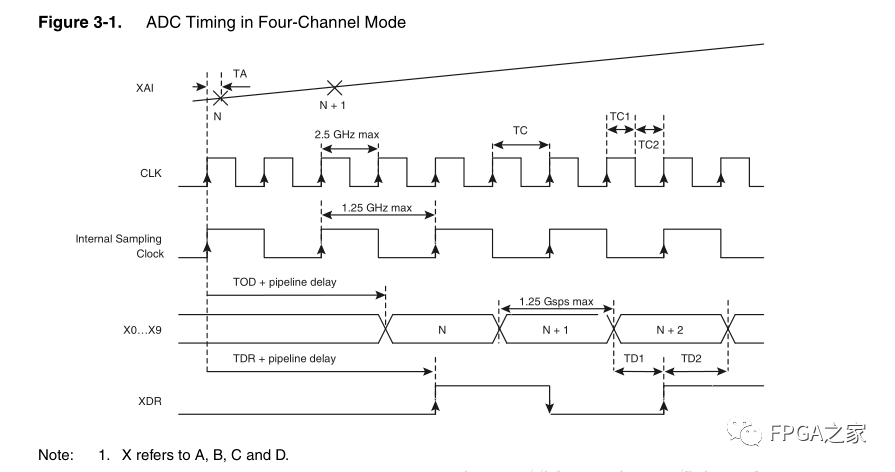

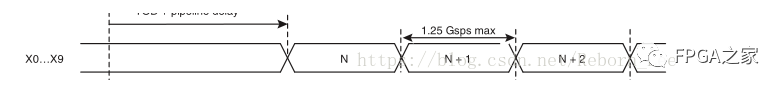

下面看看其时序图:

四通道模式的时序图可以说很简洁了。

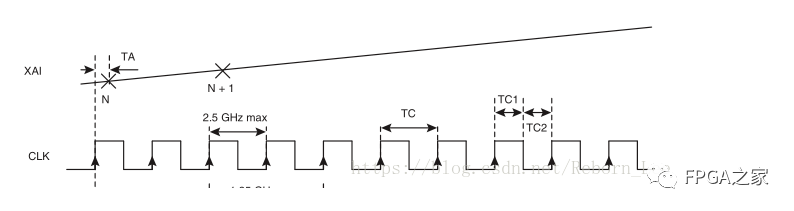

模拟输入XAI与基准时钟CLK:

这个时钟频率最大为2.5GHz;

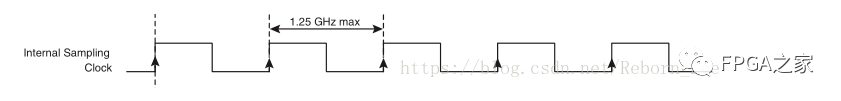

CLK时钟二分频得到ADC内部采样时钟:

频率为CLK的一半,最大为1.25GHz;

基准时钟CLK四分频得到采样数据同步时钟:

这个时钟频率就更低了,为基准时钟CLK的1/4;

内部采样时钟的上升沿到达时,开始采样,分别为N,N+1,...

每一个核(每一个通道)每秒采样1.25G个数据点;

同样该模式也采样了流水线结构,ADC的任一个通道采样得到数据后,这时数据的同步也就开始了,关于ADC怎么知道什么时候同步的问题,我想暂且就认为采样得到数据后,内部发出一个信号,这个信号通知ADC该同步了。

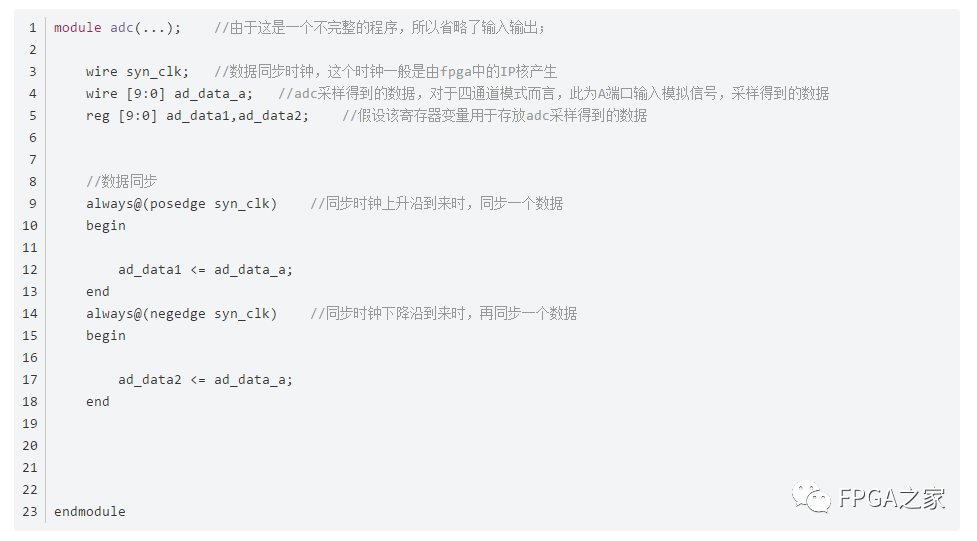

最后贴出部分代码,此代码讲了写此程序的部分思路,好多东西需要自己往里面填写,例如adc单通道模式采样模块肯定要用一个IP核产生采样数据,还有时钟产生模块等,这里仅仅为了理解上述同步过程而简写的几行代码!

审核编辑 :李倩

-

ESP8266芯片是否在四通道模式下从EEPROM读取?2024-07-08 324

-

EV12AQ600模数转换器性能如何?2025-03-05 4851

-

使用AD7656进行四通道采样接地后采样发现采样值出现异常2018-09-21 3037

-

EV10AQ190AVTPY 模拟多路复用器现货2018-11-14 2445

-

FMC转换器板学习资料:FMC147-多通道多模式的10位ADC 1.25 GSPS / 2.5 GSPS / 5.0 GSPS FMC-HPC模拟到数字转换器板2019-05-13 3715

-

解读ADC采样芯片(EV10AQ190A)的工作模式(单通道模式)2020-05-07 2990

-

使用AD7656进行四通道采样,将四通道输入接地后采样值出现异常的原因?2023-12-18 630

-

一种高速ADC接口电路设计方案2019-04-12 14084

-

高速adc四路光纤2020-04-24 4267

-

EV12AQ600/EV12AQ605数模转换器介绍2021-08-27 1520

-

AD7865:四通道、同步采样、快速、14位ADC数据表2021-04-29 1144

-

解读ADC采样芯片(EV10AQ190A)的采样(工作)模式(双通道模式)2023-02-22 5561

-

解读ADC采样芯片EV10AQ190A的工作模式2023-02-24 2650

-

ADS131M04四通道同步采样24位 Δ-Σ ADC数据表2024-07-19 1136

-

ADS131A0x双通道或四通道24位128kSPS同步采样Δ-Σ ADC数据表2024-07-23 744

全部0条评论

快来发表一下你的评论吧 !