高速ADC的正确布板、元件选择及布局指南

模拟技术

描述

本文详细介绍了通常应用于IF和基带的高速模数转换器(ADC)的正确布板、元件选择及元件布局。文中以高分辨率、高速数据转换器MAX12555系列为例,介绍了优化电路设计、正确高速布板、旁路和去耦技巧、热管理、元件选择及布局。

本文可作为高速数据转换器电路设计和布板建议的简明资源,是对高速数据转换器及其评估板数据资料中电路设计和PCB布板信息的补充。用户应根据其特定应用,仔细阅读所有可用资源,以使器件在特定应用中实现最优性能。文中以14位模数转换器(ADC) MAX12555为例,这些型号分别针对65Msps/80Msps/95Msps的采样速率进行了优化,适合所有IF和基带应用。

本文分为三部分:一般性建议、电路设计建议、布板建议。

一般性建议概要介绍了如何在应用中发挥器件的最佳总体性能,讨论了一般情况下器件外围元件的最佳布局,提出了有关物理PCB本身的建议。

电路设计建议介绍了最关键和最敏感引脚处元件的推荐值。

布板建议中详细介绍了外围元件布局,指出哪些元件应放在顶层,哪些应放在底层,同时还提供了有关PCB的附加信息。

请参考:

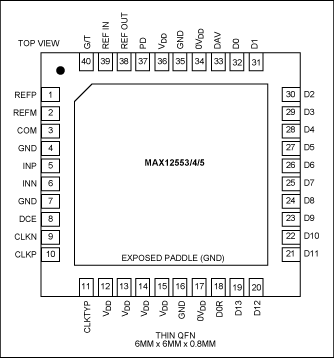

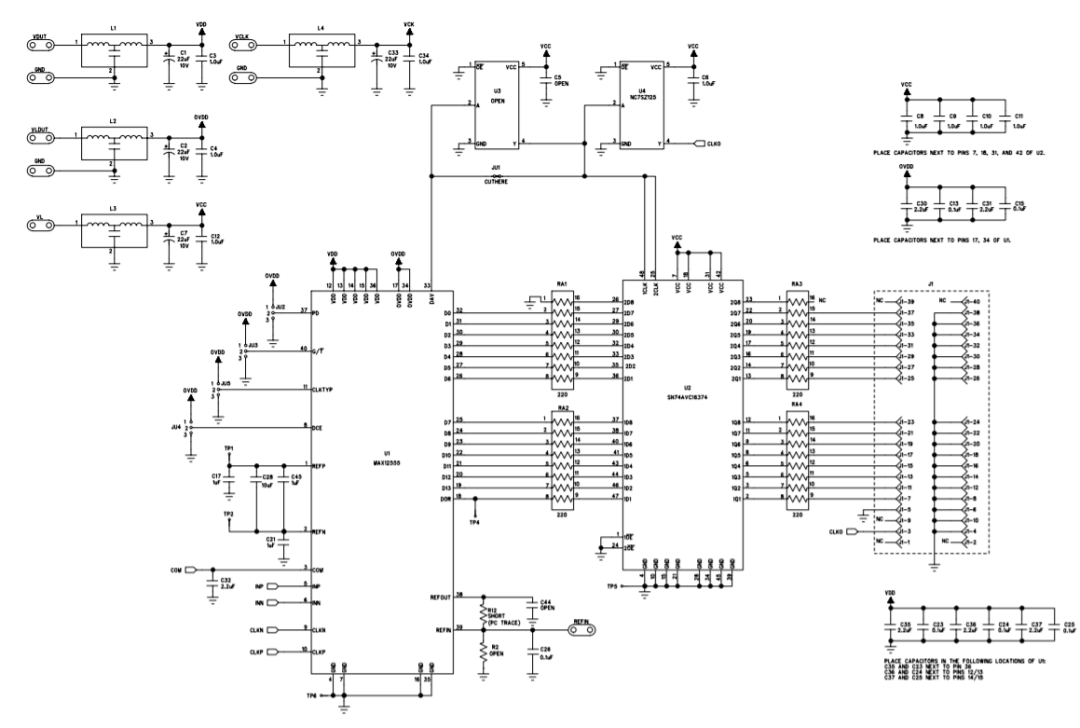

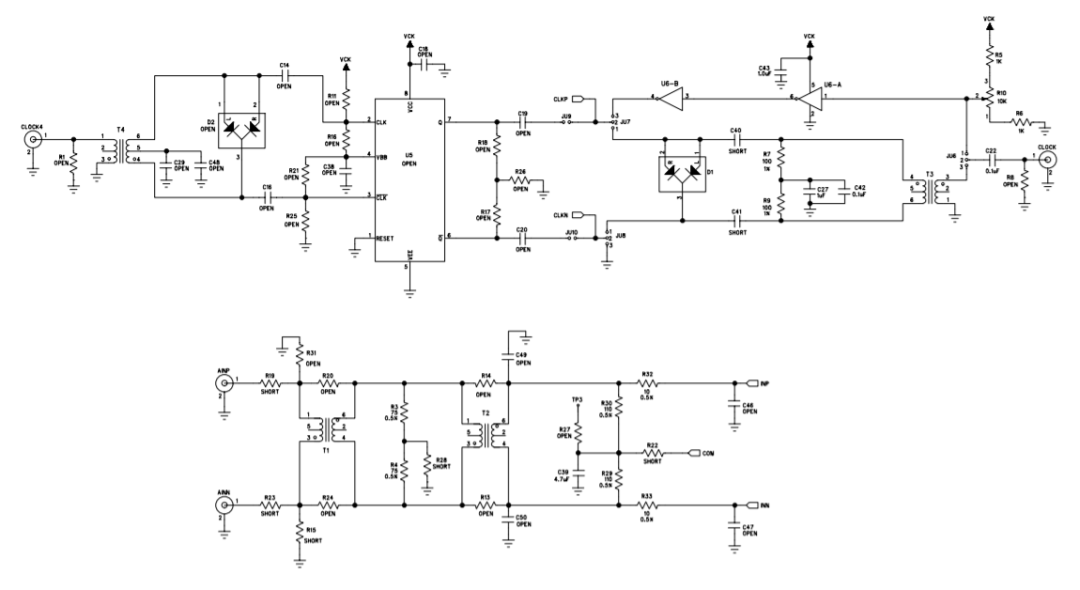

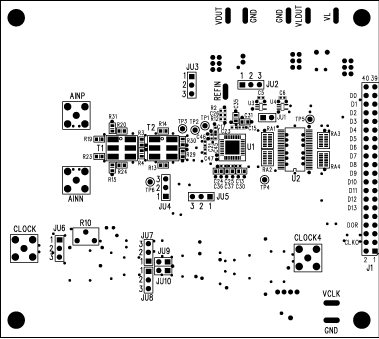

该系列ADC引脚排列见图1,引脚功能说明见表1。评估(EV)板提供多种选择,允许单端或差分时钟输入、单端或差分模拟信号输入、内部/外部基准等,所以评估板(见图2和图3)使用的外围元件和配置比正常应用中多。图4和图5为评估板顶层和底层的丝印及元件布局。

图1. MAX12555的引脚排列

表1. 引脚说明

| 引脚 | 名称 | 功能 |

| 1 | REFP | 正基准I/O。满幅模拟输入范围为±(VREFP - VREFN) x 2/3,REFP通过一个0.1µF电容旁路至GND。REFP与REFN之间并联一个1µF的电容和一个10µF电容。REFP和REFN间的1µF电容应与器件位于同一侧,并尽可能靠近器件。 |

| 2 | REFN | 负基准I/O。满幅模拟输入范围为±(VREFP - VREFN) x 2/3,REFN通过一个0.1µF电容旁路至GND。REFP与REFN之间并联一个1µF的电容和一个10µF电容。REFP和REFN间的1µF电容应与器件位于同一侧,并尽可能靠近器件。 |

| 3 | COM | 共模电压I/O。COM通过一个2.2µF电容旁路至GND。将2.2µF COM至GND的旁路电容尽可能靠近器件,可以放置在PCB另外一侧,通过1个过孔与ADC连接。 |

| 4, 7, 16, 35 | GND | 地。所有地引脚与EP相连。 |

| 5 | INP | 同相模拟输入。 |

| 6 | INN | 反相模拟输入。 |

| 8 | DCE | 占空比均衡器输入。DCE接低电平(GND)禁止内部占空比均衡器。DCE接高电平(OVDD或VDD)使能内部占空比均衡器。 |

| 9 | CLKN | 反相时钟输入。在差分时钟模式(CLKTYP = OVDD或VDD),差分时钟信号接在CLKP与CLKN之间。在单端时钟模式(CLKYP = GND),单端时钟信号接CLKP,CLKN接GND。 |

| 10 | CLKP | 同相时钟输入。在差分时钟模式(CLKTYP = OVDD或VDD),差分时钟信号接在CLKP与CLKN之间。在单端时钟模式(CLKYP = GND),单端时钟信号接CLKP,CLKN接GND。 |

| 11 | CLKTYP | 时钟模式定义输入,CLKTYP接GND时为单端时钟输入。CLKTYP接OVDD或VDD时为差分时钟输入。 |

| 12-15, 36 | VDD | 模拟电源输入。VDD连至3.15V至3.60V电源。VDD通过一个≥2.2µF的电容并联一个0.1µF电容旁路至GND。所有VDD引脚连至相同电位。 |

| 17, 34 | OVDD | 输出驱动器电源输入。OVDD可连至1.7V至VDD的电源。OVDD通过一个≥2.2µF的电容并联一个0.1µF电容旁路至GND。 |

| 18 | DOR | 数据超量程指示。DOR输出用来指示模拟输入电压超量程。DOR为高电平时,表明模拟输入电压超出范围。DOR为低电平时,表明模拟输入电压在量程以内。 |

| 19 | D13 | CMOS数字输出,第13位(MSB)。 |

| 20 | D12 | CMOS数字输出,第12位。 |

| 21 | D11 | CMOS数字输出,第11位。 |

| 22 | D10 | CMOS数字输出,第10位 |

| 23 | D9 | CMOS数字输出,第9位。 |

| 24 | D8 | CMOS数字输出,第8位。 |

| 25 | D7 | CMOS数字输出,第7位。 |

| 26 | D6 | CMOS数字输出,第6位。 |

| 27 | D5 | CMOS数字输出,第5位。 |

| 28 | D4 | CMOS数字输出,第4位。 |

| 29 | D3 | CMOS数字输出,第3位。 |

| 30 | D2 | CMOS数字输出,第2位。 |

| 31 | D1 | CMOS数字输出,第1位。 |

| 32 | D0 | CMOS数字输出,第0位(LSB)。 |

| 33 | DAV | 数据有效输出。DAV是输入时钟经占空比补偿校正后的单端输出,DAV的典型应用是将ADC的输出数据锁存至后端的数字电路。 |

| 37 | PD | 关断输入。将PD强制置高,器件进入关断模式。正常工作时PD置低。 |

| 38 | REFOUT | 内部基准电压输出。采用内部基准电压时,REFOUT直接连至REFIN,或通过一个电阻分压器设定REFIN输入电压。REFOUT通过一个≥0.1µF的电容旁路至GND。 |

| 39 | REFIN | 基准电压输入。在内部基准模式和带缓冲的外部基准模式,REFIN通过一个≥0.1µF的电容旁路至GND。此时,VREFP - VREFN = VREFIN x 3/4。在无缓冲的外部基准模式下,REFIN连至GND。 |

| 40 | G/ /T | 输出格式选择输入。G/ /T接GND为二元补码格式输出。G/ /T接与OVDD或VDD为格雷码格式输出。 |

| - | EP | 裸焊盘。通过裸焊盘实现与地的低电感连接。将EP连至GND以保证设计性能。PCB顶层和底层的地平面通过多个过孔连接。 |

一般性建议

一般而言,采用带整体地层和电源层的多层PCB可获得最佳信号完整性。

MAX12555需要高速布板技术,包括裸焊盘可靠接地。

保持MAX12555模拟部分的内层地平面完整性,空隙(void)必须最少。过孔交错排列,保持非常小的过孔间隙,将空隙减少到最低程度。另外,在关键元件下方应布设完整的地,尤其是接引脚1和引脚2的REF电容、接引脚3 的COM旁路电容、接模拟信号输入引脚5和引脚6的小电容。

将不同的输入和输出信号限定在不同的PCB层,如:所有模拟信号输入位于X层、所有数字信号输出位于Y层、所有时钟信号位于Z层等。尽量将每一层夹在两层地之间或使用微带线。

使用与地相对的电源平面来减小信号感应,将总体噪声降至最低。功率走线应宽一些,以降低IR压降和电感。

对于GND和VDD (电源线),建议采用多个18mil规格的过孔。

MAX12555的所有GND和裸焊盘(EP)必须连至同一地平面。MAX12555依靠EP实现与地的低电感连接,通过多个过孔连至指定地层。所需的过孔数量取决于孔的尺寸。作为指导原则,Maxim建议采用5 x 5 (总共25个)矩阵的13mil规格的过孔。最少需要12个过孔。

MAX12555最关键的输入、输出是模拟信号输入、基准引脚、时钟和数字输出。最关键的引脚是1、2、3、5、6、9、10、38和39。

ADC周围连接旁路电容和关键电容的走线应尽可能的宽,以减小电阻和电感。建议采用宽度大于或等于10mil的走线。如果元件无法直接连至地平面,则其接地线应尽可能宽。这还应包括PCB设计中的接地热焊盘。

如果旁路电容使用热焊盘与GND连接,每个旁路电容使用两个热焊盘,GND端使用过孔以减小电感。

高速数字信号走线应远离敏感的模拟信号线、时钟线、REFP (引脚1)和REFN (引脚2)。

所有信号线(包括REFP和REFN)都应尽可能短并且避免90°折线。

确保差分模拟输入网络对称,并且所有寄生效应是均衡的。

所有旁路电容应尽可能靠近器件,最好在PCB同侧,可采用表贴器件减小电感(在下面的布板建议中有更详细的介绍)

通常所有GND旁路过孔尺寸应为18mil。

为实现最佳性能,需要独立的模拟和数字电源。

MAX12555可接受差分或单端时钟输入。

MAX12555可接受差分或单端模拟输入,差分输入可提供最佳性能。

EP作为器件的主要接地途径,必须正确连接到指定地平面。

使用地线“隔离”ADC电路和PCB上的其它任何相邻电路。例如:一个PCB上有多个ADC时,利用地平面将每个ADC的相关电路隔离开来。

电路设计建议

(引脚1,REFP):通过一个位于PCB顶层的高频陶瓷电容(最大1.0µF)将REFP旁路至GND。所有REFP走线应尽可能短。

(引脚2,REFn):通过一个位于PCB顶层的高频陶瓷电容(最大1.0µF)将REFP旁路至GND。所有REFP走线应尽可能短。

(引脚1,REFP和引脚2,REFN):REFP和REFN之间并联两个容值分别为10µF和1µF的高频陶瓷电容。与引脚1和引脚2连接的任何电容都必须具有良好的高频性能。

(引脚3,COM):COM通过一个高频性能良好的2.2µF陶瓷旁路至GND。

(引脚5 & 6,INP & INN):为获得最佳总体AC性能,这些引脚与地之间都应接并联电容,容值依应用而定,范围为5.6pF到12pF。这些电容值可被包含在任何驱动ADC的抗混叠滤波器谐振电路中,并且应被放在电路板顶层。

(引脚12-15,36,VDD):使用高频性能良好的0.1µF和2.2µF陶瓷电容各一个并联,将VDD旁路至GND。

(引脚17,34,OVDD):使用高频性能良好的0.1µF和>2.2µF陶瓷电容各一个并联,将OVDD旁路至GND。

(引脚19-32,D13-D0):包括数据输出引脚与各自负载的串联电阻。这些电阻可限制从输出逻辑驱动器进入芯片内部GND的高频边沿电流。选定的阻值与负载电容一起产生的RC时间常数约为1ns。Maxim公司采用非常小而且低成本的电阻阵列,基本是多只0402电阻构成一组。评估板使用的是Panasonic公司的EXB-2HV-221J。

(引脚38,REFOUT):采用内部基准时,REFOUT直接与REFIN连接,或通过一个电阻分压器设定REFIN输入电压。REFOUT通过一个高频性能良好、≥0.1µF的陶瓷电容旁路至GND。

(引脚39,REFIN):在内部基准模式和带缓冲的外部基准模式,REFIN通过一个 ≥0.1µF的电容旁路至GND。在无缓冲的外部基准模式下,REFIN连至GND。

图2. 评估板器件原理图

图3. 评估板模拟部分原理图

布板建议

将MX12555放置在PCB顶层。

接着,在引脚1与引脚2之间放置一个1µF电容。该电容应位于PCB顶层,并且尽量靠近这两个引脚。REFP和REFN (引脚1、2)之间跨接的电容应在制造公差允许范围内尽量靠近DUT。

下一步,放置引脚1至地和引脚2至地的旁路电容。这些电容应尽可能靠近共用的1µF电容,同时用过孔将电容的GND一端与指定模拟地相连(也与器件EP相连)。如果第二层有一个地平面,则该地平面应延伸到这三个器件的下方以减少引脚1和引脚2上的电感。对于REFP和REFN旁路电容的接地过孔,Maxim公司采用18mil的钻孔直径,选择较大尺寸是因为过孔电镀后会减小3mil。孔的最终尺寸应为约为15mil。

接下来,在引脚1与引脚2之间放置一个10µF电容。如果顶层没有足够空间安装此电容,也可以像评估板那样把它放在PCB底层,利用过孔传输信号。该电容与器件引脚间的走线总长应减至最小。

与引脚1和引脚2连接的走线应尽可能短,并且应当是匹配的。即:它们应当是对称的,而且长度应相同。

接着,放置引脚3至GND的2.2µF电容,尽可能靠近器件。如果需要,该电容可放在PCB底层,采用13mil过孔与引脚3连接。走线应尽可能短。

所有GND引脚(引脚4、7、16和35)应与MAX12555器件下方的覆铜相连。

应遵循以下原则:正确连接MAX12555的EP与指定接地层(最好是第二层),需要使用足够多的过孔以降低电感,过孔数量取决于孔的尺寸。作为指导原则,Maxim公司建议采用5 x 5 (总共25个)的13mil过孔矩阵,最小过孔尺寸应为12mil。

模拟输入应是均衡的。也就是说,从驱动源(放大器和滤波器等)到差分输入端的走线应该等长,元件布局应相互对称,这样,所有的寄生参数才会均衡。走线长度应尽可能短,以降低电感、减小干扰。

将输入引脚5和引脚6的旁路电容放置在PCB顶层靠近器件引脚的位置,尽量减小走线长度。

应使用某一层(最好是第二层)作为可靠的模拟接地层,推荐使用过孔阵列将其与MAX12555的EP连接。

时钟布线建议(引脚9和引脚10):

时钟输入与模拟输入和基准一样敏感。应像对待模拟信号那样对时待时钟信号。避免将时钟线靠近任何数字输出信号线。如果板上有多个ADC,则需隔离时钟线对,以尽量降低噪声并减小来自其它ADC的干扰。时钟信号线不应与数字输出信号线布在同一层。如果布在同一层,应尽量使这两类信号线之间保持较大间距,并在这两类信号线之间布隔离的GND,以降低可能产生的任何耦合。 建议采用典型值为1.4VP-P的差分时钟输入,这是器件的特性之一。但时钟输入信号摆幅的峰值并不是最重要的,保证快速上升和下降时间的摆率更重要。另外,内部差分放大器可提供增益,对信号进一步整形。评估板采用一个中心抽头变压器放大时钟输入,以确保快速上升和下降时间,然后再用二极管将摆幅限制在1.4VP-P。对于单端时钟信号来说,边沿应较陡,并且满足数据资料规定的最高和最低电压要求,即逻辑高电平最低为0.8VDD,逻辑低电平最高为0.2VDD。时钟共模电压(1/2VDD)由内部提供。推荐的接口电路/驱动器逻辑:任何逻辑输入,包括CMOS、LVPECL、LVDS都可用于驱动时钟输入。对于高频输入信号的应用,建议采用非常高速的LVPECL时钟分配电路,如MAX9320 PECL缓冲器。

引脚12-15,36,VDD:最好将0.1µF的旁路电容放在器件引脚旁。

引脚17,34,OVDD:最好将0.1µF的旁路电容放在器件引脚旁。

数据线(引脚19至引脚32):对于输出数椐引脚,从ADC到缓冲器或负载IC的走线应尽量短。串联电阻尽可能靠近ADC,为确保最佳性能,总负载电容应等于10pF。而保证缓冲器或负载IC的地与MAX12555的EP可靠连接,对于实现最佳的AC性能非常重要。如果将数椐线布在顶层或底层(采用微带线技术),则相邻层必须是地层,以形成有效传输线。如果将数据线布在内层(采用带状线技术),则其相邻各层必须为地电位以形成有效传输线。数字信号输出应紧密排列在单一总线内以控制电流回路。另外,尽量减小MAX12555与数字负载间的接地层空隙(由数字信号过孔产生),当数据线进入内层时,过孔应交错排列。

REFOUT和REFIN (引脚38和引脚39)的旁路电容必须靠近器件引脚,使用短的走线直接与器件接地层相连。

图4. 评估板顶层丝印和元件布局

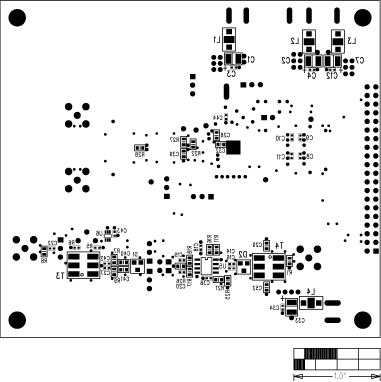

图5. 评估板底层丝印和元件布局 总结:本应文是器件和评估板数据资料的补充,用户可在应用中根据提供的建议优化器件性能。

审核编辑:汤梓红

-

AN 224:高速电路板布板指南2025-07-14 474

-

高速布局指南2023-07-24 602

-

高速接口布局指南2023-04-14 1391

-

正确的布局和元件选择可控制EMI2023-03-10 2241

-

高速电路板布板指南-Altera.zip2022-12-30 653

-

高速ADC FMC转接器评估板布局板(765KB,zip)2021-06-04 788

-

AN-1142: 高速ADC PCB布局布线技巧2021-03-20 1523

-

电路设计如何正确布局元件以降低EMI干扰2021-02-27 3107

-

高速PCB布板原则2015-12-25 1368

-

印刷线路板元件布局及结构设计2011-11-24 2717

-

正确的布局和元件选择是控制EMI的关键2009-04-30 395

-

正确选择输入网络,优化高速ADC的动态性能和增益平坦度2009-04-16 723

全部0条评论

快来发表一下你的评论吧 !