高速数字电路设计规则十七条

电子说

描述

随着信号速率的提升,电子产品设计也是越来越复杂。无论设计的能力有多强、设计经验多丰富,总会出现一些意向不到的问题。所以很多公司,都会有一些设计规则,让大家在设计中有据可依,也可以在设计完成之后作为checklist,一步一步的检查。下面列举了一些在信号完整性以及电源完整性中需要检查的点。

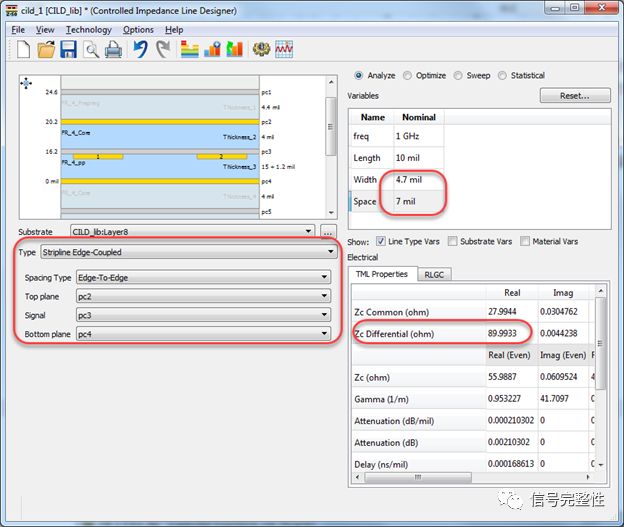

1、阻抗是否满足设计要求,这主要根据传输线的结构检查确认。不同的总线有不一样的需求。

2、高速信号线不要跨分割布线。

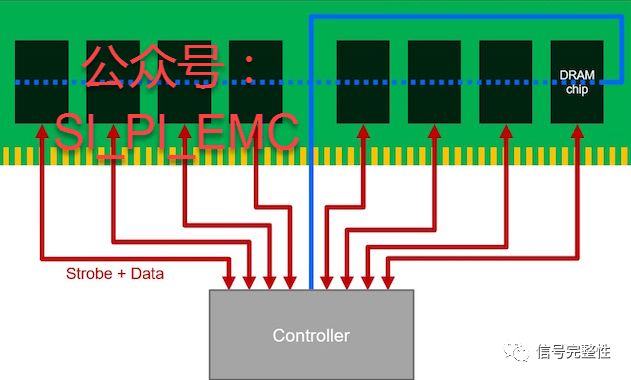

3、拓扑结构是否满足设计要求,对于SerDes总线,基本都是采用的点对点的设计结构,但是对于Memory,会涉及到T-type和Fly-by结构的选择,以及拓扑结构中每一段传输线的结构。

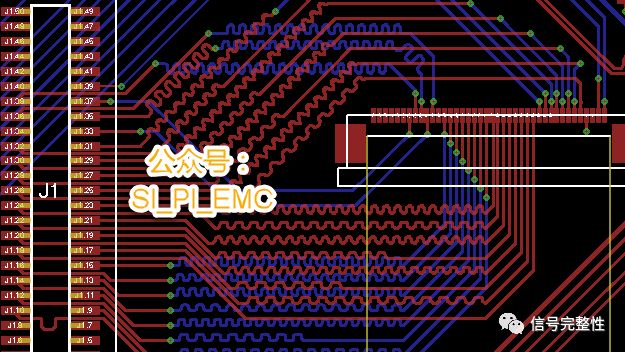

4、差分对内等长是否满足要求。对于速率特别高的总线,尽量满足等相位或者等时的要求。

5、对于特定的总线,其对与对之间等长是否满足要求。

6、高速信号网络不要布在板边,在比较大的散热通道附近也不要有高速信号线。

7、信号线与信号之间的距离是否足够大,使串扰足够小。

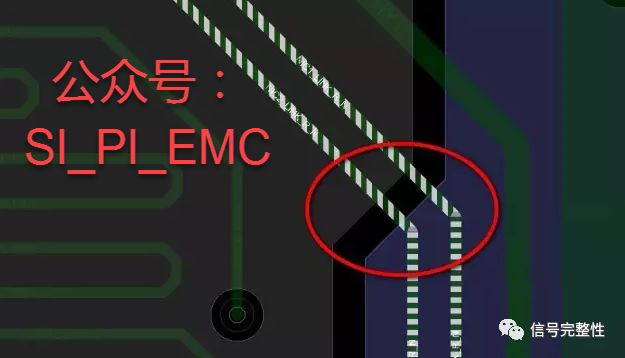

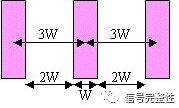

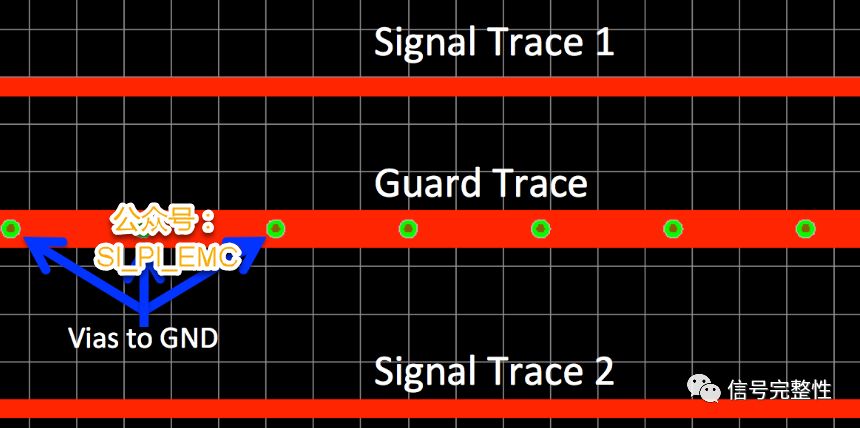

8、如果要给高速信号网络包地线保护,那么要有足够的距离(3W),避免因为包地导致新的信号完整性问题。

9、发送端与接收端的信号线距离尽量远,能分层布线最好。

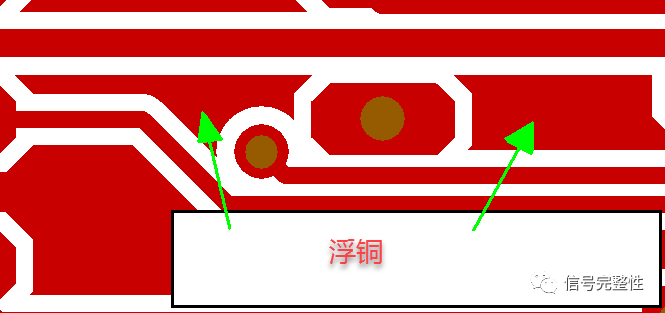

10、在高速电路的PCB板中不要出现浮铜,要么去掉,要么在浮铜上加GND via。

11、高速信号网络的via不易过多,一般除了BGA或者Connector处,其它区域不超过1个,最差不超过2个via,同时要优化via到比较合适的大小。

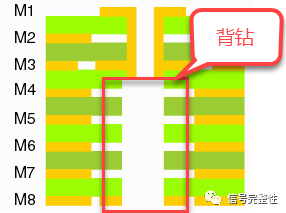

12、观察高速信号的stub是否足够短,是否需要使用Back-drill。

13、高速信号线在换层时,其via附近是否有伴随GND Via。

14、如果信号线有冗余设计,要确保传输线的stub要足够短,尽量减少信号完整性问题。

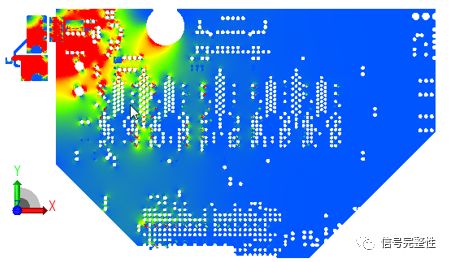

15、电源平面的设计是否满足通流的要求。

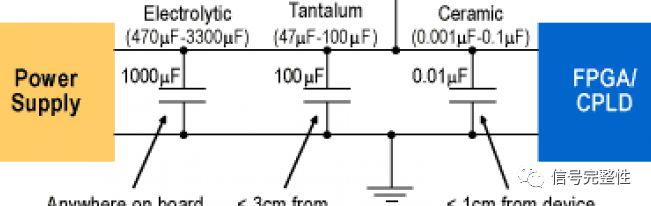

16、去耦电容的摆放是否合适,一般都是越小容量的电容越靠近芯片的摆放。

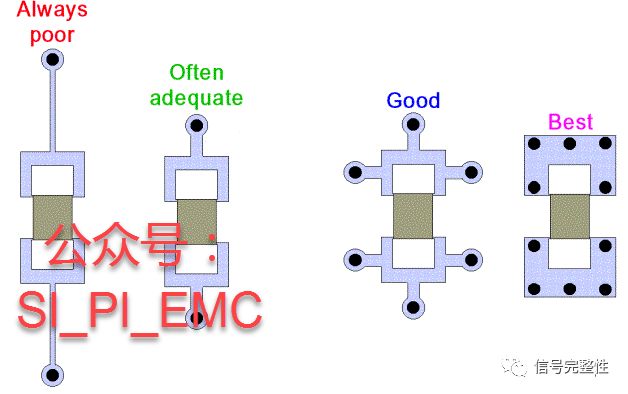

17、去耦电容的出线是否满足短而粗的要求。

以上只是之前做产品时做的关于高速产品设计简单SI部分的checklist。对于具体的产品和总线都有布线和结构等具体的要求。

不管是设计工具,还是仿真工具都在朝着越来越方便高效的方向发展。这样工程师在设计过程中都可以方便地使用工具进行仿真验证并检查设计的是否满足要求。

审核编辑:汤梓红

-

高速数字电路设计教材-华为.zip2022-12-30 776

-

高速数字电路设计教材-华为2022-06-13 1217

-

高速数字电路设计的基本要求是什么2021-04-27 2009

-

高速数字电路设计-华为2021-04-21 1141

-

高速数字电路设计方案2019-04-11 4533

-

高速数字电路设计大全2017-01-17 1145

-

高速数字电路设计及EMC设计2015-08-04 4484

-

华为《高速数字电路设计教材》2014-09-01 30118

-

高速数字电路设计教程2010-06-23 1199

-

数字电路设计2009-08-26 3106

-

高速数字电路设计2007-10-16 3461

全部0条评论

快来发表一下你的评论吧 !