EDA技术探索之窄沟道效应与反窄沟道效应

EDA/IC设计

描述

2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自主研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第10期的特别内容——窄沟道效应与反窄沟道效应,下面就跟着小编一起来开启今天的探索之旅吧~

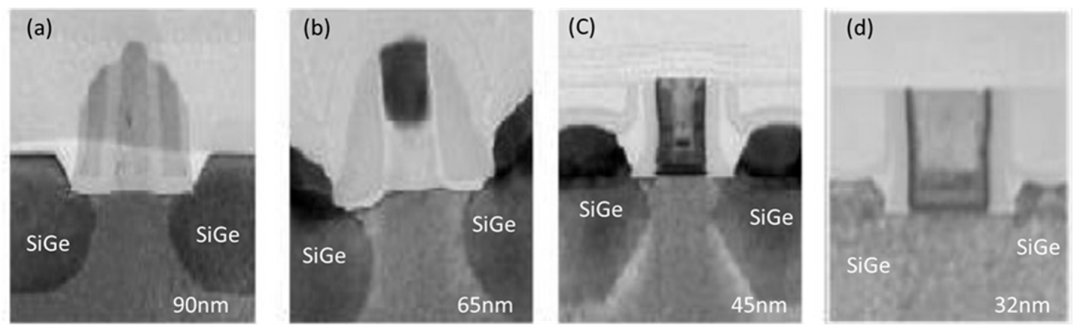

一般我们看到的MOSFET大多是这样的。

Intel 90nm-32nm 器件照片:来自Xiao, H. 3D IC Devices. In Technologies, and Manufacturing; Society of Photo-Optical Instrumentation Engineers (SPIE): Bellingham, WA, USA, 2016

从这个方向上包括了尽可能多的、我们感兴趣的信息,比如栅极(多晶硅,金属)、侧墙、源漏和沟道等等。但是实际上,集成电路和器件是一个非常复杂的系统。从更大视角俯视的角度来看,是这样子的。

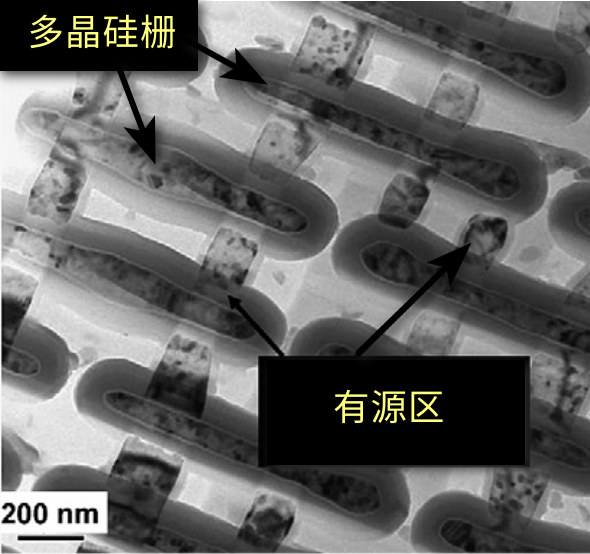

集成电路俯视照片:来自R.S. Rai, S. Subramanian / Progress in Crystal Growth and Characterization of Materials 55 (2009) 63e97

其中栅极方向与有源区方向呈垂直交错,中间白色的区域就是隔离区,或称为场区。我们最常见的照片是沿着有源区方向做截面的,如果沿着栅极方向做截面,则可以看到完整的沟道和场氧化层的截面。

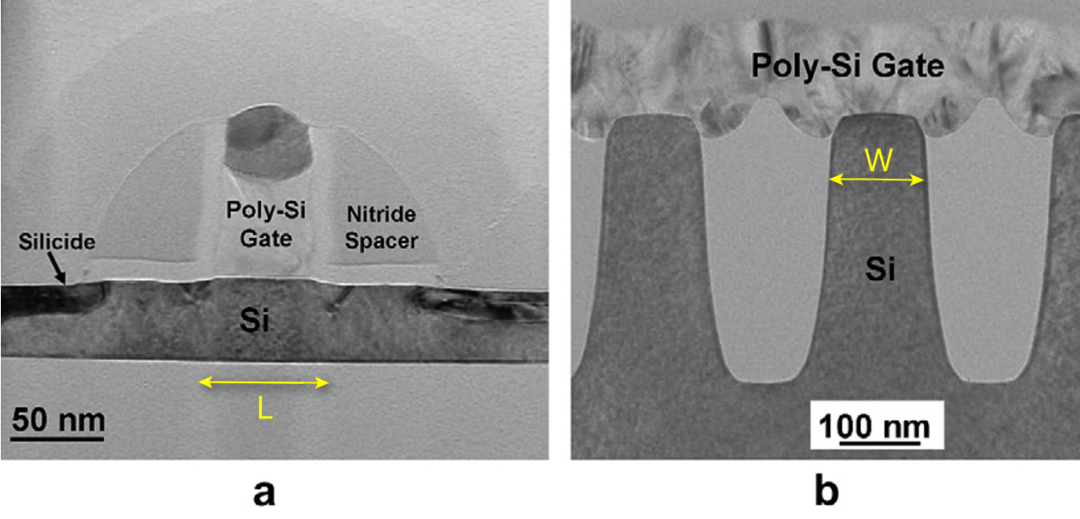

MOS器件剖面图:来自R.S. Rai, S. Subramanian / Progress in Crystal Growth and Characterization of Materials 55 (2009) 63e97

从上图a中,我们可以读到“沟道长度”,而从b中我们可以读到“沟道宽度”。实际上的沟道宽度往往要大于沟道长度,有些时候甚至是远远大于。这与我们平时把矩形的长边长度叫“长度”,短边长度叫“宽度”的习惯不同。

当MOSFET微缩时,更复杂的物理效应往往会凸显出来。对于沟道长度的减小,我们称为“短沟道效应“,包括DIBL,源漏穿通等等。同样的情况在沟道宽度上也有对应,一般称为NWE(Narrow Width Effect),中文称为”窄沟道效应“或”窄宽度效应“。

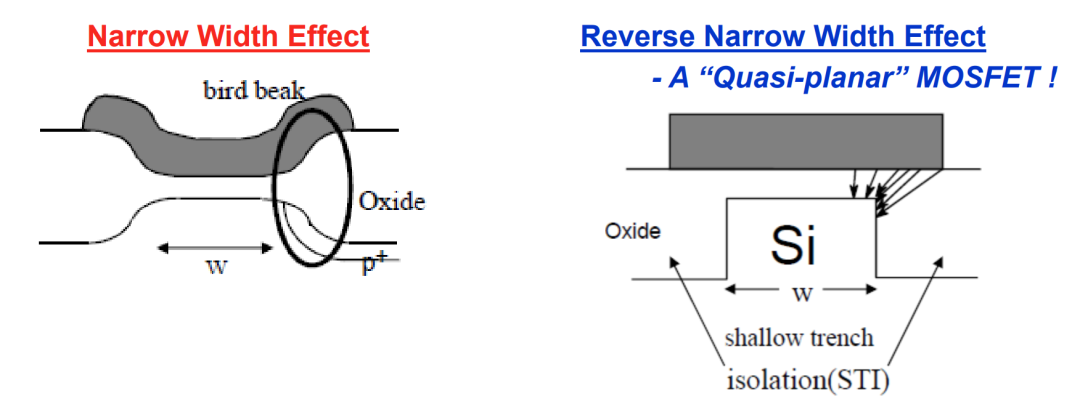

在沟道宽度很大的时候,沟道边缘对于整体性能的影响较小,可以忽略不计。当沟道长度进入亚微米时代后,沟道宽度也相应地缩短了很多,NWE变得显著起来。NWE对于器件的影响主要体现在阈值电压上。基于历史发展脉络,早期基于LOCOS隔离工艺的器件上,NWE会引起阈值电压的上升。而器件隔离方式进入STI时代之后,NWE反而会引起阈值电压的下降,由于与之前表现的方向相反,所以又被称为反向窄沟道效应,INWE(Inverse Narrow Width Effect)。

无论是NWE,还是INWE。其本质都是沟道边缘,场氧化层和栅极共同作用的寄生效应。其与场氧化层的形态,沟道的掺杂和应力都有关系。因此会表现出比较复杂的行为。

NWE和RNWE示意图:来自Lecture Notes, Advanced Topics in Semiconductor Technology - Three-Dimensional Transistor Technologies, UC Berkeley

基于对NEW的研究,可以有一系列的方式对其进行调控,从而尽量减小其实际的影响。

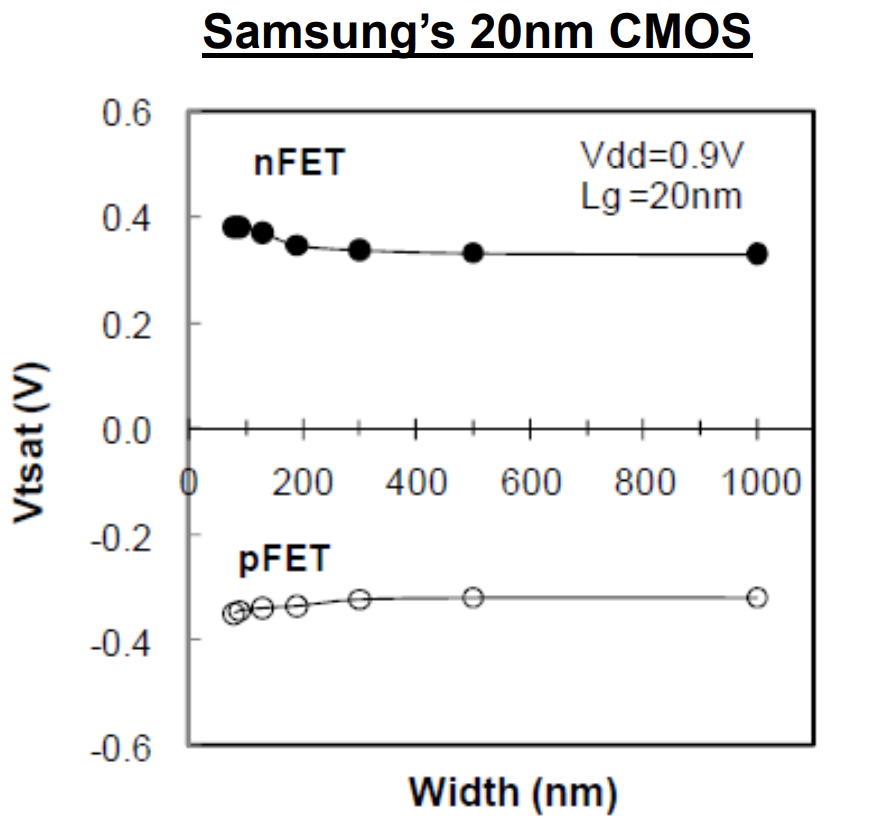

三星20nm CMOS工艺NWE:来自“Bulk Planar 20nm High-K/Metal Gate CMOS Technology Platform for Low Power and High Performance Applications,” IEEE International Electron Devices Meeting Technical Digest, pp. 350-353, 2011.

而在另一方面,鲁迅先生说过,如果不能改变它,就可以尝试利用它。在已经NEW效应的情况下,从器件设计的角度也可以利用这一特性对物理设计进行一定的修改,从而在一定程度上优化电路的性能。

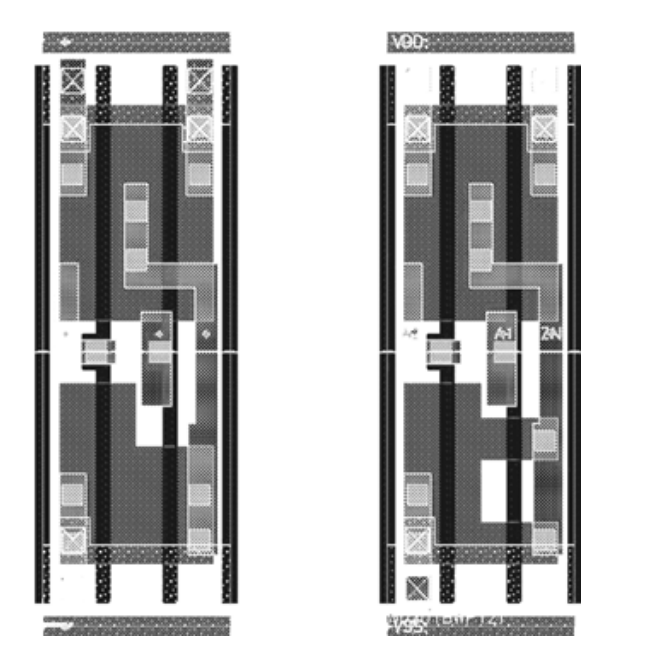

根据INWE对与非门版图的修改:来自郑凯磊等 40nm工艺下反向窄沟道效应对VLSI电路设计的影响

编辑:黄飞

-

短沟道二维晶体管中的掺杂诱导辅助隧穿效应2024-12-06 2382

-

什么是N沟道场效应管和P沟道场效应管2024-09-23 6754

-

一文解析离子注入的沟道效应2024-02-21 6663

-

结型场效应管和金属氧化物场效应管的分类2024-01-30 18312

-

离子注入涉及到的隧道效应为什么需要7°角?2024-01-08 3733

-

场效应管怎么区分n沟道p沟道2023-09-02 15518

-

[5.3.1]--反常短沟道效应4.1.4窄沟道效应4.1.5漏感应势垒_clip001jf_75936199 2023-05-22

-

[5.4.1]--沟道效应学习电子知识 2022-11-24

-

半导体器件物理:窄沟道效应#半导体学习电子 2022-11-10

-

FD-SOI与深度耗尽沟道DDC MOS器件的详细资料介绍2019-04-10 3349

-

N沟道耗尽型MOS场效应管的结构与原理2015-06-15 5175

-

结型场效应管(N沟道JFET)工作原理:2012-08-13 6845

-

MOS管短沟道效应及其行为建模2011-07-04 5931

全部0条评论

快来发表一下你的评论吧 !