双通道、电压输出DAC功耗极低

描述

本设计笔记显示了一个电路,该电路修改了一个双通道、电压输出数模转换器(DAC),以节省功耗,并采用20V电源消耗小于5μA的电流。该电路可用于慢速或静态应用中的可编程电压生成,例如微功耗仪器中的失调归零。

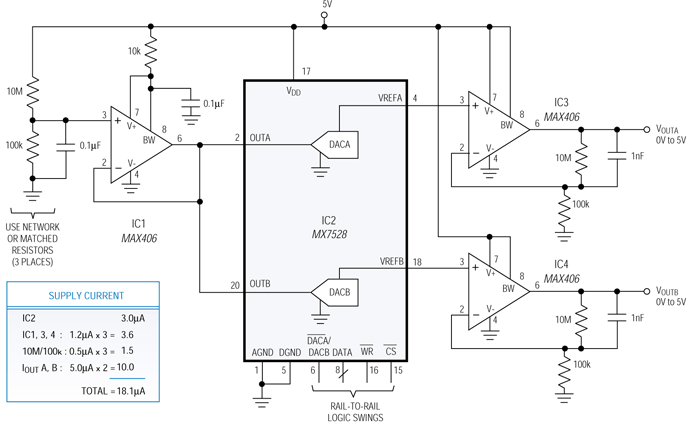

下图所示的双通道电压输出DAC采用多种省电技巧组合,从20V电源吸收小于5μA的电流。该电路适合慢速或静态应用中可编程电压生成的需求,例如微功耗仪器中的失调归零。

该双通道DAC电路提供两个独立的8位DAC,具有电压输出和一个公共基准,采用20V电源吸收的电流小于5μA。

电流输出DAC通常通过路由I的补码来浪费功率外接地。图中的电路通过在反向电压开关模式下操作每个DAC来避免功耗浪费,在该模式下,基准电压施加到通常标记为I的引脚上外.

本电路中的OUT引脚具有恒定且相对较低的输入阻抗(11kΩ)。为了减小输入电流,基准电压被分压100 (从5V到50mV),因此仅向每个DAC输入提供5μA电流。信号电平通过每个输出放大器中的100补偿增益恢复。廉价的 10MΩ/100kΩ 电阻网络是需要多个 100:1 衰减器的不错选择。虽然精度仅为2%,但它们的匹配和跟踪比分立电阻器要好得多。

更大的缩放是不切实际的,因为所示输出放大器的失调为0.5mV (最大值)。放大100时,这些失调会产生±1%(0.05V)的最差输出误差。误差在整个温度范围内是恒定的,但在40°C范围内由于漂移引起的额外误差通常为±<>/<> LSB。图中所示的微功耗输出放大器因其低电源电流而被选中,典型功耗为IDD仅 1μA。

最小化总电流消耗的最后一个要求是确保施加到IC1数字输入的逻辑信号摆幅在每个供电轨的0.2V以内。指定的最大值 IDD对于该条件,整个温度为100μA,但此规格(与大多数CMOS I一样)DD收视率)极其保守。我DD对于轨到轨摆动可以忽略不计,但随着摆动接近 TTL 水平,摆幅会急剧上升。

审核编辑:郭婷

-

DAC7562-Q1 12位、双通道、低功耗、超低毛刺、缓冲电压输出DAC技术手册2025-11-12 827

-

DAC7563T 12 位双通道电压输出数模转换器(DAC)技术文档总结2025-11-11 978

-

DAC8552双通道、电压输出数模转换器(DAC)数据表2024-07-26 893

-

TLV5618A双通道12位电压输出DAC数据表2024-07-18 563

-

DAC82002 16位、低毛刺脉冲、双通道电压输出、非缓冲DAC数据表2024-07-15 460

-

DAC53xAxW具有I2C或SPI的10位三通道和双通道电压输出和电流输出智能DAC数据表2024-07-12 535

-

UG-979:AD5338R 10位双通道电压输出DAC评估板2021-05-13 824

-

UG-973:AD5322 12位双通道电压输出DAC评估板2021-05-12 1118

-

DAC856X,DAC816X和DAC756X低功耗电压输出双通道数模转换器资料概述2018-05-18 1908

全部0条评论

快来发表一下你的评论吧 !