基于UPF的低功耗数字后端设计实训课

描述

基于UPF的低功耗数字后端设计技术是芯片设计中非常重要的一环,现在越来越多的公司和岗位对此有要求。如果想从事相关领域的工作,掌握基于UPF的低功耗数字后端设计技术是非常有必要的!

本次,E课网特推出全新的《基于UPF的低功耗数字后端设计实训课》,课程采用基于矿机的后端项目,项目实践从前端的RTL代码,经过逻辑综合,布局布线和静态时序分析,帮助大家掌握基于UPF的低功耗后端实现技术,完成进阶之路!快快报名参加吧~

一、项目介绍

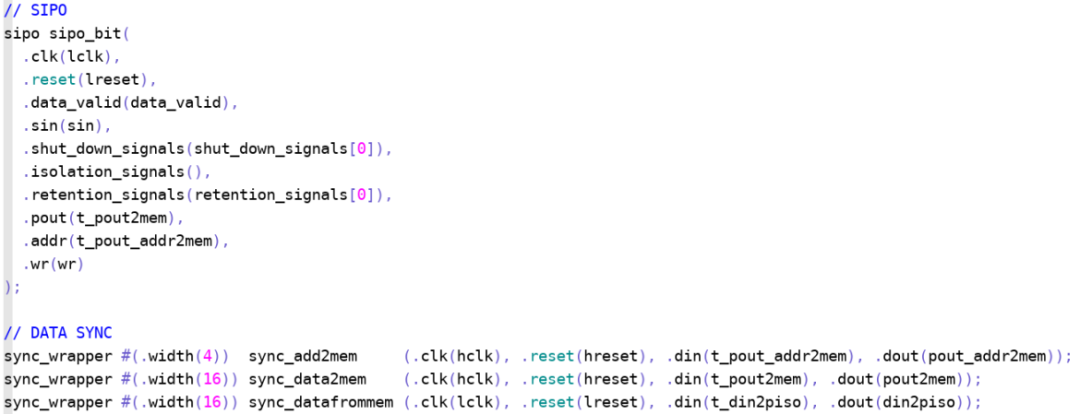

工艺介绍:28nm工艺;RTL代码示例:

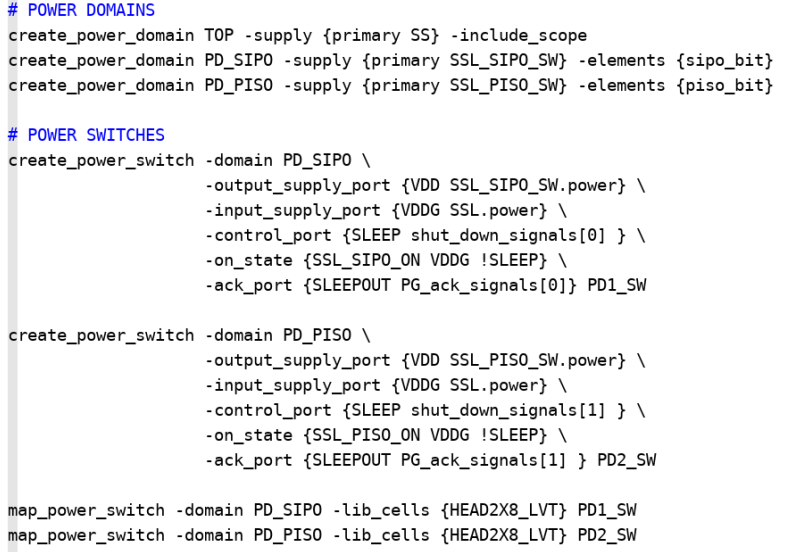

UPF代码示例:

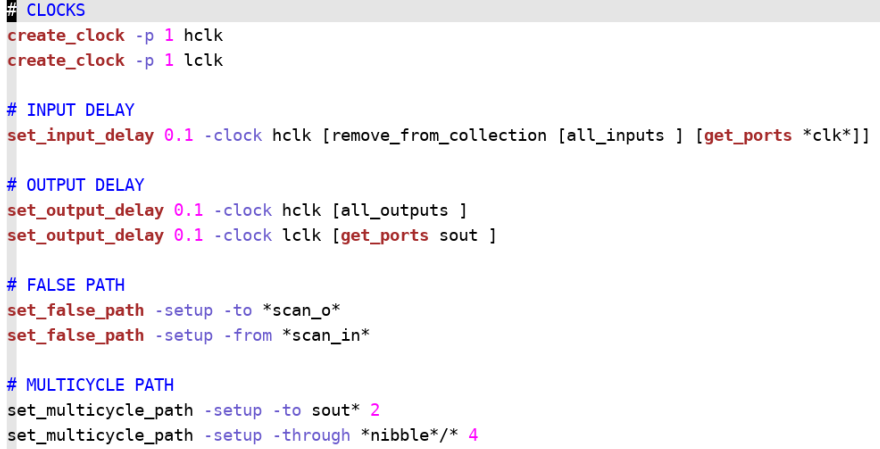

DC:sdc代码示例:

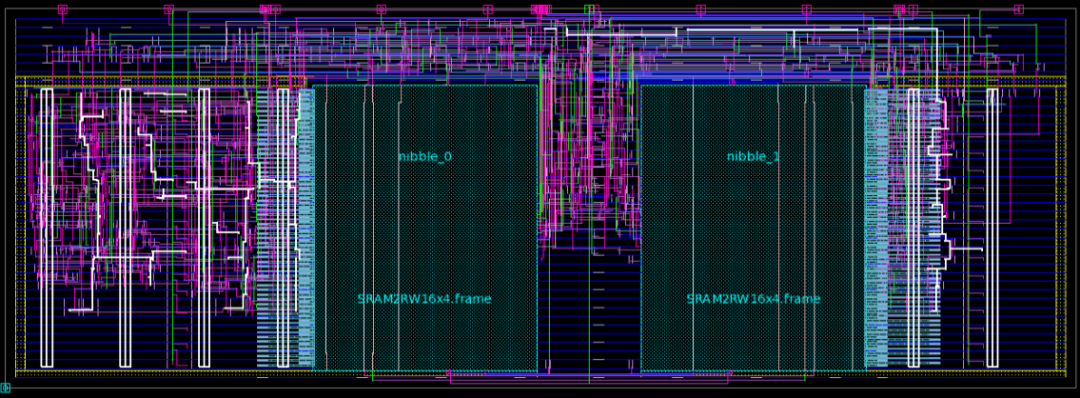

PR:

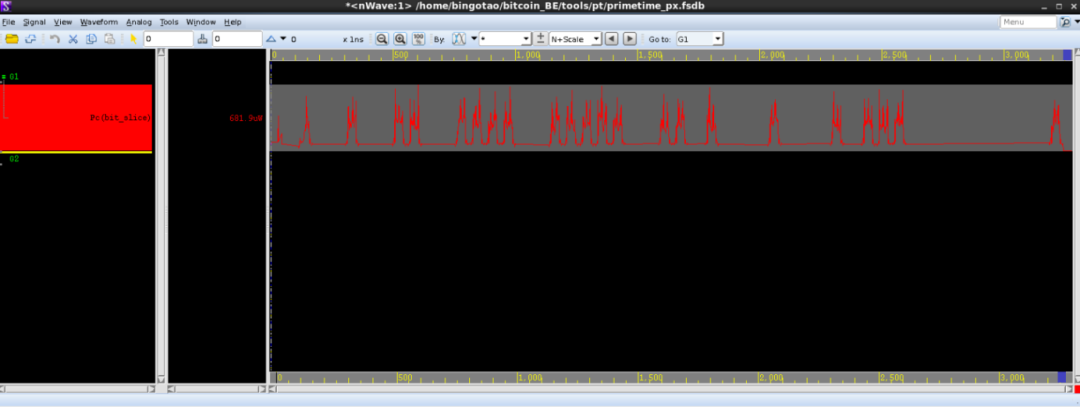

PT PX功耗峰值分析:

二、低功耗简介

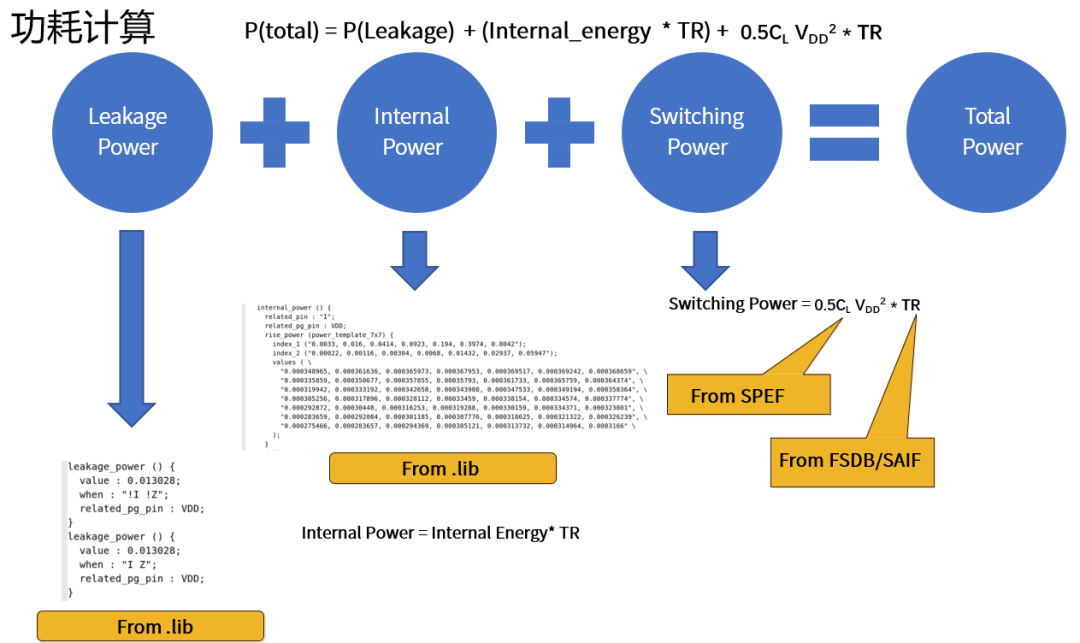

现如今,手机电脑等电子设备已经成为了大家日常生活中的必需品,而我们最关心的,除了性能之外,可能就是它们的续航了。因为电子设备如果功耗过大,就会产生更多的热量,设备过热便会影响器件工作,手机电脑会因此卡顿。因此,低功耗设计就显得至关重要。CMOS电路中功耗分为静态功耗和动态功耗,动态功耗是由内部功耗和开关功耗组成的。其中动态功耗的分析依赖于前端VCS功能仿真提供的包含Switching Activity信息的FSDB波形文件或者SAIF文件。

在数字芯片设计中,低功耗方法学是一项非常重要的学习内容,可以利用UPF对power domain进行系统性的管理,从而提高芯片的续航能力。

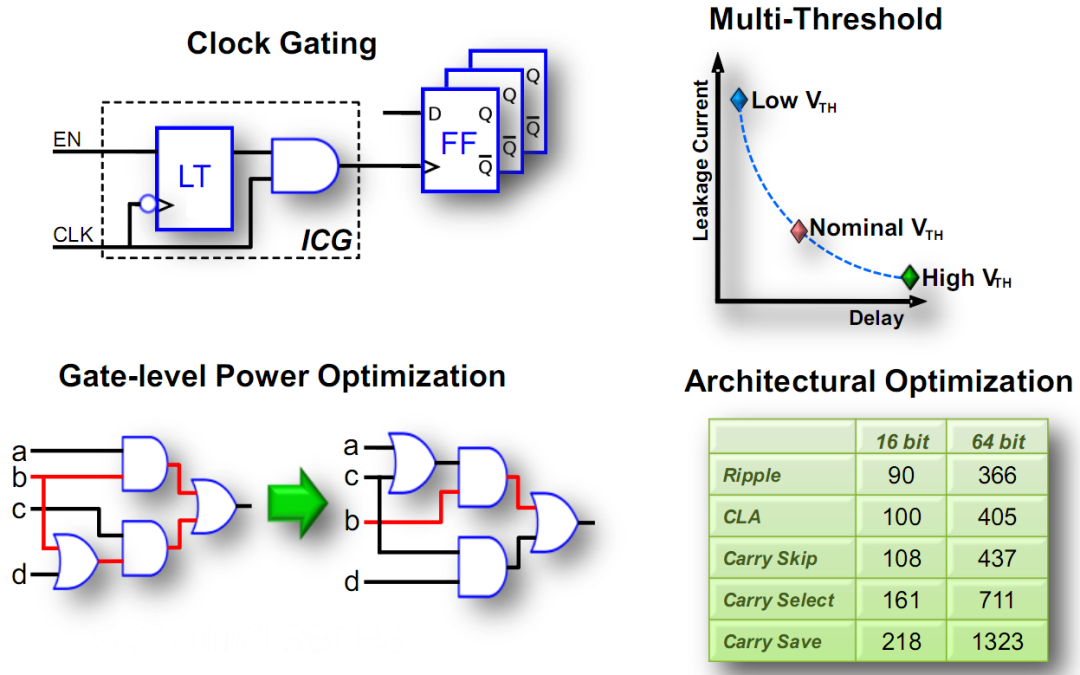

芯片设计中主流的低功耗技术

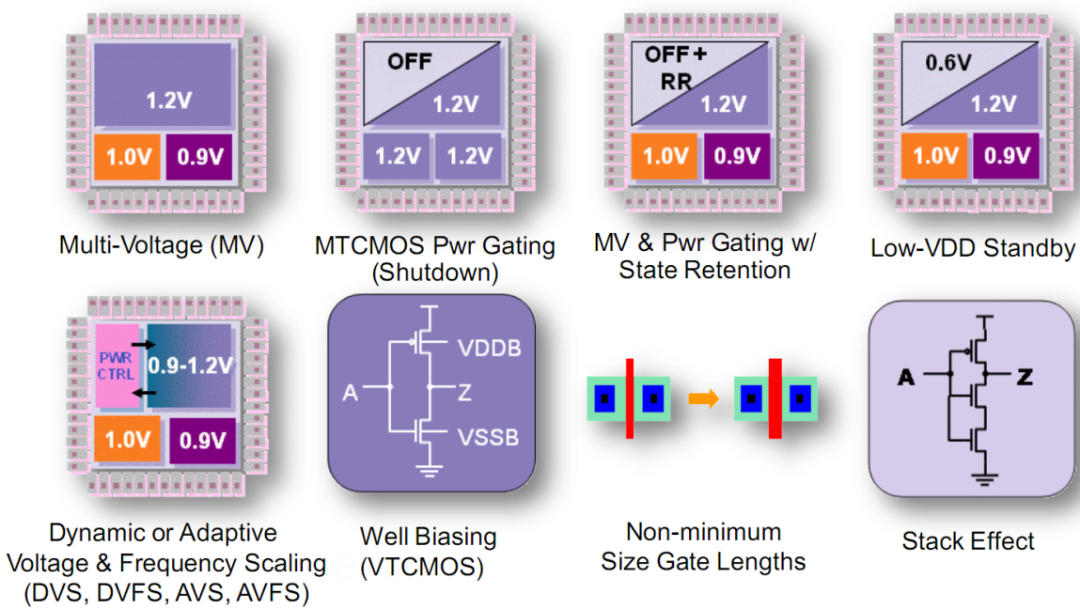

数字后端中多电压域

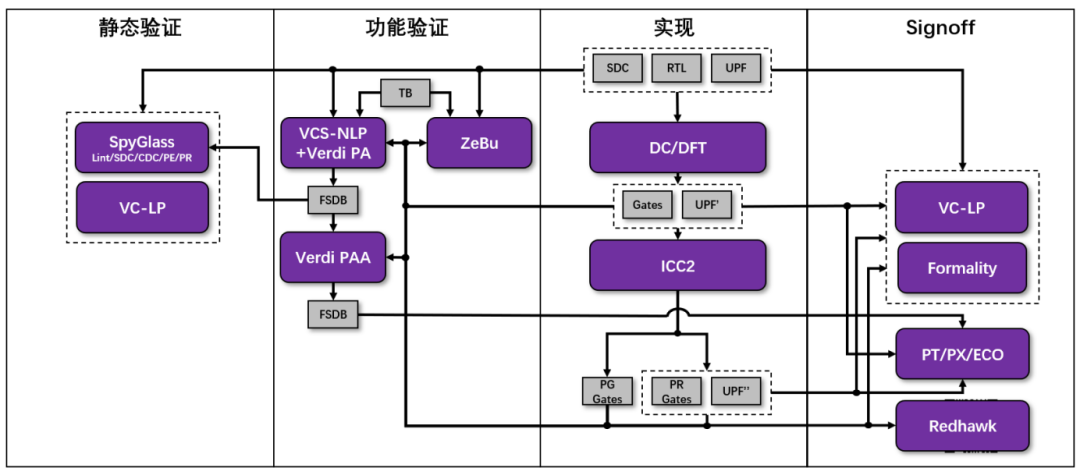

带UPF的低功耗设计流程中包括了前端VCS-NLP功能仿真,后端VC LP静态验证,以及在DC综合和ICC2布局布线中低功耗单元的插入,例如level shifter,isolation cell,retention cell和power switch等。Signoff阶段的Formality逻辑等价性检查以及PTPX功耗分析等。

三、UPF简介

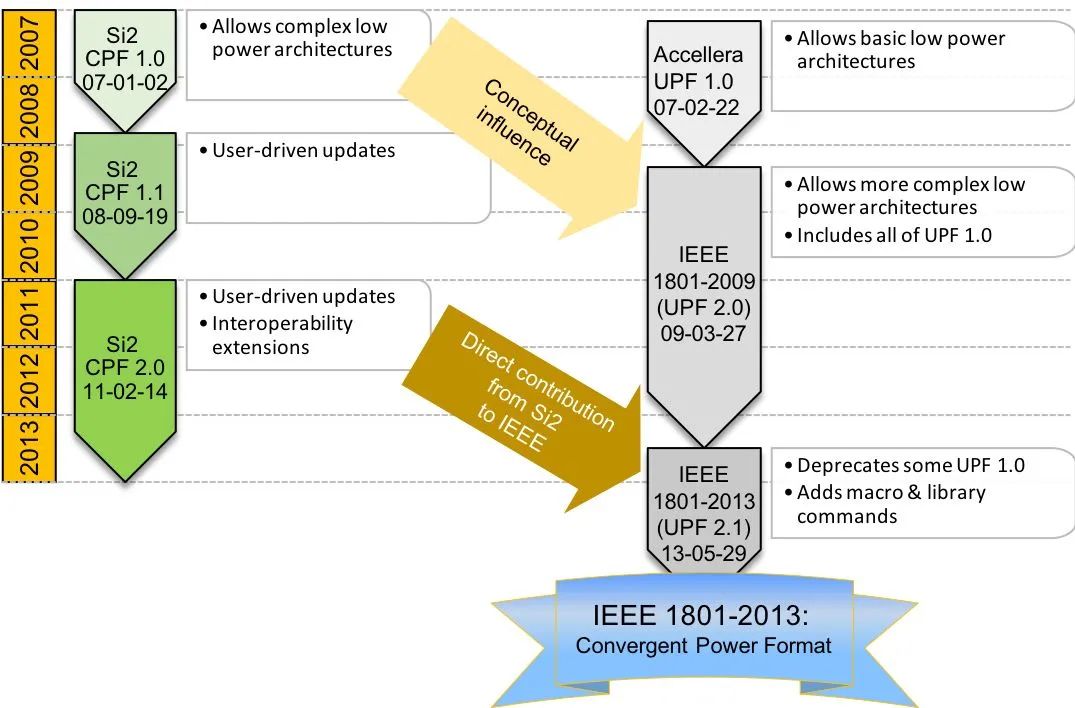

UPF(Unified Power Format)是通用的电源格式,是一组TCL语言的集合,用来描述芯片设计中的低功耗意图。UPF可以描述芯片工作的“电特性”,包括工作电压、电压的开关、低功耗cell插入的策略和芯片的power state等,UPF可以应用在设计、分析、验证和实现流程中。低功耗设计流程中加入UPF可以保证功耗意图在IC设计中的一致性,使低功耗意图在仿真、综合、一致性检查和设计验证环节更容易实现。

UPF历史

UPF的运用贯穿低功耗设计的始终,包括仿真验证、逻辑综合、物理实现、等价性验证和最终签核的过程。综合阶段会读入RTL文件和初始UPF文件,产生门级网表及综合后的UPF文件,该UPF文件不仅包括初始UPF信息,并且还包括了在综合过程中插入的低功耗单元。物理实现阶段是读入综合产生的网表和UPF,执行布局布线后,生成包含整个电源信息的网表和布局布线的UPF,该UPF包含初始UPF信息,并且还包括了插入的低功耗单元之间的电源连接关系。

审核编辑 :李倩

-

数字后端设计工程师主要干什么?2021-01-13 6866

-

求大佬分享数字后端的教材或教程2021-06-21 2315

-

什么是UPF呢?2021-07-28 2733

-

什么是低功耗UPF?2021-09-29 4731

-

招聘数字后端工程师2023-10-26 1208

-

数字后端设计流程2011-10-28 1849

-

数字逻辑实训板实训指导书2017-03-16 1343

-

数字后端关于Litho Grid基本概念介绍详解2017-12-14 5806

-

介绍数字后端概念--Shape Blockage2018-01-29 7574

-

数字后端基本概念介绍2018-03-16 25822

-

浅谈数字后端工程师的工作2021-02-26 15503

-

什么是低功耗设计呢(UPF编码篇)2023-05-15 3226

-

低功耗技术(三)UPF的使用2023-06-05 4843

-

数字后端基本概念介绍—FinFET Grid2023-07-12 2401

-

模拟前端和数字后端哪个好 模拟前端和数字后端的区别2024-03-16 2262

全部0条评论

快来发表一下你的评论吧 !