分析音频DAC抖动灵敏度

模拟技术

描述

本应用笔记描述了采样时钟抖动(时间间隔误差或“TIE抖动”)如何影响Δ数模转换器(DAC)的性能。新的见解解释了在这些器件中分别指定低频(< 2x 通带频率)和高频或宽带(> 2x 通带频率)抖动容限的重要性。本文还提供了一个简单的高度抖动周期跳跃采样时钟的应用示例,并描述了一种生成适当宽带抖动时钟的方法。然后,本文将Maxim的音频DAC抖动容限与竞争对手的音频DAC进行比较。Maxim具有极高的抖动容限,可实现非常简单、低成本的采样时钟实现。

高性能音频数模转换器(DAC)传统上需要一个非常干净的采样主时钟(MCLK),以避免音频质量下降。时钟源通常直接来自晶体振荡器,其产生的抖动通常小于100ps。在某些系统中,音频过采样频率(通常是3.072MHz或2.8224MHz的倍数)不是晶体振荡器参考频率的方便部分。虽然这些系统可以实现小数N分频PLL来创建所需的音频MCLK频率,但这种基于PLL的频率基准通常具有多个参考频率杂散和大量的低频抖动。此外,这些基于PLL的频率基准通常无法在不超过所需引脚数、面积或功耗目标的情况下使抖动足够低。然而,有一个解决这一困境的办法。可以容忍高抖动的音频DAC允许在此类系统中使用更简单的采样时钟基准。

了解抖动容限

高抖动容限很重要,因为它:

在存在抖动的情况下最大限度地提高音频信号质量

通过使用更简单的抖动时钟源降低系统复杂性或物料清单 (BOM)

无需高频 MCLK,从而降低功耗和电磁干扰 (EMI)

目前没有评估抖动容限的标准方法。音频精度 2700 (AP2700) 音频分析仪可以产生时钟抖动,但它产生的大部分是低频抖动(主要低于奈奎斯特音频采样率),如图 1 所示。

图1.AP5 产生的 2700ns “宽带”抖动频谱。

抖动容限测试设置

使用两个不同的抖动时钟源来比较多个DAC的抖动灵敏度。第一个抖动时钟是来自12MHz基准的288.25MHz周期跳跃时钟。这在11kHz以上产生~40ns的抖动,在0kHz以下产生~37.40ns的抖动。该 时钟 是 使用 NI PXI-5421® 100MHz 任意 波形 发生 器 (ARB) 创建 的, 该 发生 器 提供 所需 的 时钟 模式。

第二个抖动时钟是使用相同的ARB创建的宽带白色抖动时钟。ARB产生一个6.144MHz的正弦波,并增加白噪声,然后通过MAX999比较器馈送,产生具有大量宽带抖动的方波时钟。

使用LeCroy WaveRunner® 104MXI-A 1GHz示波器使用时间间隔误差(TIE)抖动测量来测量抖动。上升沿和下降沿在两个测试文件中都会抖动。

为此评估创建的宽带抖动时钟具有真正的宽带(白色)抖动频谱,适用于评估对宽带抖动的灵敏度。参见图 2、3 和 4。这种真正的白色抖动频谱不太可能在实际应用中找到;但是,这是一个很好的抖动容限测试,因为它将揭示任何特定频率范围内的抖动敏感性。

图2.用于此分析的宽带 5.9ns RMS 白抖动频谱。

图3.5.9ns宽带抖动直方图。

图4.示波器捕获3.072MHz时钟,具有5.9ns宽带白抖动。

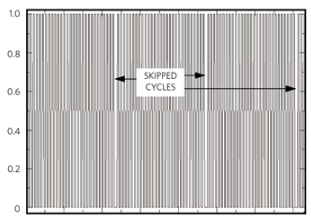

本研究使用的跳周期时钟如图5所示,该时钟的抖动频谱如图6和图7所示。该周期跳跃时钟测试表明,DAC可以容忍非常容易生成、极其抖动的时钟,而无需PLL。只需少量逻辑即可跳过任何频率基准的时钟周期,以生成任何(较低频率)采样时钟。这种类型的时钟生成不需要滤波或反馈环路。

图5.12.288MHz MCLK与周期跳跃的25MHz时钟的瞬态图。

图6.从12MHz参考时钟周期跳过的288.25MHz MCLK抖动频谱。

图7.周期跳跃时钟的低频抖动频谱。

Maxim的几个器件,包括音频编解码器(MAX98089和MAX98096)和MAX98355/MAX98356功率放大器,都受益于高抖动容限DAC。 这些器件的额定值可在 0 至 5kHz 频段内承受高达 0.40ns 的抖动,在 12kHz 频段上可承受 40ns 的抖动。有了这个抖动量,这些器件将显示以下抖动引起的性能限制(不包括电路噪声):

-108dB THD+N,1kHz 满量程音调

-96.5dB THD+N,6kHz满量程音调

-87dB THD+N,20kHz 满量程音调

105dB 动态范围和信噪比 (SNR)

THD+N性能结果仅受低频抖动(<40kHz)的影响。而动态范围和信噪比仅受高频抖动(> 40kHz)的影响。

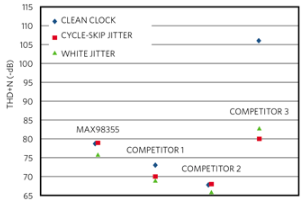

图8、9、10和11显示了Maxim MAX98355功率放大器使用高抖动时钟源测量的音频性能与一组竞争DAC的比较。除竞争对手 2 外,所有这些竞争部件都声称它们对时钟抖动不敏感,但没有提供抖动容限规格。

抖动容限测试结果

图8.动态范围下降,11.5ns RMS周期跳跃时钟抖动。

注意,MAX98355的动态范围不会随着周期跳跃的抖动时钟而降低。因此,MAX98355在时钟抖动时的性能比“120dB DAC”高出20dB以上。

图9.宽带白抖动导致动态范围下降。

竞争对手 3 的 5.5ns 和 9.3ns 抖动性能以及竞争对手 5 的 9.2ns 抖动性能是外推的,因为该器件在这些抖动电平下实际上无法正常工作;它们开始下降位,实际测量的动态范围低于该图所示。

图 10.1kHz THD+N 性能随时钟抖动而下降。

图 11.20kHz THD+N 性能随时钟抖动而下降。

结论

本应用笔记介绍了一种测试音频DAC抖动容限的方法。音频DAC对低频和高频频段抖动的响应不同,因此有助于分别指定抖动频谱这两个频段的容差。容忍高抖动的DAC允许更简单的采样时钟实现,而不会降低音频质量。

审核编辑:郭婷

-

电源设计的灵敏度分析2024-10-10 540

-

柔性传感器的灵敏度多少算高?传感器灵敏度大小与灵敏系数的关系2023-10-24 5057

-

分析音频 DAC 抖动灵敏度2022-11-17 394

-

#硬声创作季 现代电路分析与综合:6.1灵敏度概念Mr_haohao 2022-10-27

-

# **LOTO虚拟示波器关于触发灵敏度功能**2022-09-14 16712

-

ADC电源分类及灵敏度分析2021-03-11 1942

-

GPS接收机的灵敏度性能的原理性分析和设计高灵敏度GPS接收模块2020-01-07 2073

-

Multisim中的灵敏度分析方法,为什么没有电容的灵敏度,另外灵敏度是怎么判断的。2019-10-24 3821

-

扬声器的灵敏度2019-05-22 3439

-

航空液压管路灵敏度分析2018-03-06 1072

-

传输线网络瞬态响应灵敏度分析2017-01-07 882

-

什么是接收灵敏度2009-05-08 4869

全部0条评论

快来发表一下你的评论吧 !