为给定噪声预算选择最佳数据转换器

模拟技术

描述

介绍

本文是关于信号链中噪声的三部分系列文章的最后一部分。在第1部分关于恼人的半导体噪声中,我们确定了所有IC中半导体噪声的来源和特征。我们解释了器件数据手册中如何指定基准电压源,并展示了如何在数据手册中未指定的实际条件下估算基准电压源的噪声。在第2部分“数据转换器中的噪声和失真”中,我们重点介绍了数据转换器特有的噪声和失真源。我们展示了如何在数据手册中指定它们的噪声。在本文中,我们将第 1 部分和第 2 部分放在一起。现在,我们将帮助读者根据其噪声预算选择最合适的数据转换器。

信号链中的噪声

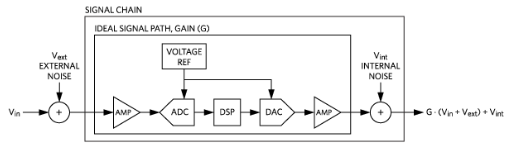

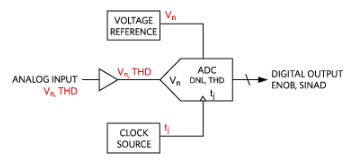

我们首先简要回顾本系列第 1 部分中涵盖的概念。噪声是电气系统中任何不受欢迎的电气现象。根据其来源,噪声可分为信号链的外部(干扰)或内部(固有)。在图1中,所有外部噪声源合并为单个项Vext,所有内部噪声源合并为单个项Vint。

图1.信号链中的噪声。

噪声预算是信号链中噪声的分配,可在输出端产生可接受的信噪比(SNR)。SNR定义为满量程RMS信号电平与总RMS噪声之比。因此,要确定信号链中可接受的噪声分布,必须评估其对总SNR的影响。为此,引入了数据转换器特有的两种规格:信噪比和失真(SINAD)和有效位数(ENOB)。

信噪比和失真

数据转换器扩展了SNR的定义,包括失真,并使用信噪比和失真(SINAD)这一术语。增加的失真包括所有不需要的频谱分量,不包括直流电。SINAD 是满量程 RMS 信号与所有其他噪声和失真分量的 RMS 总和之比。

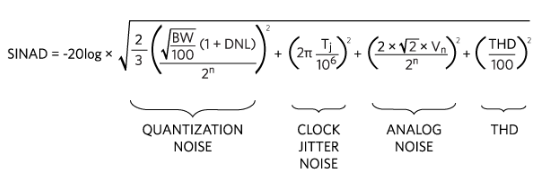

SINAD 可以用量化噪声、采样抖动、模拟噪声和总谐波失真 (THD) 表示为:

其中:

N 是分辨率,以位为单位。

DNL是平均微分非线性度,单位为LSB。

BW 是所用完整奈奎斯特带宽的分数,以百分比表示。

Tj 是采样周期的 RMS 抖动与正弦波信号周期的比值,单位为 ppm。

Vn是模拟噪声,以LSBRMS为单位。

THD是总谐波失真,以百分比表示。

SINAD 简化为熟悉的“经验法则”等式:

信噪比 = = 6.02N + 1.76dB LSBRMS

当:

BW = 100%

DNL = 0 LSB

Tj= 0ppm有效值

Vn= 0LSB有效值

总谐波失真 = 0%

这些参数值共同描述了理想的数据转换器,其中唯一的噪声源是采样过程中固有的全带宽量化噪声。

在本例中,ENOB = N 位。

有效位数

有效位数 (ENOB) 是衡量模数转换器 (ADC) 或数模转换器 (DAC) 在模拟域和数字域之间转换信号的能力的指标。ENOB是一种交流规范,是SINAD的同义词。

ENOB和SINAD由以下方面相关:

ENOB意味着数据转换器具有相当于理想数据转换器的噪声和失真水平。这意味着数据转换器具有全带宽和与ENOB等效的位数,但没有噪声和失真。ENOB 始终小于或等于设备的分辨率 (N)。不应将ENOB与直流精度混淆,后者只是分辨率(N)和线性度(INL)的函数。

ENOB 计算器

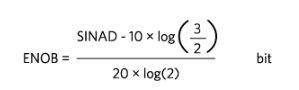

免费计算器,有效位数计算器(ENOB),可用于在数据转换器中快速进行噪声计算。要开始使用,只需单击链接并选择有效位数 (ENOB)。

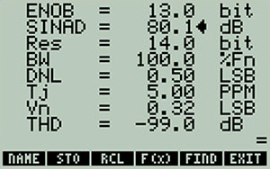

ENOB计算器是HP50g计算器的程序,有助于ADC和DAC应用电路的设计和分析。可以输入或找到每个噪声参数。

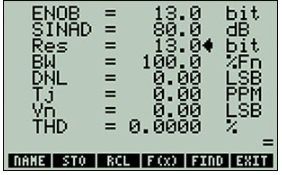

图2.ENOB 计算器屏幕截图。

ENOB计算器使用上述SINAD方程1和3,以及本系列第2部分中给出的噪声方程。每个参数都可以输入或找到,因此计算器对于设计和分析都很有用。该计算器用于说明在给定噪声预算下选择最佳数据转换器的方法。有关如何操作计算器的说明,请参阅用户指南(在计算器的 zip 文件中)。

为您的噪声预算选择最佳数据转换器

噪声预算是信号链中可接受的噪声分配,可产生所需的SINAD。一个示例最能说明为您的噪声预算选择最佳数据转换器的分步方法。ENOB计算器可以加快该过程,因为它可以进行必要的计算。

目的

在80kHz至0kHz带宽内使用满量程信号工作时,考虑到100dB SINAD的系统要求,选择最佳ADC。

图3.具有噪声相关规格的ADC。

第 1 步。选择分辨率

使用最简单的公式4作为理想数据转换器,我们将找到满足SNR所需的最小分辨率:...

信噪比 = 6.02N + 1.76dB

求解 N:

N = (信噪比 - 1.76)/6.02

使用 ENOB 计算器进行此计算,我们了解到 80db SINAD 需要 13 位分辨率(图 4)。

图4.ENOB计算器确定在我们的示例中需要13位分辨率。

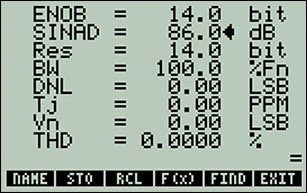

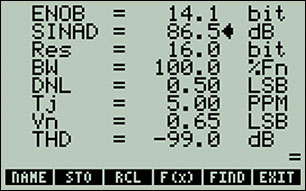

现在选择 14 位。是的,14位而不是13位,因为实际ADC的SINAD较低,因为DNL,T等其他因素j/ 5n,并且THD始终大于零,因此会增加噪声。在计算器中输入 14 位,我们发现 ADC 可以提供 86dB 的 SINAD(图 5)。

图5.使用14位作为ENOB,SINAD为86dB。

该值大于所需的80dB,因此我们首先查看14位ADC。

第 2 步。选择初始 ADC

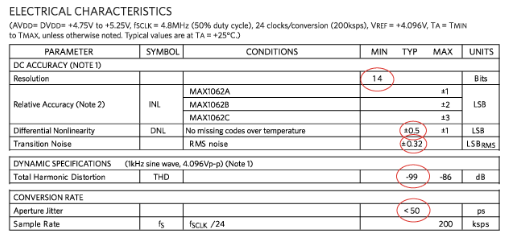

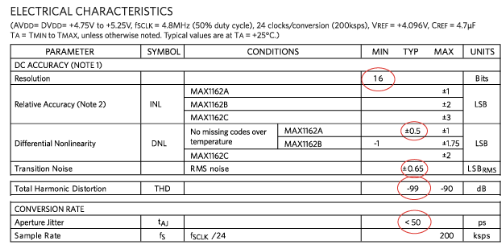

查找可接受 14kHz 至 0kHz 输入信号的 100 位 ADC。快速搜索Maxim集成ADC参数表,可以得到许多14位候选产品。本例使用MAX1062,数据资料中电气特性(EC)表中的所有相关参数如图6所示。

图6.MAX1062 ADC噪声参数

与我们的噪声预算分析相关的参数以红色突出显示。数据手册表明,该ADC的典型DNL为0.5LSB;典型输入参考噪声(Vn) 的 0.32LSB有效值;典型谐波失真为-99dB;和典型的孔径抖动(Tj) 的 50ps。在ADC中,折合到输入端的噪声称为转换噪声,因为它表现为输出代码之间转换时间的不确定性。

第 3 步。计算 SINAD

在计算器中输入上述EC表参数:DNL为0.5LSB,THD为-99dB和Vn的 0.32LSB有效值.

在 ENOB 计算器 T 中j定义为有效值抖动之比(tj) 的采样时钟到满量程正弦波周期,单位为 ppm。

在此示例中,最坏情况 Tj通过取 50ps (tj) 到最短输入信号周期 (tj) 的 1/100kHz,并将其乘以 106。因此,Tj= (50 × 10-12/10 × 10-6) × 106ppm = 5ppm。

在 T 中输入 5ppmj.

使用计算器,我们了解到SINAD降低到80.1dB(图7)。MAX1062符合我们的目标SINAD80dB,裕量为0.1dB。然而,在实践中需要额外的裕量,因为我们使用的是数据手册中的典型值,而不是器件的最大值。我们也没有考虑任何其他噪声源的存在。

图7.现在计算器显示MAX1062的SINAD为80.1dB。

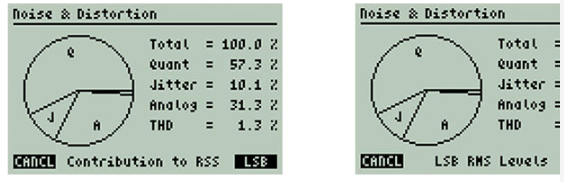

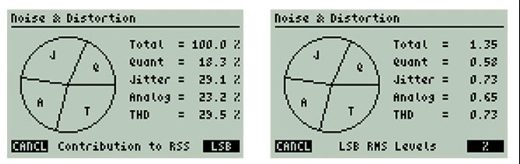

第 4 步。检查噪声分布

在采取措施降低噪声之前,我们首先检查噪声和失真水平(图8),看看可以改进的地方。

图8.ENOB 计算器以图形方式将噪声分布显示为和平方根 (RSS) 的百分比或 LSB有效值.

图8.ENOB 计算器以图形方式将噪声分布显示为和平方根 (RSS) 的百分比或 LSB有效值.

可以看出,量化噪声是总噪声和失真的最大贡献者。可以通过提高分辨率来降低量化噪声。

第5步。降低量化噪声

通过选择MAX16的1162位版本可以实现额外的噪声容限。同样,所有相关参数都出现在数据手册的EC表中(图9)。

图9.MAX1162 ADC噪声参数

与我们的噪声预算分析相关的参数以红色突出显示。如果未给出典型值,则根据14位器件MAX1062估算典型值。

现在在计算器中输入MAX1162的参数,找到其SINAD:

N = 16 位

DNL = 0.5LSB

Tj= 5ppm

Vn= 0.65LSB有效值

总谐波失真 = -99dB

MAX1162 SINAD为86.5dB(图10),符合我们的目标SINAD80dB,裕量为6.5dB。

图 10.MAX1162的SINAD为86.5dB。

再次回顾,典型值用于预测MAX1162的SINAD实际上,SINAD的实际值可能更小。您可以使用数据手册中尽可能多的最大参数值来确定更保守的估计值。

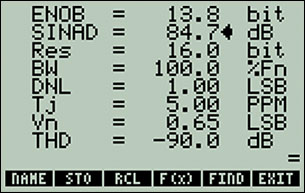

第 6 步。重新计算 SINAD

现在我们重新计算MAX1162的SINAD,但这次使用EC表中的最大值。此步骤还有助于我们确定MAX1162在最坏情况下的DNL和THD下是否能满足80dB SINAD要求。数据手册指出,最坏情况下的DNL为1LSB (最大值),最差情况下的THD为-90dB (最大值)。将这些值输入计算器,我们看到:

N = 16 位

DNL = 1.0 LSB

Tj= 5ppm

Vn= 0.65LSB有效值

总谐波失真 = -90dB

SINAD 为 84.7dB(图 11)。我们的结论是,MAX1162满足80dB的目标SINAD,裕量为4.7dB。

图 11.使用最大LSB和THD值,16位MAX1162的SINAD为84.7dB。

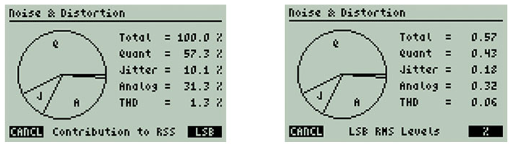

步骤 7.重新检查噪声分布 重新检查最坏情况下的噪声和失真水平,我们发现量化、采样抖动、输入参考噪声和THD之间的噪声分布

大致相等。请注意,没有单一的噪声源是主要因素(图 12)。

图 12.通过比较图 8 和图 12 强调了图形显示的有用性。量化噪声已大大降低。

总噪声从40.0LSB降低了57%有效值14位至1.35LSB有效值在 16 位(相当于 0 位时的 34.14LSBRMS)。噪声的降低导致SINAD的增加。

第8步。进行一些噪声分布权衡

只要不超过总噪声预算,噪声就可以在信号链内的源之间重新分配(图13)。

图 13.信号链中的ADC噪声源。

时钟抖动(Tj)和模拟噪声(Vn) 可以使其源位于数据转换器的外部。因此,尽管这些规格对于给定的ADC是固定的,但可以通过改变ADC外部的电路来改进它们。例如,您可以使用低噪声输入放大器和基准电压源或低抖动采样时钟。

如何添加随机噪声源

所有不相关的噪声源都以和方根 (RSS) 方式进行几何求和:

en总计= √(e2N1+ e2N2+ e2N3+ ... + e2nn)

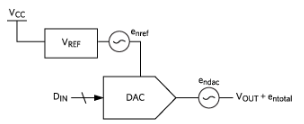

一个术语通常主导 RSS 总和。例如,在图14中,输出噪声来自基准电压源(enref)和DAC(endac)。

.

总输出噪声是DAC输出设置为满量程时enref和endac的RMS总和:

entotal = √(e2nref + e2ndac)>

如果 enref = 300nV/vHz 且 endac = 100nV/vHz,则总计 = 316nV/vHz。

DAC仅贡献16nV/vHz的总噪声!这里有一个教训:在对抗不相关的噪音时,专注于减少主导术语。

噪声权衡

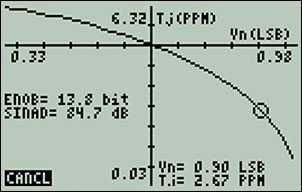

ENOB计算器可以绘制任何变量相对于另一个变量。此功能现在用于显示时钟抖动(Tj) 和输入噪声 (Vn),而不影响 SINAD。曲线上的任何位置都可以通过圆形光标选择,并显示参数权衡(图15)。

图 15.ENOB计算器比较时钟抖动和输入噪声之间的权衡,光标指示权衡值。

上面的光标位置表示 V 之间的权衡n和 Tj保持 84.7dB 的 SINAD。光标指示如果 Vn增加到0.9LSB,则必须将时钟抖动降低到2.67ppm,以保持84.7dB的相同SINAD。

最后,还有另一种有用的工具可用于计算ADC和DAC应用中的误差预算。有关更多详细信息,请参阅下面的侧边栏。

结论

ACD和DAC数据手册中的典型值和最大值可用于确定存在噪声(如数据转换器量化、时钟抖动、通道非线性以及输入和输出参考噪声)的系统性能。演示了为给定噪声预算选择最佳数据转换器的分步程序。ENOB计算器有助于分析这些参数,并指导我们找到控制和减少其他系统噪声元素的建设性方法。

-

数据转换器中的噪声量化噪声方案2021-06-01 7250

-

数据转换器中的噪声和失真 如何为其应用选择最合适的数据转换器2023-02-28 70526

-

浅谈转换器的噪声2018-08-08 3072

-

时钟发生器性能对数据转换器的影响2018-10-18 2459

-

选择最佳的DC/DC转换器的五大秘诀2019-03-25 3563

-

时钟发生器的相位噪声和抖动性能为什么会影响到数据转换器?2019-07-30 3112

-

如何为DC/DC直流电源转换器选择最佳的开关频率呢2021-11-01 2040

-

请问数据转换器中噪声与误差之间的关系?2023-12-07 613

-

为降压型转换器选择电感器2009-04-27 773

-

TI 放大器及数据转换器选择指南2017-09-16 734

-

如何选择选择最佳的数据转换器2021-05-24 2144

-

为转换器时钟应用选择最佳器件2022-04-24 1986

-

为您的救生医疗应用选择最佳DC-DC转换器2022-07-29 2039

-

为给定的噪声预算选择最佳数据转换器:第 3 部分2022-11-17 198

-

为高速数据转换器设计低抖动时钟2023-02-25 4441

全部0条评论

快来发表一下你的评论吧 !