一种测量ADC转换错误率的测试方法

模拟技术

描述

犯错是人之常情。但是,对于您系统的模数转换器(ADC),可以提出哪些要求?我们将回顾高速ADC的转换错误率(CER)测试和分析范围。ADC CER测量过程可能需要数周或数月才能完成,具体取决于采样速率和所需的目标限值。通常,为了获得高置信水平(CL),需要在第一次错误率之后进行测试(Redd,2000)。对于那些需要低转换错误率的系统,需要这种详细的关注和努力来量化。当我们完成所有操作时,可以高置信度地确定错误率 - 优于<10–15.

许多实际的高速采样系统,如电气测试和测量设备、重要系统健康监测、雷达和电子战对策,都不能容忍ADC转换误差的发生率。这些系统正在寻找跨越宽噪声范围的极其罕见或小的信号。这些系统中的错误警报触发器可能导致系统故障。因此,能够量化高速ADC转换误差率的频率和幅度非常重要。

CER 与 BER

一开始,让我们在错误率描述中分离出两个明显的差异。转换错误率(CER)通常是由于ADC对模拟电压样本做出错误决定的结果,因此,与转换器输入的满量程范围相比,ADC各自的数字代码做出了错误的决定。ADC的误码率(BER)也可以描述类似的误差。但是,出于我们在这里讨论的目的,我们将 BER 定义为纯粹的数字接收错误,否则正确转换的代码数据。在这种情况下,下游逻辑器件(如FPGA或ASIC)无法正确接收正确的ADC数字输出。代码的错误程度及其出现频率是我们将在本文其余部分讨论的内容。

ADC转换误差可能很难通过简单地从数据手册中读取技术参数来收集。您当然可以通过转换器数据手册上的单个数字来估算转换错误率。但是这个数字究竟量化了什么?您无法判断什么尺寸的样品偏移被视为误差,也无法确定测试测量或模拟中的置信水平。“误差”的定义必须以已知发生频率的大小为界限。

错误源

ADC内部和外部的多个误差源都可能导致转换误差。外部源包括系统电源毛刺、接地反弹、异常大的时钟抖动和潜在的错误控制命令。ADC数据手册建议和应用笔记通常会概述规避这些外部问题的最佳系统布局实践。ADC的内部源主要归因于亚稳态(Beavers,2014),或模拟域中级之间的残余处理切换,以及数字层和物理层域中的输出时序误差。ADC设计团队必须在开发元件期间分析这些挑战。

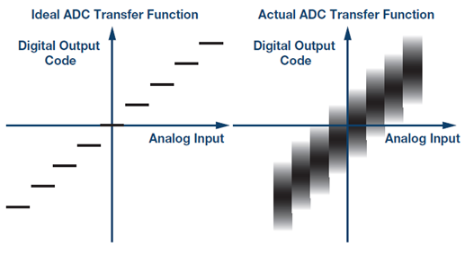

图1.理想的ADC样本在满量程内具有每个模拟分辨率位的单个数字输出(左)。实际ADC输出行为示例(右)显示了与内部和外部噪声相关的一些模糊性。

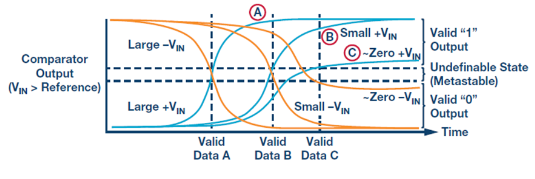

当 比较器基准电压精确等于或非常接近 要比较的电压(Kester,2006)。星等越接近 比较电压是其参考电压,它所需的时间越长 比较器做出完整的决定。在三角电压下降的情况下 两者之间很小或为零,比较器可能没有 有足够的时间解决电压是否高于的最终决定 或低于引用。随着样本的转换时间到期, 比较器输出可能保持亚稳第三状态,而不是 清楚地确定有效的逻辑输出为 1 或 0(Kester,2006)。这种优柔寡断 会波纹穿过ADC,并可能导致转换误差。

图2.理想的ADC样本在满量程内具有每个模拟分辨率位的单个数字输出(左)。实际ADC输出行为示例(右)显示了与内部和外部噪声相关的一些模糊性。

在流水线ADC架构中,转换误差的其他潜在来源是级间边界切换点,其中残余电压从一个级传递到下一级。例如,如果两级之间发生未校正的增益匹配误差,则残余电压的切换可能会在后续级中产生误差。此外,残余DAC中的毛刺将电压发送到下一个ADC级,也可能在后续处理中导致意外的中断错误(Kester,2006)。所有ADC固有的热噪声分量存在于任何无源元件中,它决定了ADC处理的绝对本底噪声(Brannon,2003)。在对ADC进行全面检定期间,必须对所有这些潜在的误差源进行审查和量化,以确保转换器的执行中没有任何间隙。

噪声成分

折合到输入端的噪声是ADC转换缺陷的一个固有组成部分,包括ADC输入端的热噪声。它通常使用数字输出代码直方图进行量化,给定开路或浮动ADC输入。这通常在ADC数据手册中注明并显示。下图显示了这种噪声幅度的示例,在本例中为 [N] ± 11。

图3.对于开路或浮动输入,理想的ADC将对单个中间电平失调代码进行采样,如左侧直方图所示。实际ADC将具有折合到输入端的噪声,该噪声应在右侧以对数刻度显示高斯形状弯曲直方图。

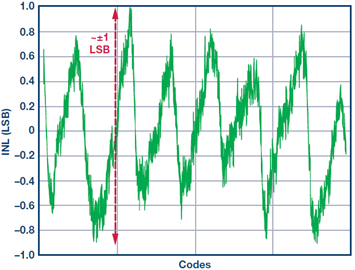

ADC的积分非线性(INL)是实际采样码相对于理想输出的满量程ADC输入范围内的传递函数(Kester,2005)。此信息通常也指定并绘制在ADC数据手册中。与理想代码的最大偏差通常表示为一定数量的最低有效位(LSB)。下面可以看到一个示例 INL 图。虽然它代表了一定程度的绝对误差,但在大多数分辨率为0位或更低的高速ADC中,INL通常只考虑约3至16个代码。它不会是实际转换器错误率的主要贡献者。

图4.一个跨所有ADC代码的INL曲线示例显示,与理想样本相比,最大误差约为±1 LSB或±1代码,与ADC转换误差基本可以忽略不计。

测试方法

用于长期CER检测的测试方法可以使用相对于时钟速率的非常低的ADC输入频率。正弦波的斜率可以近似为任何相邻的两个采样点之间的大致直线。类似地,略高于采样率的频率输入将混叠为低频。对于这种情况,有一个可预测的理想解决方案,即每个相邻样本都可以在前一个样本的 ±1 个代码范围内。输入信号频率和编码采样时钟频率需要锁定在可预测的相位对齐中。如果该相位不保持恒定,则对准将移出相位,测量数据将无用。因此,为了计算理想的转换,sample(N + 1) – sample(N) 应该是数量级不超过 1 的代码差异。

所有ADC固有的小的可预测转换误差来源包括积分非线性、输入噪声、时钟抖动和量化噪声。所有这些噪声贡献因素可以累积相加,以获得最坏情况限值,如果超过该限值,将考虑来自两个相邻转换样本的误差。16位ADC的输出代码数量为24位转换器的16或12×。因此,这种扩展的分辨率将对用于测试转换错误率的限制的代码数量产生影响。在其他条件相同的情况下,16位ADC的限值将比16位ADC宽12×。

ADC内部内置自检(BIST)可用于根据热噪声、时钟抖动和其他系统非线性度建立误差阈值。当超过误差限值时,可以在ADC内核内标记特定样本及其相应的样本计数和误差幅度。使用内部BIST的主要优点之一是,它可以隔离ADC内核本身内的误差源,从而排除了仅在数字数据传输输出中接收的位错误引起的误差。一旦建立了误差阈值,就会执行涉及ADC加链路以及FPGA或ASIC的完整系统测量,以确定完整的元件CER值。

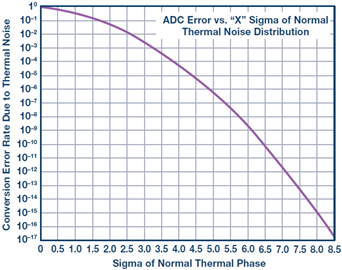

图5.ADC的转换误差率与其热噪声的关系通常只能通过晶体管级电路仿真获得。上图显示了12位ADC的示例图,其中必须容许8的热噪声σ才能实现10–15的CER。

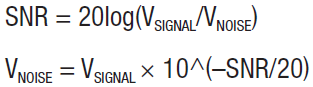

让我们来看看我们如何计算热噪声贡献(Brannon,2003)。

为了找到ADC的均方根噪声,我们必须标定V满量程:

AD9625是一款12位、2.6 GSPS ADC,设计满量程范围(FSR)为1.1 V,在55.2 MHz混叠输入频率下SNR为508,使用以下公式计算热噪声限值。热噪声限值 = 8 西格玛 × VIN聚丙烯× 10 × (SNR/20)/2√(2) = 3.39 mV ~ ±12 码

在这种情况下,仅热噪声的 8 西格玛分布就可以提供多达 ±12 到 10–15错误限制。这应该根据ADC的总输入折合噪声测量值进行测试。请记住,数据手册中的折合到输入端的噪声可能不是基于足够大的样本量(10–15测试。折合到输入端的噪声将包括所有内部噪声源,包括热噪声。

为了定义可能涵盖所有噪声源(包括测试设备)的限值,我们使用内部BIST来测量误差幅度分布。在AD9625中使用内部BIST,工作速率为2.5 GSPS,混叠A。在在标称电源和温度条件下,频率接近ADC的满量程,频率为80 kHz,CER测量在20天内进行。

假设ADC对模拟电压的所有处理都是理想的。在信号链下游的FPGA或ASIC处理的下一阶段,数字数据仍然需要精确地发送和接收。此阶段的数字混乱通常由术语位错误或位错误率定义。但是,可以直接测量PCB走线末端ADC输出的数据眼图的全面表征,并将其与JESD204B接收器模板进行比较,以便很好地了解输出质量(Farrelly,Loberg 2013)。

为了建立10个核证的排减量–15,一千万亿个样本,在 1 西格玛以内,在 2.6 GSPS 下,我们需要连续运行此测试4.6 天。为了使用更大的西格玛建立更高的置信水平,此测试需要运行更长时间2.测试需要非常稳定的测试环境和清洁的电源。被测转换器电源电压上的任何非抑制毛刺都将导致错误的测量,测试将需要重新开始。

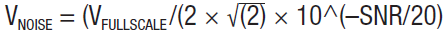

FPGA计数器可用于跟踪两个相邻样本之间的时间幅度差异超过阈值限制的情况,将该样本计为转换误差。计数器必须在整个测试期间保持累积错误总数。为了确保系统按预期工作,误差与理想值的大小也应记录在直方图中。测试所需的时间将基于采样率、所需的测试转换错误率和所需的置信水平。核证的排减率为 <10–15置信度为 95% 需要至少 14 天的连续测试。CER的估计可以通过以较低的置信水平推断超出测量值来完成(Redd,2000年)。

由于测量ADC的CER可能是一项耗时的工作,因此您可能想知道是否可以推断出超出已知测量结果的范围。好消息是,是的,这是可以做到的。但是,这种方法总是需要权衡取舍,因此可能需要注意。随着我们继续对错误率进行有根据的数学估计,如果我们几乎确定地对其进行测试,我们在估计中接近不断降低的置信水平。3 例如,知道错误率为 10 可能不是那么有用–18,如果我们对答案的信心低于 1%。

对于任何给定样本,转换的误差阈值可以累积为 4 或 5 个最低有效位。根据ADC分辨率、系统性能和应用的误码率要求,可能会略多或少。当使用此误差带与理想值进行比较时,超过此限制的样本将计为转换误差。ADC的误差带可以通过调整阈值和监控典型性能数据来测试。使用的最终测试限值是缺陷的均方根和,通常由ADC热噪声决定。

采样值与理想值的测试数据直方图类似于泊松分布,泊松分布是离散分布。泊松分布和二项分布之间的主要区别在于泊松没有固定数量的试验。相反,它使用记录成功次数的固定时间或空间间隔,这类似于所描述的CER测试方法。任何超出理想值计算误差限值的记录样本都被识别为真正的代码错误。

图6.通过将ADC样本的长期直方图与理想输出代码进行比较,我们可以检测到超出计算限值的任何偏移。直方图类似于泊松分布。

系统

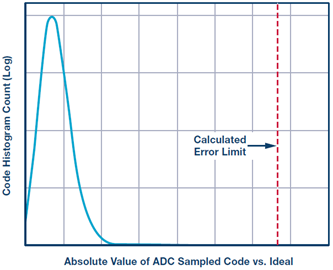

现在我们了解了单个转换器的CER,我们可以计算由多个转换器组成的高级同步系统的误码率。许多系统工程师会问,在使用多个ADC的大型复杂系统中,累积ADC转换误差率是多少。

因此,高级多信号采集系统的次要考虑因素是识别转换器阵列的转换错误率。一开始,这听起来可能是一项艰巨的任务。幸运的是,在测量或计算单个ADC的CER后,将此速率外推到多个ADC并不是太困难。然后,该函数根据系统中使用的转换器数量成为概率展开方程。

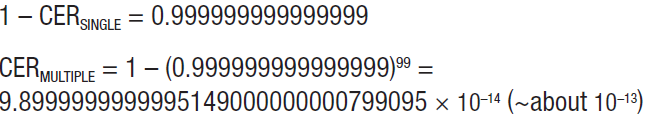

首先,我们找到单个转换器不会出现错误的概率。根据错误率的值,这仅略小于 1,(1 – CER单).其次,然后将系统中每个ADC的该概率乘以自身,(1 – CER单) #ADCs.最后,我们可以通过从 1 中减去该值来找到系统中发生错误的速率。我们得到以下等式:

让我们考虑一个使用99个ADC的系统,单个ADC CER为10–15.

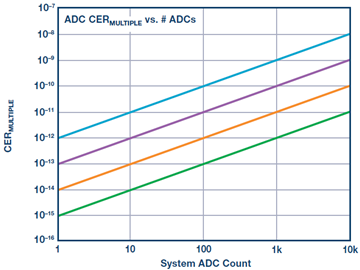

我们可以看到核证的核证的产生倍数现在的值比CER高出近100×单的 10–15.我们可以从中了解到,基本上,具有99个ADC的系统的转换错误率与单个ADC的CER成比例地成比例,具体取决于系统中ADC的数量。它从根本上高于单个ADC,并且受到单个ADC的转换误差率和系统内使用的转换器数量的限制。因此,我们可以确定,与单个ADC相比,由许多ADC组成的系统可能会显著降低整体转换错误率。

图7.使用多个转换器的系统的CER按ADC计数按比例缩放单个CER。

精确定位ADC转换误差可能具有挑战性,但可以实现。第一步是确定系统中转换误差的大小。然后,需要确定一组适当的有界误差限值,其中包括预期ADC操作的非线性良性源。最后,特定的测量算法可以实现大部分或全部测试。测量值的外推可以针对超出测试边界的目标,以获得额外的近似值。

审核编辑:郭婷

-

一种用于测量ADC转换误差率的测试方法2017-04-24 2114

-

模数转换器代码错误率使闪光变暗2022-08-10 1043

-

一种提高ADC分辨率的插值滤波方法pdf2012-11-03 1941

-

CC254x专有模式包错误率测试2016-02-25 2599

-

CC2538+CC2592通信错误率很高,什么原因?2016-03-25 3864

-

测量ADC转换误差率的测试方法2018-10-19 2924

-

用于测量模数转换器输出字中的位错误的FPGA固件项目参考设计2022-09-22 1305

-

深度解读高速ADC的转换误差率2023-12-20 1123

-

ADC转换误差率的测试分析2017-11-15 9239

-

IBM宣布语音识别技术的错误率已接近人类2019-10-24 1151

-

如何测量ADC的转换误差率详细方法说明2020-10-22 1101

-

报告指出口罩正在挫败常规的人脸识别算法,提高错误率2020-08-28 952

-

了解 ADC 代码错误率2023-08-17 2201

-

OpenAI攻克Sora视频创建错误率高难题2024-12-31 1108

全部0条评论

快来发表一下你的评论吧 !