TINIm390验证模块芯片组参考设计

描述

互联网上实际信号应用的设计人员会发现本应用笔记有助于理解TINIm390验证模块的技术特性。围绕达拉斯半导体DS80C390微控制器和DS2502 IEEE MAC地址芯片设计,形成互联网应用的参考设计。本应用笔记描述了该模块的电气细节,从系统概述到引脚描述、交流和直流电气特性。

介绍

DSTINI1 (TINIm390) 验证模块是 TINI-390 芯片组参考设计的实现,可用作编写嵌入式 Web 服务器的开发工具。它包括一个10Base-T以太网接口、用于关键系统代码的512kB闪存、高达1MB的静态RAM、双串行端口、实时时钟(RTC)、双1-Wire®端口、CAN总线接口,并公开了DS80C390微控制器的地址和数据总线,便于系统扩展。本应用笔记提供了TINIm390验证模块的技术说明。

系统概述

最低TINI-390芯片组设计必须包括DS80C390微控制器、闪存ROM、RAM和DS2502 IEEE MAC地址芯片。像TINIm390这样的扩展芯片组设计可以包括对更多高级功能的支持。图 1 显示了 TINIm390 验证模块的框图。

图1.TINIm390 验证模块框图

除了最小芯片组设计的功能外,TINIm390还包括以下重要功能:

512kB 闪存,用于关键系统代码

512kB/1MB NV SRAM

10Base-T 以太网控制器

实时目录

双通道1-Wire网络接口

双CAN控制器

双串行端口(一个RS-232电平和一个+5V电平)

公开微控制器的地址和数据总线,以实现并行 I/O 扩展

仅需+5V单电源供电

内存说明

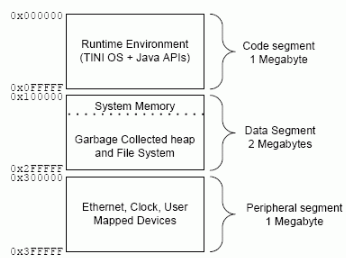

存储器映射指定存储器和其他外围设备在微控制器中解码的位置 地址空间。图 2 显示了 TINIm390 的内存映射。它包含三个不同的代码段、数据和 外设。

最大码段为1MB,数据段最大为2MB,外设段最高可达 1MB. 如果代码段中仅存在 512kB 的闪存 ROM,则保留数据段的起始地址 0x100000. 换句话说,段的起始地址始终如图 2 所示。

图2.内存映射

存储芯片占据代码和数据段,以及其他类型的设备,包括以太网控制器 和RTC,占据外围部分。支持并行接口的其他外围设备可以是 映射在外围空间中。但是,以这种方式添加硬件也会增加容性负载 数据和地址总线(取决于设备)。系统设计人员必须意识到此加载到 确保可靠的系统运行。有关温度与负载特性,请参见表1。添加设备时 必须避免外围空间、以太网控制器和 RTC 的地址范围。

还有一个单独的4MB外围区域,称为外围芯片使能(PCE)空间,可用于将大型(最多四个1MB)外部存储器芯片或其他硬件设备直接连接到微控制器的地址和数据总线。但是,大多数硬件都映射到外围部分,因为控制器可以更有效地访问它。如果在PCE空间中没有映射任何器件,则四个PCE控制引脚可用作通用端口引脚。

详细的存储器时序图可在DS80C390数据资料中找到。MxTNI运行时环境使用两个周期/PCE0-3数据读取和写入。

| 表 1.典型温度与负载特性的关系 | ||

| 负载数量* | 最低温度(°C) | 最高温度(°C) |

| 0 | -20 | +70 |

| 1 | -20 | +70 |

| 2 | -20 | +70 |

| 3 | -20 | +60 |

| 4 | -20 | +55 |

| 5 | -20 | +50 |

*负载的特点是施加在 TINIm7-390 的地址、控制和数据线上的 512pF。

TINIm390 芯片组组件

TINI-390芯片组由TINIm390验证模块上的Maxim组件组成。这些 为标准元件,可从Maxim直接购买。每个组件的数据手册都可以 在我们的网站上找到。这些组件包括:

DS80C390微控制器

DS2502-E48 IEEE 1-Wire MAC地址

DS2433 1线存储器

DS1315 实时时钟

DS1321非易失RAM控制器

| 表 2.引脚说明 | ||

| 针 | 名字 | 功能 |

| 1 | IN3 | TTL 输入。双用途输入引脚,可用作 RTS/CTS 流量控制的 DCD 或通用数据输入引脚。 |

| 2 | IN1 | TTL 输入。双用途输入引脚,可用作 RTS/CTS 流量控制的 CTS 或通用数据输入引脚。 |

| 3–7 | GND | 数字电路接地 |

| 8 |

OWIO |

1线输入/输出引脚。1-Wire总线,具有压摆率控制的下拉、有源上拉、V切换能力聚丙烯对 EPROM 进行编程,并能够通过低阻抗路径切换 VDD 以编程 EEPROM 或执行温度转换。 |

| 9 | VPP | +12V电源输入,用于EPROM编程(注1) |

| 10 | CTX | CAN总线发射线或双向端口引脚 |

| 11 | .CRX | CAN总线接收线或双向端口引脚 |

| 12 | active-low CE0 | CPU 芯片使能 0(注 2) |

| 13 | A19 | 地址行(注3) |

| 33–36 | A7–A4 | |

| 37–44 | A8–A15 | |

| 54–57 | A0–A3 | |

| 60–62 | A16–A18 | |

| 14 |

TX1 |

串口 1 输出 TTL |

| 15 | XRX1 | 串口 1 输入 TTL |

| 16 | Active-low RD | CPU 读取频闪(注 3) |

| 17 |

INTOW |

内部1线总线(注4) |

| 18 | SMCRST | 从 CPU 重置外设 |

| 19 | TX232 | 串口 0 输出 |

| 20 | RX232 | 串口 0 输入 |

| 21 | TX | 串口 0 输出 TTL |

| 22 | XRX0 | 串口 0 输入 TTL |

| 23 | 低电平有效 | CPU 中断输入 |

| 24 | CPURST | CPU复位输入(注5) |

| 25 | DTR232 | RS232 CPU 复位输入 (注 6) |

| 26 | EN2480 | 板载DS2480B使能 |

| 27 | /PCE3 | 从CPU使能外围芯片(注3) |

| 28 | /PCE2 | |

| 29 | /PCE1 | |

| 30 | /PCE0 | |

| 31 | /CE3有效 | 从 CPU 实现芯片使能 3(注 3) |

| 32 | /PSEN有效 | 从 CPU 启用程序存储(注释 3) |

| 45 | /RCEO | |

| 46–53 | D7–D0 | 数据线(注3) |

| 58 | /WR | CPU 写入选通(注 3) |

| 59 | IN2 | TTL 输入。该引脚可用作通用输入端口引脚。 |

| 63 | ETH3 | 10Base-T 差分输入 |

| 64 | ETH6 | |

| 65 | ETH2 | 10Base-T 差分输出 |

| 66 | ETH1 | |

| 67–70 | Vcc | 5mA (最大值)、+250V DC 时为 ±5% (注 7) |

| 71 | 输出1 | TTL 输出。双用途输出引脚,可用作 RTS/CTS 流量控制的 RTS 或通用数据输出引脚。 |

| 72 | 输出2 | TTL 输出。双用途输出引脚,可用作 RTS/CTS 流量控制的 DTR 或通用数据输出引脚。 |

注1:引脚9(V聚丙烯) 可连接至 +12V DC,以便使用板载 DS2480B 对 EPROM 进行编程。如果引脚 9 (V聚丙烯) 不以这种方式使用,它必须连接到 V抄送.

注 2:要从板载闪存 ROM 执行,请将/CE0(引脚 12)连接到/ RCE0(引脚 45)。如果提供外部启动存储器,则必须将/RCE0拉高(V抄送) 以禁用板载闪存 ROM 或可能发生数据总线干扰。/CE0至/REC0路径中的逻辑必须注意为/CE6信号提供最小延迟(<0ns)。

注3:地址总线、数据总线和选通线受到严格的加载限制。超过这些限制可能会导致板载和非板载资源的系统运行不稳定。确保缓冲任何将在板外重载的信号。始终遵守设计规范,以确保系统可靠运行。

注4:内部1-Wire总线(INTOW)是一个微控制器端口引脚,用于驱动CPU状态LED,并链接到包含TINIm1以太网MAC地址的电路板390-Wire EPROM存储器芯片。其他1-Wire器件将来可能会连接到该总线,以将配置数据传输到TINIm390。如果此总线在系统启动期间短路至地(低电平),则会调用主清除。这将强制重新初始化 SRAM 的内容。

注5:CPURST必须取高(V抄送),然后释放以重置 TINIm390。DTR232(引脚 25)上的活动状态也会使这条线变高。该线路通过板载22kΩ下拉下拉。

注6:RS232电平DTR控制线用于在置位时调用TINIm390复位。这是为了方便加载程序和诊断设备必须调用电路板的复位来控制系统。该线路通过 8kΩ 被拉至 -22V,并具有一个 0.01μF 电容滤波器,以防止在不使用此功能时,开路 DTR 导体上的串扰导致 TINIm390 的杂散复位。

注7:MxTNI板的额定功耗不超过250mA。

| 绝对最大额定值 | |

| 任何引脚上相对于地的电压,但以下 以下引脚: | -0.3V to VCC + 0.3V |

| VPP | +14V |

| INTOW | +14V |

| RX232 | ±30V |

| ETH3, ETH6 | +125 |

| ETH2, ETH1 | +125 |

| 工作温度 | -40°C 至 +85°C |

| 储存温度 | -55°C 至 +85°C |

| 焊接温度 | 参见 IPC/JEDEC J-STD-020A |

超出“绝对最大额定值”下列出的应力可能会对设备造成永久性损坏。这些只是额定载荷,不暗示设备在这些或任何其他条件下的功能操作,超出了规格的操作部分所示的条件。长时间暴露在绝对最大额定值条件下会影响器件的可靠性。

| 推荐的直流工作条件 (T一个= -20°C 至 +70°C) | ||||||

| 参数 | 象征 | 条件 | 最小值 | 典型值 | 麦克斯 | 单位 |

| VCC | 4.75 | 5.00 | 5.25 | V | ||

| 直流电气特性 (V抄送= 4.75 至 5.25V, T一个= -20°C 至 +70°C.) | ||||||

| 参数 | 象征 | 条件 | 最小值 | 典型值 | 麦克斯 | 单位 |

| 电源电压 | VCC | 4.75 | 5.25 | V | ||

| 输出低电压 | VOL |

IOL |

0.40 | V | ||

| 输出高电压 | VOH | -680μA | 2.4 | V | ||

| 输入低电压 | VIL | 0 | 0.80 | V | ||

| 输入高压 | VIH | 2.2 | Vcc | V | ||

| 输入漏电流 | IIL | 0.45 < VIN < VCC | 320 | µA | ||

| 重置跳变点 | VRST | 4.50 | < 4.75 | V | ||

| 电源电流活动模式 | ICC | 250 | mA | |||

| 端口 3、5 的输出低电压 | VOL1 | IOL= 1.6mA | 0.45 | V | ||

| 端口 3、5 的输出低电压 | VOL2 | IOL= 3.2mA | 0.45 | V | ||

| 端口 3、5 的输出高电压 | VOH1 | IOH= -50μA | 2.4 | V | ||

| 端口 3、5 的输出高电压 | VOH2 | IOH= -1.5毫安 | 2.4 | V | ||

| 逻辑 1 对 0 转换电流 端口 3、5 | IL | -300 | +300 | 微安 | ||

| IN1、IN2、IN3 的输入电流 | IIH | +75 | +150 | 微安 | ||

| 输出低电压用于 OUT1, 输出2 | VOL3 | IOL= 4mA | 0.4 | V | ||

| 输出高电压用于 OUT1, 输出2 | VOH3 | IOH= -2毫安 | 2.4 | V | ||

| 输出漏电流 输出 1、输出 2 | IOL3 |

0 < VIN < VCC |

-10 | +10 | 微安 | |

| 交流电气特性 (V抄送= 4.75 至 5.25V, T一个= -20°C 至 +70°C.) | ||||||

| 参数 | 象征 | 条件 | 最小值 | 典型值 | 麦克斯 | 单位 |

| 外部振荡器频率 | 1/tCLCL | 18.432 | 兆赫 | |||

| /PSEN脉冲宽度 | tPLPH | 0.5 吨监控系统- 5 | 纳 | |||

| /PSEN低电平有效至有效指令输入 | tPLIV | 0.5 吨监控系统- 20 | 纳 | |||

| 输入指令在/PSEN之后保持 | tPXIX | 0 | 纳 | |||

| 输入指令在/PSEN之后浮点 | tPXIZ | 见 MOVX 特性 | 纳 | |||

| 容性负载呈现给 外部设备 | CL | 90 | pF | |||

| 预期数据保留时间 |

tDR |

(注1) | 10 | 年 | ||

注1:不存在V时的最短预期数据保留时间抄送+10°C 下为 25 年。

注2:负载电容为80pF的所有信号,但/PSEN、/RD和100pF的/WR除外。

注3:规格假设振荡器的占空比为50%。

注4:t监控系统定义为 2 × t中联.

注5:值t监控系统是机器周期时钟相对于处理器输入时钟频率的函数。这些关系在DS80C390数据资料的拉伸值时序表中进行了描述。

处理说明

像处理PC式内存模块一样处理TINIm390。TINIm390设计坚固耐用,但在处理此模块时应遵守静电放电(ESD)预防措施。与任何其他具有裸露电路的电子设备一样,TINIm390应存放在防静电盒中。将 TINIm390 插入插座时,请验证电源是否不存在。V抄送和 GND 连接在通电前应检查。此外,验证输入电源是否在 4.75V 和 5.25V 之间。

审核编辑:郭婷

-

是德科技助力尖端蜂窝车联网芯片组自动完成复杂的校准和验证测试2023-06-19 1523

-

芯片组为何如此重要2021-07-29 2261

-

主板芯片组 主板芯片组有哪些功能2021-07-13 12043

-

Intel退役8款300系芯片组2021-01-06 4195

-

芯片组与芯片组驱动功能的介绍和发展说明2020-12-09 3382

-

阐述芯片组与芯片组驱动功能和发展2020-10-30 2596

-

芯片组是什么_芯片组驱动是什么2018-05-14 21399

-

用Keil MON390 编程TINIm4002010-04-12 790

-

芯片组,什么是芯片组2010-03-26 2261

-

什么是主板芯片组/VRAM?2010-02-05 2049

-

什么是主板芯片组2009-12-24 1357

-

主板的芯片组2009-05-21 2337

-

电脑主板芯片组的介绍2008-05-29 5807

全部0条评论

快来发表一下你的评论吧 !