8086基础-定时器

描述

4.1 8253简介

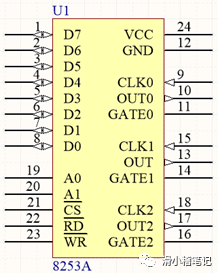

4.1.1 引脚详解

(1)三态双向数据口D0~D7:用于8253A与CPU的并行通信;

(2)计数脉冲输入CLK0~CLK2:用于提供8253的计数脉冲;

(3)通道门控GATE0~GATE2:控制对应通道的输出;

(4)读控制信号RD:低电平有效;

(5)写控制信号WR:低电平有效;

(6)片选信号CS:低电平有效;

(7)地址选择端A0,A1:用于选择芯片内部的寄存器。

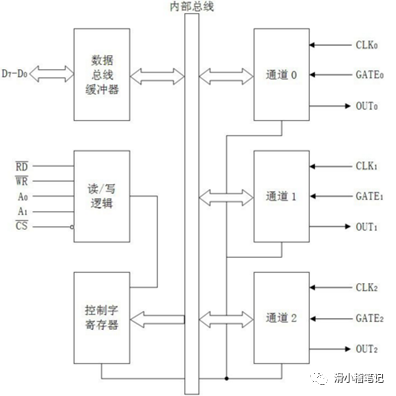

4.1.2 内部结构框图

4.1.3 工作模式

(1)工作模式0—计数结束产生中断

在计数值减到0时输出信号OUT将产生一个上升沿,这个上升沿作为CPU的中断请求信号,当CPU执行完中断处理程序时,如果希望再一次启动计数器结束中断功能,可以再次将计数值送给它。

(2)工作模式1—可编程单稳态输出方式

计数初值写入到8253A后必须等待GATE信号的触发才能开始计数,触发后使输出信号OUT变低,计数到0时,OUT信号又回到高电平,这类似于数字电路中的单稳态电路,而低电平的宽度由计数脉冲的个数决定,所以这种工作方式又称为可编程单稳态输出方式。

(3)工作模式2—频率发生器/分频器

该模式在计数器减到0的时候会重新自动地把原来的初值寄存器中的数据装载到减一计数器中重复计数,第一次运行时有一个额外的下装脉冲,而后续的重复计数没有这个额外脉冲,它的下装脉冲直接用上一次计数的最后一个脉冲,所以,当计数值设为N时,第一次要N+1个脉冲,后面重复计数的值皆为N。

(4)工作模式3—方波发生器

模式3与模式2基本相似,不同之处在于计数值如果为偶数,OUT输出的高电平宽度与低电平宽度相等,称为方波发生器,如果计数值为奇数,高电平比低电平多一个CLK的脉冲宽度。

(5)工作模式4—软件触发的选通信号发生器

模式4除OUT的波形与模式0不同,计数过程中GATE和计数初值发生变化对OUT的影响与模式0一样。

(6)工作模式5

模式5除了OUT的波形与模式1不同之外,计数过程中GATE和计数初值发生变化对OUT的影响与模式1一样

4.1.4 控制字格式

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| SC1 | SC0 | RW1 | RW0 | M2 | M1 | M0 | BCD |

控制字的具体描述如下表所示:

| 计数器选择 |

|---|

| SC1 |

| 0 |

| 0 |

| 1 |

| 1 |

| 计数器操作方式控制 |

|---|

| RW1 |

| 0 |

| 0 |

| 1 |

| 1 |

| 计数器工作模式选择 |

|---|

| M2 |

| 0 |

| 0 |

| 0 |

| 0 |

| 1 |

| 1 |

| 1 |

| 1 |

D0:二进制与BCD码选择

0:二进制形式

1:BCD码形式

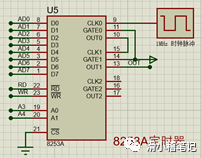

4.1.5 端口地址计算

8253通过引脚CS、RD、WR、A0和A1五个端口的电平决定芯片内部的寄存器,地址对应如下表所示。

| CS | RD | WR | A1 | A0 | 功能 |

|---|---|---|---|---|---|

| 0 | 1 | 0 | 0 | 0 | 设置计数器0的初值 |

| 0 | 1 | 0 | 0 | 1 | 设置计数器1的初值 |

| 0 | 1 | 0 | 1 | 0 | 设置计数器2的初值 |

| 0 | 1 | 0 | 1 | 1 | 设置控制字或命令 |

| 0 | 0 | 1 | 0 | 0 | 读取计数器0的计数值 |

| 0 | 0 | 1 | 0 | 1 | 读取计数器1的计数值 |

| 0 | 0 | 1 | 1 | 0 | 读取计数器2的计数值 |

4.2 8253初始化流程

(1)将控制字写入8253A

(2)对8253A中的某个计数器写入初值

(3)启动计数器

注意:由于8253A是一个16位的计数器,所以当计数的时间超出计数器的范围时可以考虑用两个计数器级联达到目的。

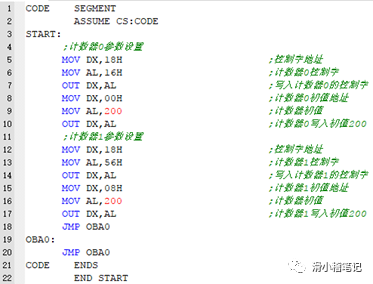

4.3 源代码

例题:利用8253A芯片产生一个500ms,占空比50%的方波。

解析过程:由于硬件电路设计时利用1MHz作为计数器的时钟脉冲,所以计数器的一个脉冲的时间应该是1us,由于需要产生一个20ms的高电平,所以需要计数20000次才可以,但是由于8位的计数器数据范围是255,所以采用两个计数器级联的方式达到目的,将两个计数器均设置为模式3(即方波发生器),另外,根据硬件连接,A0连接在地址端的A3,A1连接在地址端的A4,片选CS接地,所以,对应计数器0的初值设置地址应该是0000 H,计数器1的初值设置地址应该是0008 H,控制字的地址为0018 H。经过上述分析,源代码如下图所示。

注:由于设定的计数器工作在模式3,所以计数脉冲会自动在中间产生脉冲

-

使用555定时器的可调双定时器电路2024-02-25 5040

-

定时器中断是什么意思,定时器中断的工作原理2023-07-23 8461

-

STM32定时器(二)定时器中断2023-07-21 5573

-

什么是软件定时器?软件定时器的实现原理2023-05-23 4459

-

基础定时器实验2023-03-01 2916

-

定时器开关怎么接线?2023-02-24 16467

-

31章-定时器2022-01-17 747

-

SysTick 定时器2021-12-05 953

-

STM32定时器学习---基本定时器2021-12-02 1668

-

STM32——高级定时器、通用定时器、基本定时器的区别2021-11-26 3951

-

基于硬件定时器的软件定时器2021-11-25 1222

-

STM32定时器-基本定时器2021-11-23 1995

-

定时器电路图工作原理(声光提示定时器电路/555定时器电路/相片曝光定时器电路)2021-11-05 19241

-

555定时器2015-11-10 3871

全部0条评论

快来发表一下你的评论吧 !