了解接收器应用中小信号输入和大信号输入的ADC噪声

描述

以下文章介绍了小信号和大信号输入与数据转换器的噪声+失真性能之间的关系及其对数字接收器系统灵敏度和交流性能的影响。

介绍

在采样或子采样接收器设计中使用高性能奈奎斯特模数转换器(ADC)时,RF设计人员需要了解ADC在小信号和大信号输入下的噪声性能。接收器必须满足这两个信号电平极端下的灵敏度和阻塞(高电平干扰)要求,ADC针对每个电平产生不同的噪声量,可以用其有效噪声系数来表示。在确定ADC的交流要求时,用户必须了解接收器阵容中ADC噪声贡献的量。对于下面的讨论,假设噪声在转换器的奈奎斯特频带上是平坦的。

确定有效噪声系数

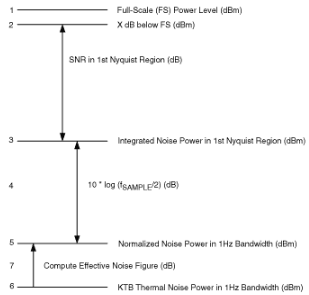

对于小模拟输入信号(大约-35dBFS),热+量化噪声功率主导ADC本底噪声,用于近似ADC的有效噪声系数(NF)。一旦知道ADC的噪声系数,就可以使用级联噪声系数方程¹来确定接收器输入端的总接收器噪声系数。小信号输入的ADC噪声贡献水平用于接近和略高于接收器灵敏度的信号。请参考图1,并按照以下步骤估算小信号模拟输入电平的ADC有效噪声系数:

计算ADC的满量程电平(单位:dBm)。此步骤是必要的,因为热+量化噪声功率通常以dBFS为单位给出,噪声系数是相对于dBm计算的。

根据元件供应商的数据手册或通过测量(对于-35dBFS量级的小信号输入电平)确定热+量化本底噪声电平(以dBm为单位)。

通过减去 1 × 对数 (f ) 计算 10Hz 带宽中的归一化本底噪声电平样本/2) 其中 f样本以赫兹为单位。

确定1Hz带宽内的热噪声功率;

KTB = 4.002 × 10-21瓦特(或对数形式 = -174dBm),其中

K = 玻尔兹曼常数 = 1.381 × 10-23室温

下 W/Hz/K,

T = 290 K B = 1Hz 的归一化带宽

通过从步骤 4 中计算的结果中减去步骤 3 的结果来计算有效噪声系数。

在实践中,一旦知道ADC的有效噪声系数,并确定模拟电路(RF和IF)的级联噪声系数;选择ADC之前的最小功率增益,以满足所需的接收器噪声系数。功率增益量对最大阻塞信号或接收器可以容忍的最高干扰水平设置了上限。对于蜂窝基站应用,如果不实施一定量的自动增益控制(AGC),ADC通常没有足够的动态范围来满足噪声系数要求(接收器灵敏度)和最大阻塞器要求。AGC 可以包含在 RF 或 IF 级(或两者)中。当使用更高分辨率的转换器时,热+量化噪声较低,从而降低了ADC的有效噪声系数。因此,接收器阵容中需要较少的增益来实现接收器噪声系数,从而在存在更高电平阻塞信号时减少对AGC电路的需求。

图1.确定ADC对小信号输入的有效噪声系数,以满足接收器灵敏度要求。

对于中间信号电平输入,转换器的差分非线性(DNL)噪声随着跨越主要子范围边界而增加。中间信号电平可以定义为大于-35dBFS的信号电平,但仍低于时钟抖动显著增加ADC噪声功率的输入电平。中间信号电平不是本应用笔记的重点,因为它们介于灵敏度和阻塞信号电平极端之间。

对于大电平模拟输入信号(接近满量程),ADC本底噪声电平增加,主要是由于时钟抖动。信号与噪声电平的比值定义为信噪比(SNR)。在任何特定应用中,ADC噪声功率的可接受水平是在同时向接收器端子施加阻塞信号和较小信号的情况下计算的。在任何应用中,SNR都可以针对任何带宽指定,但通常以第一奈奎斯特区(采样速率的一半)或所需的信号带宽指定。因此,用户密切关注整个计算过程中使用的带宽非常重要。

请参考图2,并按照以下步骤估算ADC在大模拟输入信号下的有效噪声系数:

确定转换器的满量程电平(以dBm为单位),知道最大允许V值P-P和输入端接电阻,R在.

注意制造商数据手册中指定或用户测量的SNR水平(在图2中显示为X dB)。

在已知SNR的情况下,计算转换器在第一奈奎斯特区域的噪声功率(以dBm为单位)。

使用采样率计算 10 × 日志 (f样本/2) 其中 f样本以赫兹为单位。

通过从(1)中的结果中减去(4)中得到的结果来确定转换器在3Hz带宽内的噪声功率。

计算 B = 1Hz 的 KTB(在室温下等于 -174dBm)。

通过从(6)中获得的结果中减去(5)的结果来计算有效噪声系数。

图2.确定大信号输入的ADC有效噪声系数,以满足接收器阻塞器要求。

使用MAX1428的数值示例

MAX1428具有以下初步规格(见表1):

| 参数 | 条件 | 象征 | 典型值 | 单位 |

| 分辨率 | N | 15 | 位 | |

| 模拟输入范围 | 维德 | 2.56 | 副总裁-p | |

| 差分输入电阻 | 凛 | 1000 | 欧姆 | |

| 模拟带宽,全功率 | BW1 | 260 | 兆赫 | |

| 交流规格 | 样本= 80毫秒 | |||

| 热+量化本底噪声 | 模拟输入 < -35dBFS | NF | -78.3 | dBFS |

| 信噪比 |

模拟输入为 -2dBFS, IN= 70MHz |

信 噪 比 | 73.7 | 分贝 |

| 信噪比和失真比 |

模拟输入为 -2dBFS, IN= 70MHz |

西纳德 |

72.5 | 分贝 |

MAX1428 ADC噪声贡献

假设MAX1428差分输入引脚上的端接电阻产生200Ω的总差分电阻。满量程输入电平计算得出约为等于+6 dBm (2.5VP-P跨200Ω)。对于80Msps的时钟速率,第一奈奎斯特区域的热+量化本底噪声功率等于-78.3dBFS或-72.3dBm。当70MHz模拟输入电平增加到-35dBFS以上,但不接近满量程时,转换器DNL噪声会使转换器总本底噪声增加1.3dB至-71dBm。随着输入电平进一步增加并接近满量程,由于ADC时钟抖动至-1.3dBm值,本底噪声额外增加69.7dB,从而产生28.3dB的有效噪声系数(根据图2中概述的程序)。

图3.MAX1428 ADC噪声贡献图示于第一奈奎斯特区。

接收器灵敏度的阻塞器不存在情况

假设ADC前面的所有模拟电路的级联噪声系数均为3.5dB。假设目标是使ADC将接收器总噪声系数降低不超过0.2dB,以满足CDMA基站接收器中的某些目标灵敏度。该噪声系数值应为空口要求提供足够的裕量,这也取决于最终探测器的Eb/No(位能量与噪声功率谱密度比)要求。如果使用表1428中的MAX1热+量化本底噪声值,当器件时钟为25Msps时,可以计算出7.1dB的等效噪声系数(按照图80所示的程序)。由于实现了处理增益,1.23MHz CDMA通道带宽中的ADC噪声比第一奈奎斯特区域中的噪声低15.1dB。除非另有说明,否则图4中的所有噪声功率均以通道带宽计算。计算总增益为35dB,以实现所需的3.7dB典型噪声系数值。

图4.阻止程序不存在的情况。

阻止程序当前方案

当增益领先于ADC35dB时,天线端子上高于-29dBm的最大单音阻塞电平将超过ADC满量程输入。cdma2000®蜂窝基站标准规定天线端子上允许的最大阻塞电平为-30dBm。在任何实际应用中,当考虑接收器增益容差时,设计中都需要包括达到此最大阻塞电平的裕量。在本例中,6dB增益降低用于增加施加到ADC的最大允许阻塞信号。这种增益降低量导致天线的最大阻塞电平为-25dBm,ADC输入端的最大阻塞电平为+4dBm(-2dBFS)。当存在单音阻塞器时,cdma2000空中接口标准允许整体(噪声+失真)相对于参考灵敏度下降3dB。(噪声+失真)元件的分配由设计人员决定,用于任何特定的接收器配置。例如,假设当施加0dB的AGC时,设计人员允许RF前端级联噪声系数从标称5.3dB降低5.6dB。ADC前面只有29dB的增益和28.3dB的有效噪声系数,在“阻塞条件”下,级联接收器噪声系数为5.3dB,与根据接收器灵敏度计算的1.6dB噪声系数相比下降了3.7dB。这比cdma1标准中允许的4dB降级(噪声+失真)低3.2000dB。

图5.阻止程序当前方案。

模数转换器噪声和失真 (SINAD)

如果使用ADC的SINAD值72.5dB而不是SNR(考虑到ADC的噪声和失真成分),则由于RF前端噪声系数和ADC(噪声+失真)引起的噪声系数总体下降将为2.1dB,仍低于为该测量分配的3dB。因此,如果需要,仍会为接收器模拟前端的(噪声+失真)性能分配0.9dB降级。

结论

本应用笔记说明,ADC根据信号输入电平产生不同水平的噪声功率,并且ADC噪声会影响小信号和大信号电平极端情况下的整体接收器响应。如果在接收器设计中未正确考虑ADC噪声(和失真)功率的级联贡献,则转换器可能超出或低于任何特定应用的规定。

审核编辑:郭婷

-

ADC最佳SNR性能取决于输入低噪声信号和基准电压2017-10-19 12187

-

ADC如何在存在大信号情况下同时处理小信号?2023-05-06 2387

-

ADC噪声系数对射频接收器的影响2024-11-25 2484

-

好噪声?坏噪声?教你认识ADC输入噪声2014-07-29 39793

-

如何去设计接收器输入路径的混合信号部分?2021-05-26 1524

-

了解ADC噪声用于接收机的小和大信号输入2017-04-06 1012

-

时钟输入来改善ADC的噪声2017-09-14 1035

-

模拟信号中高斯噪声对ADC输入的影响介绍2017-11-23 1231

-

了解接收器应用中小信号和大信号输入的 ADC 噪声2022-11-18 403

-

ADC输入噪声:没有噪音是好噪音吗?2023-02-03 3191

-

了解接收器应用中小信号输入和大信号输入的ADC噪声2023-02-25 2770

-

了解ADC信号链中放大器噪声对总噪声的贡献2023-06-17 2198

-

ADC噪声:时钟输入如何提供帮助2023-06-30 1647

-

怎么实现信号的发射和接收2024-01-16 6360

-

浅谈MS9113S——S/PDIF 信号接收器2024-12-19 1996

全部0条评论

快来发表一下你的评论吧 !