MAX2395 PLL在80kHz比较频率下的性能

描述

本应用笔记给出了MAX2395的优化环路滤波器设计,具有80kHz比较频率,以支持WCDMA/UMTS系统。参考频率为 13MHz 或 26MHz。还显示了 EVM 结果。

介绍

MAX2395为全单芯片准直接变频调制器IC,用于WCDMA/UMTS发送器。由于其内部架构,RF输出频率为RF LO频率的5/6,RF频率由片内整数N分频PLL产生。由于WCDMA系统中的光栅频率为200kHz,MAX2395 PLL需要提供240kHz步长(即6的5/200倍)。对于WCDMA用户终端应用中最常用的参考频率,例如19.2MHz和15.36MHz,内部PLL整数分频器(分别为240和80)可以轻松生成64kHz比较频率。模拟评估板在设计时考虑了19.2MHz基准电压源。

在UMTS系统中,通常使用13MHz或26MHz的参考频率,它不是240kHz的整数倍。因此,MAX2395的PLL使用的比较频率需要降低到倍数为240kHz和13/26MHz。对于26MHz晶体,常用的比较频率为80kHz,通过使用三个240kHz步进允许80kHz通道光栅。对于相同的LO,80kHz PLL频率的“N分频”值高出3倍,导致近载波相位噪声(10logN)增加20dB。

EVM(误差矢量幅度)也会降低,因为PLL对EVM的贡献大致与其积分相位误差成正比。比较杂散从环路滤波器获得的衰减较低,因此需要重新设计环路滤波器,以平衡积分相位误差、建立时间和比较杂散衰减。

环路滤波器组件

在240kHz比较频率下使用的环路滤波器带宽约为12kHz,对于7kHz比较频率情况,带宽约为80kHz。下表显示了相应的环路过滤器组件值:

| 带宽 = 12kHz, 240kHz 比较频率 | 带宽 = 7kHz, 80kHz 比较频率 |

| C1 = 2.2nF | C1 = 1nF |

| C2 = 22nF | C2 = 10nF |

| R2 = 3.3kΩ | R2 = 7.5kΩ |

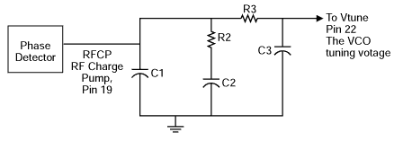

参见下面的原理图(图1),了解无源环路滤波器拓扑。

图1.

测量数据

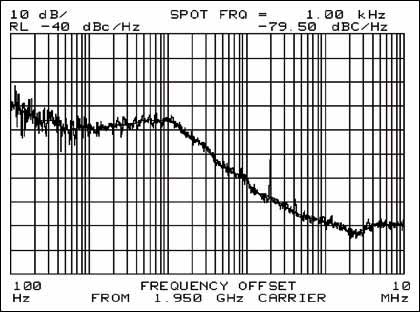

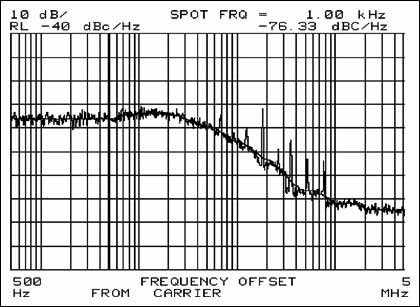

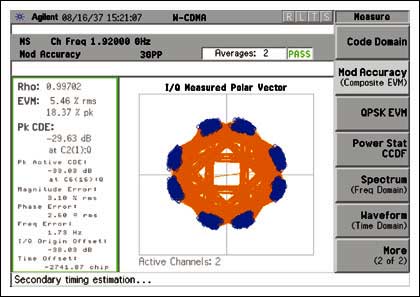

MAX2395的性能分别在模拟WCDMA参考设计板上使用19.2MHz和26MHz晶体进行测量。所有测量的图如图2至图7所示。

图2.19.2MHz基准晶体处的相位噪声图。

图3.26MHz参考晶体处的相位噪声图。

图4.射频输出时的 EVM,频率为 19.2MHz 参考晶体。

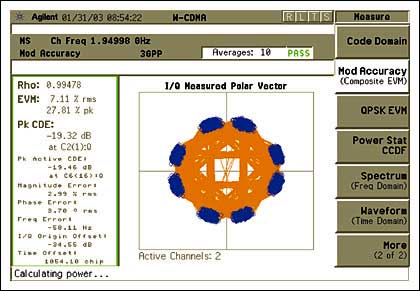

图5.26MHz 参考晶体时射频输出时的 EVM。

图6.超过 60MHz 的 PLL 建立时间在 19.2MHz 晶体处跳跃。

图7.PLL建立时间超过60MHz,在26MHz晶体时跳跃。

500Hz至1.92MHz的积分相位误差在1kHz比较频率下为98.240度,在2kHz比较频率下为75.80度。前者在RF输出为5.5%时产生EVM结果,而后者产生7.2%的EVM。对于采用720.60MHz晶体的19MHz步进频率,环路建立时间为2μs,对于820MHz晶体,环路建立时间为26μs。两种情况下的比较杂散衰减相似,约为-40dBc。

审核编辑:郭婷

-

探索MAX2871:超宽带PLL频率合成器的卓越性能与应用2026-04-21 28

-

LMK04808 PLL1为什么不能正常锁定?2024-11-12 346

-

TLV320AIC3101测试音频的仪器不用80KHZ的低通滤波器时,输出信号失真度很大,为什么?2024-10-25 402

-

AD7767主时钟由STM32提供80KHz时,DRDY信号产生异常是什么问题?2023-12-06 472

-

MAX2395锁相环(PLL)在鉴相频率为80kHz时的性能2023-06-09 2884

-

MAX2395输出与SAW滤波器匹配,实现最佳的级联增益平坦度2023-03-03 2769

-

MAX2395ETI+ RF 其它 IC 和模块2023-02-04 97

-

具有 80kHz 比较频率的 MAX2395 PLL 的性能2022-11-18 315

-

请问《STM32》2.0版本PWM产生的频率是不是应该是80KHZ?2019-09-19 1769

-

开关电源的频率和ADSL性能2011-06-12 2301

-

基于FPGA的PLL频率合成器2010-09-01 547

-

70W、80kHz彩色监视器用升压变换器电路2009-07-20 1436

-

MAX2395 WCDMA准直接调制器,带有VGA和PA驱动2009-02-19 1050

-

80M~1.2G频带PLL频率合成器2008-08-17 2505

全部0条评论

快来发表一下你的评论吧 !