网络SMII接口解析

网络SMII接口解析

描述

RMII接口综述

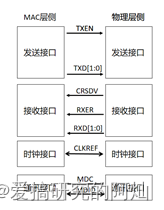

RMII接口有12个信号线,所有信号名称都是从MAC层侧说明的,主要#包括四个部分。一是从MAC层到物理层的发送数据接口,二是从MAC层到物理层的接收数据接口,三是物理层与MAC层之间时钟接口,四是MAC层和物理层之间数据管理的MDIO/MDC接口。

接口图片解析

引脚定义解析

TXD[1:0]:数据发送信号线,数据位宽为2,是MII接口的一半。

RXD[1:0]:数据接收信号线,数据位宽为2,是MII接口的一半。

TXEN(Transmit Enable):数据发送使能信号,与MII接口中的该信号线功能一样。

RXER(Receive Error):数据接收错误提示信号,与MII接口中的该信号线功能一样。

CLKREF:是由外部时钟源提供的50MHz参考时钟,与MII接口不同,MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

CRSDV:此信号是由MII接口中的RX_DV和CRS两个信号合并而成。当介质不空闲时,CRS_DV和RECLK相异步的方式给出。当CRS比RXDV早结束时(即载波消失而队列中还有数据要传输时),就会出现CRSDV在半位元组的边界以25MHz/2.5MHz的频率在0、1之间的来回切换。因此,MAC能够从 CRSDV中精确的恢复出RXDV和CRS。

在100Mbps速率时,TX/RX每个时钟周期采样一个数据;在10Mbps速率时,TX/RX每隔10个周期采样一个数据,因而TX/RX数据需要在数据线上保留10个周期,相当于一个数据发送10次。

当PHY层芯片收到有效的载波信号后,CRS_DV信号变为有效,此时如果FIFO中还没有数据,则它会发送出全0的数据给MAC,然后当FIFO中填入有效的数据帧,数据帧的开头是“101010—”交叉的前导码,当数据中出现“01”的比特时,代表正式数据传输开始,MAC芯片检测到这一变化,从而开始接收数据。

当外部载波信号消失后,CRSDV会变为无效,但如果FIFO中还有数据要发送时,CRSDV在下一周期又会变为有效,然后再无效再有效,直到FIFO中数据发送完为止。在接收过程中如果出现无效的载波信号或者无效的数据编码,则RXER会变为有效,表示物理层芯片接收出错。

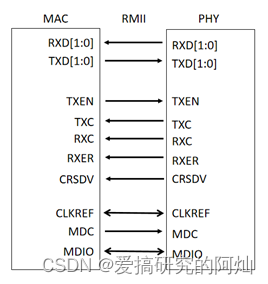

连接方式

MAC-to-PHY的RMII连接

MAC-to-PHY的RMII连接比较简单,直接将相应信号连接起来即可。

审核编辑:汤梓红

-

DP83910A CMOS SNI 串行网络接口:技术解析与应用指南2025-12-18 378

-

浅析以太网接口及串口转以太网技术2023-09-26 9189

-

SSSMII接口2023-03-29 2502

-

ARM与FPGA的接口实现的解析2021-07-22 1211

-

深入解析传感器网络中实时通信的研究2021-05-26 1519

-

MII接口有什么功能?2019-10-18 1940

-

如何使用多个网络接口2019-07-16 3996

-

解析蓝牙mesh网络2017-09-25 4145

-

以太网接口知识2016-03-09 757

-

ATM网络接口,ATM网络接口类型有哪些?2010-04-06 6224

-

IP网络存储的网络接口2010-01-09 1056

-

网络电话的网络接口2009-12-31 2826

-

路由器网络接口解析2009-08-01 2264

-

PS/2接口协议解析及应用2006-07-03 3076

全部0条评论

快来发表一下你的评论吧 !