基于28nm工艺制程的7系列FPGA

描述

全局时钟管脚

7系列FPGA是基于28nm工艺制程。在7系列FPGA中,每个输入/输出区域(I/O Bank)包含50个输入/输出管脚,其中有4对(8个)全局时钟管脚,称之为CCIO(Clock-capable IO)。每对CCIO包含一个P端和一个N端,用于构成差分IO,从而使得输入时钟支持差分时钟。如果外部时钟是单端时钟,则需要连接到CCIO的P端。

此时,相应的N端只能用作通用IO,而不能再当作另一个全局单端时钟管脚。在这4对CCIO中,有2对MRCC(Multi-regionClock-capable),2对SRCC(Single-region Clock-capable)。当它们未被当作时钟管脚使用时,可用作通用IO。

时钟缓冲器

7系列FPGA中的时钟缓冲器分为全局时钟缓冲器(GlobalClock Buffer)和区域时钟缓冲器(Regional Clock Buffer)。全局时钟缓冲器是指由BUFGCTRL配置成的BUFG、BUFGCE、BUFGMUX和BUFGMUX_CTRL。7系列FPGA有32个全局时钟缓冲器。这32个全局时钟缓冲器位于全局时钟列,不属于任何时钟区域(ClockRegion)。

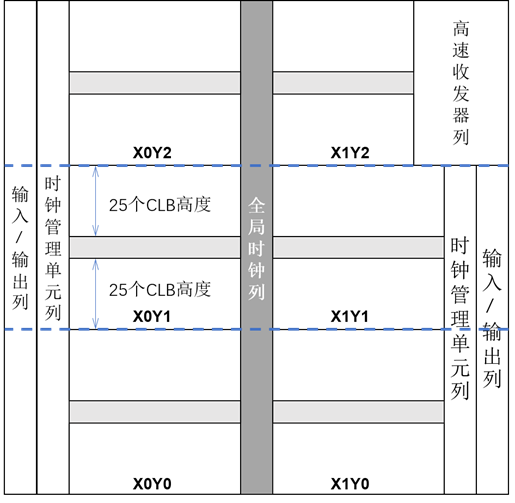

其中有16个位于全局时钟列的上侧,另外16个位于全局时钟列的下侧,如下图所示。图中XmYn是时钟区域坐标,每个时钟区域的高度为50个CLB(Configurable Logic Block),宽度为整个芯片宽度的一半。同时,还可以看到全局时钟列位于芯片的中心位置,垂直时钟布线资源也位于此。水平时钟布线资源则位于每个时钟区域水平方向的中心位置。

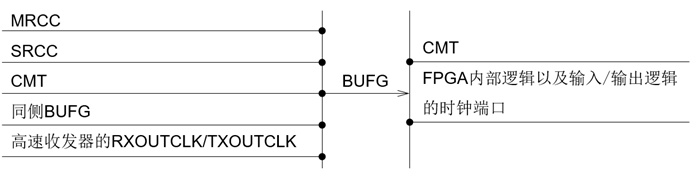

之所以称之为全局时钟缓冲器是因为它们输出的时钟可经全局时钟树(GlobalClock Tree)到达FPGA内部逻辑以及输入/输出逻辑(指ILOGIC和OLOGIC,位于输入/输出区域)的时钟端口,而其输入时钟可来自于与之同侧的MRCC、SRCC、CMT(时钟管理带,Clock Management Tile,一个CMT包含一个MMCM和一个PLL)、BUFG或高速收发器的输出时钟RXOUTCLK/TCOUTCLK,如下图所示。

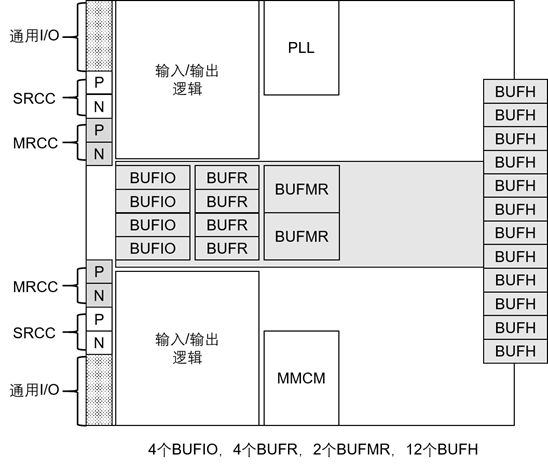

区域缓冲器也称之为局部缓冲器,包括BUFH、BUFIO、BUFR和BUFMR。之所以称之为区域缓冲器是因为它们输出的时钟经区域时钟树(RegionalClock Tree)之后可到达特定区域内的逻辑的时钟端口。区域缓冲器隶属于时钟区域。每个时钟区域包括12个BUFH、4个BUFIO、4个BUFR和2个BUFMR,如下图所示。

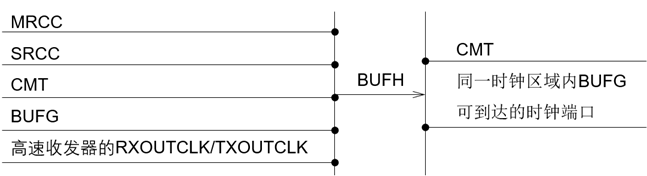

BUFH的输入时钟可来自于与之同一时钟区域或相邻水平时钟区域内的MRCC、SRCC、CMT、BUFG或高速收发器的输出时钟RXOUTCLK/TCOUTCLK。

BUFH的输出可连接到CMT的时钟端口或本时钟区域内BUFG可到达的时钟端口,如下图所示。相比于BUFG,BUFH具有更低的功耗,同时输出时钟抖动更小。此外,BUFH还可配置为带时钟使能的BUFHCE,从而实现门控时钟功能。

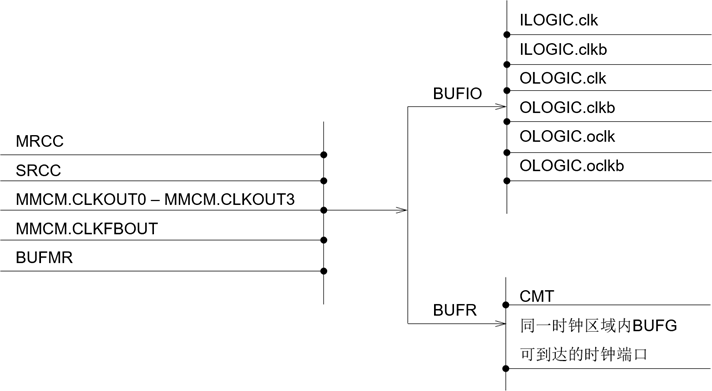

BUFIO和BUFR的输入时钟均可来自于与之同一时钟区域内的MRCC、SRCC、MMCM的输出时钟CLKOUT0~CLKOUT3、MMCM的输出反馈时钟CLKFBOUT或BUFMR。

BUFIO的输出时钟只能驱动ILOGIC和OLOGIC。BUFR的输出时钟可驱动CMT或与之同一时钟区域内的逻辑资源,包括ILOGIC和OLOGIC,如下图所示。此外,BUFR还具备分频功能,可支持的分频因子为1~8(包含1和8)的整数。

应用案例

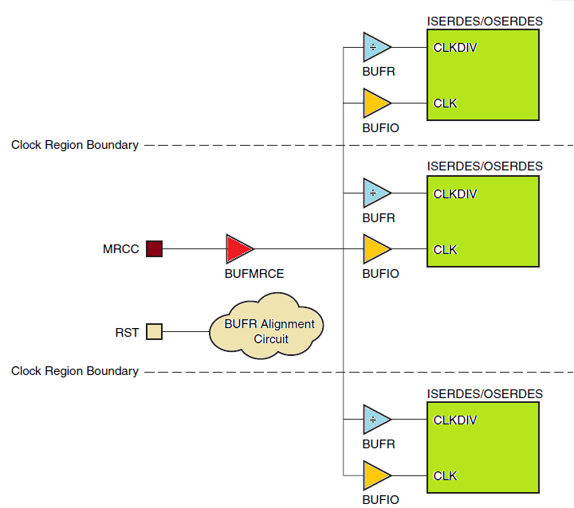

我们看一个应用案例。在源同步设计中,我们可能用到ISERDES/OSERDES。这两个模块都有CLK/CLKDIV。其中CLKDIV由CLK分频得到。

由于二者均在IOB里,所以可以用BUFIO驱动时钟CLK,借助BUFR的分频功能生成CLKDIV。如果ISERDES/OSERDES在多个IOB内,那么就需要BUFMR,因为BUFR只能驱动所在Bank的资源,如下图所示。时钟由MRCC管脚进入,连接BUFMR。

审核编辑:刘清

-

面向低成本及中端应用的28nm FPGA2011-01-26 1075

-

令人侧目的Altera 28nm FPGA芯片?2012-09-21 16606

-

如何利用28nm高端FPGA实现功耗和性能的平衡?2019-09-17 2915

-

请问C2000系列产品的制程是45nm还是28nm?2020-06-17 2155

-

台积电年中将为Altera试产28nm制程FPGA芯片2010-02-05 911

-

28nm Stratix V FPGA突破带宽瓶颈2010-05-10 1063

-

降低赛灵思28nm 7系列FPGA的功耗2012-03-07 742

-

赛灵思28nm系列的里程碑–首批Artix-7 FPGA出货2012-07-20 2442

-

Cyclone V系列28nm FPGA:市场功耗最低、成本最低2012-09-04 3818

-

Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex2017-02-11 3904

-

超越--赛灵思7系列28nm FPGA产品发布会2018-06-05 4996

-

紫光推出Logos-2系列,采用28nm CMOS工艺制程2020-03-18 5398

-

半导体制程发展:28nm向3nm的“大跃进”2020-10-15 6964

-

Omdia 研究报告,28nm 将在未来 5 年成为半导体应用的长节点制程工艺2020-12-03 3601

-

复旦微去年上半年28nm工艺制程FPGA的毛利率水平分别为98.48%和99.6%2021-01-11 3186

全部0条评论

快来发表一下你的评论吧 !