如何排除DC-DC降压转换器的故障

描述

本文解决了并不总是按计划工作的主要电子系统的故障排除:开关模式、低压、DC-DC、单相、非隔离、基本降压转换器电路。

转换器故障排除的一般规则

进行故障排除时,重要的是要考虑哪些变量在起作用,并减少可能的故障原因的数量。

以下是一些可以帮助您的指南:

您需要可靠地使系统无法对其进行故障排除。一个自行消失的问题会自行卷土重来。

一次只改变一件事并注意效果。

如果电路停止工作,问“发生了什么变化?” 是否有与失败同时发生的事件?

查看故障是否随转换板、芯片或负载移动。

考虑到这些概念,以下是您在设计 DC-DC 降压转换器时可能遇到的九个常见问题以及一些可能的原因。

问题 #1:纹波太多

如果您看到太多纹波,电感值可能太低——较高的值会产生较低的纹波,但瞬态响应较慢。

此外,请记住大电感纹波电流意味着更高的峰值电流和更大的电感饱和可能性,尤其是在高温下——以及对 FET 的更大压力。

其他问题可能是C out太低(没有足够的存储空间来支撑输出)或C out ESR(等效串联电阻)太高(导致C out中的 IR 压降)。

最后,低开关频率会导致更多纹波。

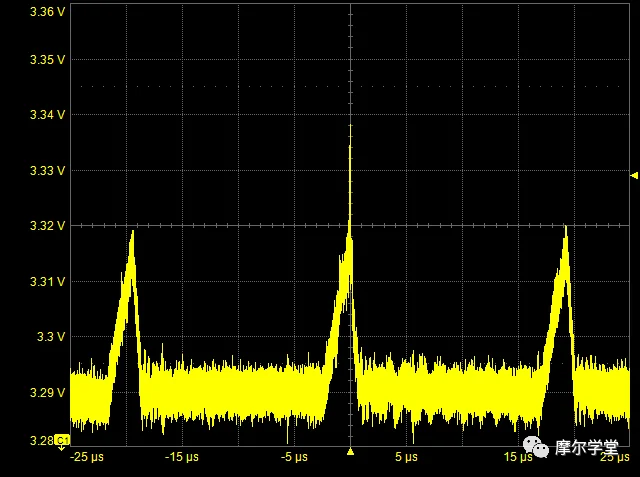

使用 10 倍探头测得的噪声。Eric Bogatin 在“如何测量开关模式电源 (SMPS) 中的噪声”中的截图

问题 #2:无法启动

首先,问自己这个问题:“启用”引脚是否正确驱动(或上拉)?电源良好输出也一样。

启动失败可能是因为您看到过大的负载电容(如 FPGA)就像短路一样并触发了电流限制。一些芯片具有消隐和软启动功能来解决这个问题。

将电流限制点设置得尽可能高以避免误报,并与 FPGA 工程师协商以优化系统级别的电容。

最后,确保V in没有下垂,并且 UV 锁定没有因输入压降而激活。

问题 #3:关闭时输出端存在电压

如果您的电路确实关闭但您看到输出端有电压,则它通常来自另一个电源电路。检查到其他活动轨道的非明显路径。

问题#4:监管不当

对于远程V out感测,电源路径欧姆压降可能会导致调节不良,这可能是由于电源轨(单电源转换器输出线)分配给电路板上的太多负载。这就是为什么有时会避免使用多轨转换器 IC(“PMIC”)以支持负载旁边的多个转换器。

如果您的电压检测引脚有噪声,请保持该引脚的布局整洁,并确保与检测信号相关的任何电阻器都放置在控制器附近。

另一种解释是你的参考电压可能在过滤不足时不稳定。

问题 #5:瞬态响应缓慢

这里的罪魁祸首是可能有太多的大容量输出电容或太大的电感器。

另一个问题可能是环路补偿不良。如果没有合适的设备,环路特性很难完全表征。但是,即使您没有网络分析仪,也可以使用阶跃负载并观察瞬态振铃——它会告诉您很多便宜的事情。

此外,在开发过程中,如果设计负载发生变化,补偿通常也必须发生变化。例如,您是否在其设计负载的一半时使用工厂评估模块?你看到了问题。

问题#6:不稳定

C out ESR 可能是不稳定的原因,因为它在环路响应中引入了零,这使得增益曲线停止下降并开始横向移动,侵蚀或消除增益裕度。如果零频率足够低,则在相位达到 180° 之前增益不会超过零。

较便宜的转换器芯片可能会进行内部补偿以节省外部零件,但请确保您的C输出满足它们稳定的最小和最大C输出ESR 范围。

对不稳定性的其他解释可能包括不良电压检测或求和节点布局或噪声。

请务必使用设计软件生成波德图并检查相位和增益裕度,包括过温情况。

问题 #7:效率低下

自举电容器需要足够大,以便为高侧 FET 栅极提供电荷——否则,该 FET 可能无法完全导通,然后会烧毁电源。与升压引脚串联的电阻可用于调整开启以控制振铃。

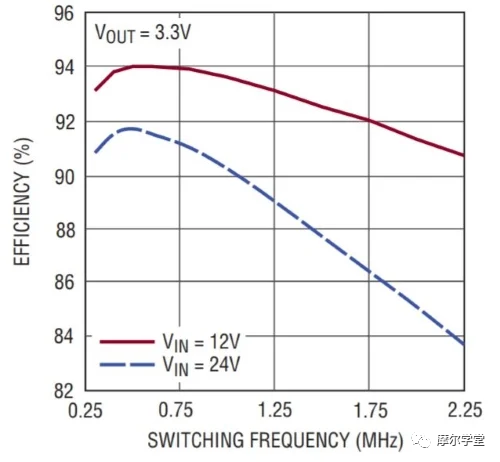

测量电源电路效率(尤其是 90% 以上)并非易事,因为它需要电流测量并且是两个功率量的比率。希望您已经通过电子表格工具描述了每个组件对损耗的贡献,该工具通常会告诉您 MOSFET 和电感器电阻(“DCR”或直流电阻)是浪费热量的主要来源。

显示降压开关稳压器的效率与频率的关系图。绘图取自 Linear Tech/Analog Devices 的LT8610 数据表。

问题 #8:低温问题

请记住,低温下电解电容的 ESR 会升高,电容也会下降。

问题 #9:PMBus 问题

在共享数据通信总线上,确保在您不注意时另一个节点不会间歇性地抖动。

此外,请确保您使用的上拉电阻足够强:47kΩ 上拉电阻(如 FPGA)不如 10kΩ 好。

结论

如果您完全不知道该怎么做,请获取更多数据——这将为您提供一些分析依据、从中产生想法并促进团队讨论。

审核编辑:汤梓红

-

双通道降压型 DC-DC 转换器 skyworksinc2025-07-24 85

-

DC-DC降压转换器的常见故障与排除方法2024-05-21 9214

-

降压型DC-DC转换器与升压型DC-DC转换器的输出纹波差异2024-04-24 3344

-

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理2023-09-19 5788

-

如何排除DC-DC降压转换器故障?2023-09-18 1635

-

DC-DC降压转换器PCB布局的技巧2023-06-19 3334

-

DC-DC降压转换器工作原理! #硬声创作季学习硬声知识 2022-10-30

-

DC-DC降压转换器工作原理!#电路原理学习电子知识 2022-10-20

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7242

-

什么是DC-DC转换器?DC-DC转换器是如何命名的?2021-11-09 5296

-

非隔离式的DC-DC转换器解析2020-12-09 5673

-

DC-DC降压转换器电路布局与设计和实践2019-07-11 13633

-

DC-DC转换器2010-03-09 4151

-

DC-DC转换器是什么及其参数2009-11-14 21298

全部0条评论

快来发表一下你的评论吧 !