AD9545输入端与输出端信号延迟问题解析

描述

AD9545 输入端与输出端信号延迟问题

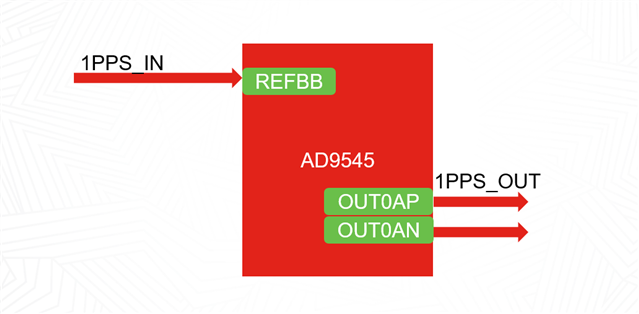

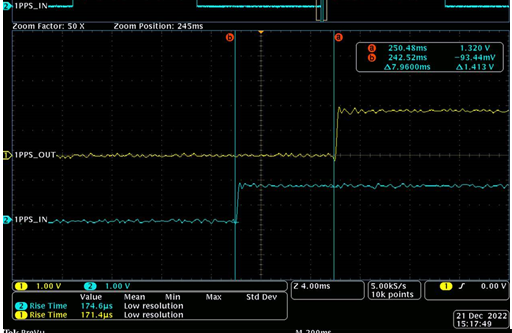

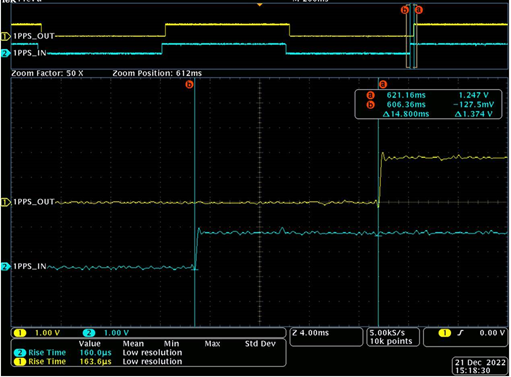

目前使用AD9545方案,备注:1PPS_IN为上升沿500ms的1HZ的时钟信号,Rise time 160us左右,现在有以下问题请帮忙Spport一下

1:目前1PPS_IN与OUT有非固定的延迟,最大15ms左右,我们这边测试0x3100和ox3200,一直是0x28, APLL锁定了的,想咨询一下这个延迟有哪些原因可能导致,

2:当输入端输入上升沿10ms的1PPS信号后,输出还是500ms的上升沿,请问有什么原因可能导致此类问题么?

根据您的描述,您是想实现1pps的0延时功能,也就是说输出的1pps需要和输入的1pps有个固定的0时延。

AD9545支持DPLL的两种配置模式,第一种是PBO,这种模式下每次上电初始化锁定后,输出和输入会保持固定相位差,但这个相位差根据每次锁定时候的初始值会是一个随机指,也就是说PBO模式下保证输入输出频率锁定,相位固定但每次不确定。

第二种是0延时模式,该模式下输入和输出的1pps可以保证每次锁定后上升沿严格对齐。这两种模式的配置差异很大,有很多细节包括配置的细节和其他实现的细节需要考虑,请联系你们的ADI的支持渠道(可以通过sales/fae来找AE支持)来获取详细的技术指导,在EZ上很难实现详尽的解答。

关于您上面描述中的一些问题,我一一答复如下:

1:“1PPS_IN为上升沿500ms的1HZ的时钟信号,Rise time 160us左右”, 上升沿500ms应该是想表达高电平脉宽500ms的时钟,rise time160us的可能性不大,可能是测试的示波器采样率太低带宽太小造成的偏差。9545对1pps的上升沿时间有具体spec需求定义,详见datasheet。但对9545的输入而言,只有上升沿信息是有效信息,高电平脉宽信息不需要。

2:0x3100和ox3200,一直是0x28,所以APLL锁定了,但DPLL一直没有锁定,此时输入1pps和输出1pps的相位是一直变化的状态,而且由于没有更多寄存器信息,所以并不能判断此时的DPLL状态,是否参考有效稳定(0x3005~0x3008)?DPLL是否处于跟踪锁定或其他状态状态(0x3101/3201)?

3:“当输入端输入上升沿10ms的1PPS信号后,输出还是500ms的上升沿”。这里上升沿10ms应该还是想指高电平脉宽10ms,前面说过,只有上升沿信息有效,也就是说只有上升沿的沿位置是被9545采样的信息,后面脉宽多长不做任何处理,不会影响内部电路,然后9545的任何输出频率都是50% duty cycle的信号,包括1pps,而且这个duty cycle不能调节。

审核编辑:刘清

-

AD9545 IEEE1588第2版及1 pps同步器和自适应时钟转换器技术手册2025-04-09 1414

-

单端输入和双端输入的区别是什么2024-07-31 6625

-

比较器输入端和输出端的关系2024-07-10 5052

-

光耦失效的几种常见问题解析2023-12-25 10155

-

差分放大电路中,单端输入和双端输入两种输出值是否相同?为什么呢?2023-11-20 6984

-

时钟同步器AD9545能否实现0延时?2023-03-08 2149

-

关于SIGNAL输入/输出端的信号协议2022-10-14 2965

-

AD9545 IBIS型号2021-05-28 615

-

AD9545原理图2021-05-25 958

-

UG-1146:AD9545寄存器映射参考手册2021-05-21 1055

-

AD9545革资料2021-03-23 703

-

AD9545 IBIS Model2021-02-19 921

-

AD9545 Gerber Files2021-02-01 802

-

AD9545 IEEE1588 第 2 版以及 1 pps 同步器和自适应时钟转换器2019-02-15 1145

全部0条评论

快来发表一下你的评论吧 !