三分钟教你快速处理没有使用的端口信号

描述

编 者 按

用DataAnalyzer快速处理没有使用到的端口信号

避不开的场景 如果熟悉SpinalHDL设计,那么都应该清楚在SpinalHDL设计里,如果输出端口没有给明确赋值的话,那么在生成RTL代码时会报错提示我们没有为端口赋值。想想如果你在设计一个AXI4的测试逻辑,但你并不需要使用里面的全部信号(要知道AXI4总线配置里面的哪个信号使用哪个不使用可使一大堆参数),如果想要做的模块在任何场景下都能直接连接使用的话,最早对于我没有使用的信号我是这么来处理的:

if(axi4Port.useRegion) axi4Port.clearAll() if(axi4Port.useLock) axi4Port.lock.clear() ……是不是写起来很啰嗦?~ 还有一个场景就是在FPGA里面在制作PR版本时对于动态区和静态区之间的接口信号为了方便后续Impl版本的时序收敛,对于没有使用到的信号以及赋常值的信号都建议添加约束:

对于输入没有使用到的信号,内部定义一个寄存器来锁存信号,并把这个寄存器的属性设置为nopurne

对于暑促好信号,则建议将输出信号必须为reg类型,并将该输出信号配置为preserve属性。

对于这种使用不到的信号,一个个的follow这些原则不免有点儿太过于“体力活”~ 而在SpinalHDL里,我们可以通过DataAnalyzer来快速地实现这些没有使用到的端口信号。 》DataAnalyzer

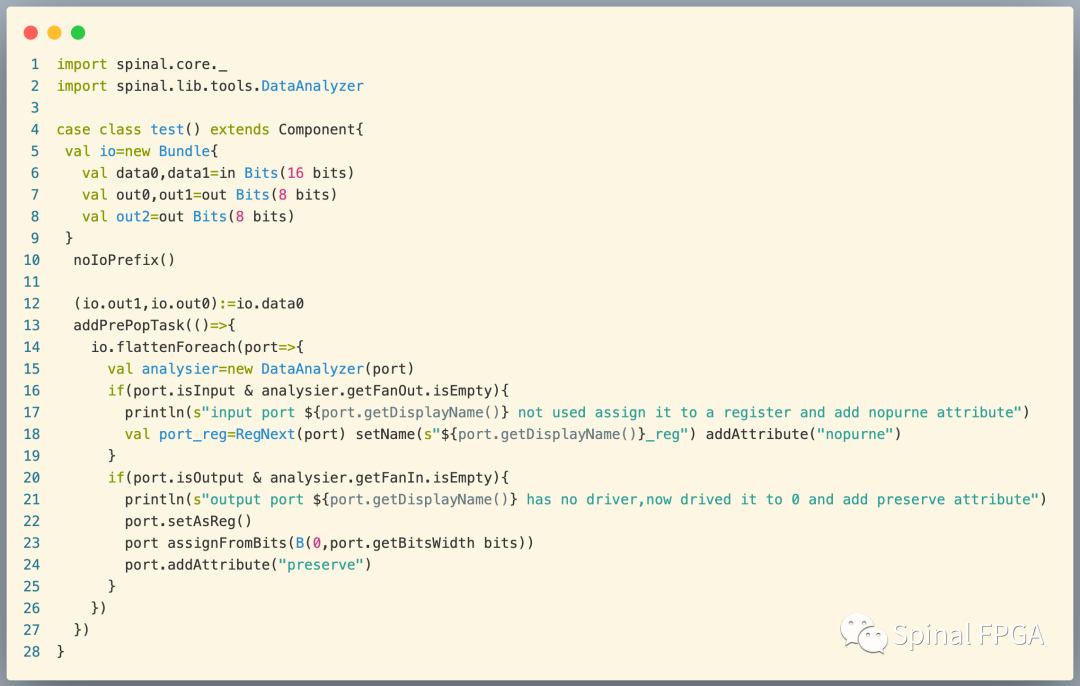

考虑下面这个简单的模块:

在这个模块里,对于输入的data1接口我们并没有用,而对于输出out2端口,我们也并没有输出赋值。

现在,如果我们想要实现针对PR那种场景的需求,我们可以通过DataAnalyzer来写一个通用的处理代码:

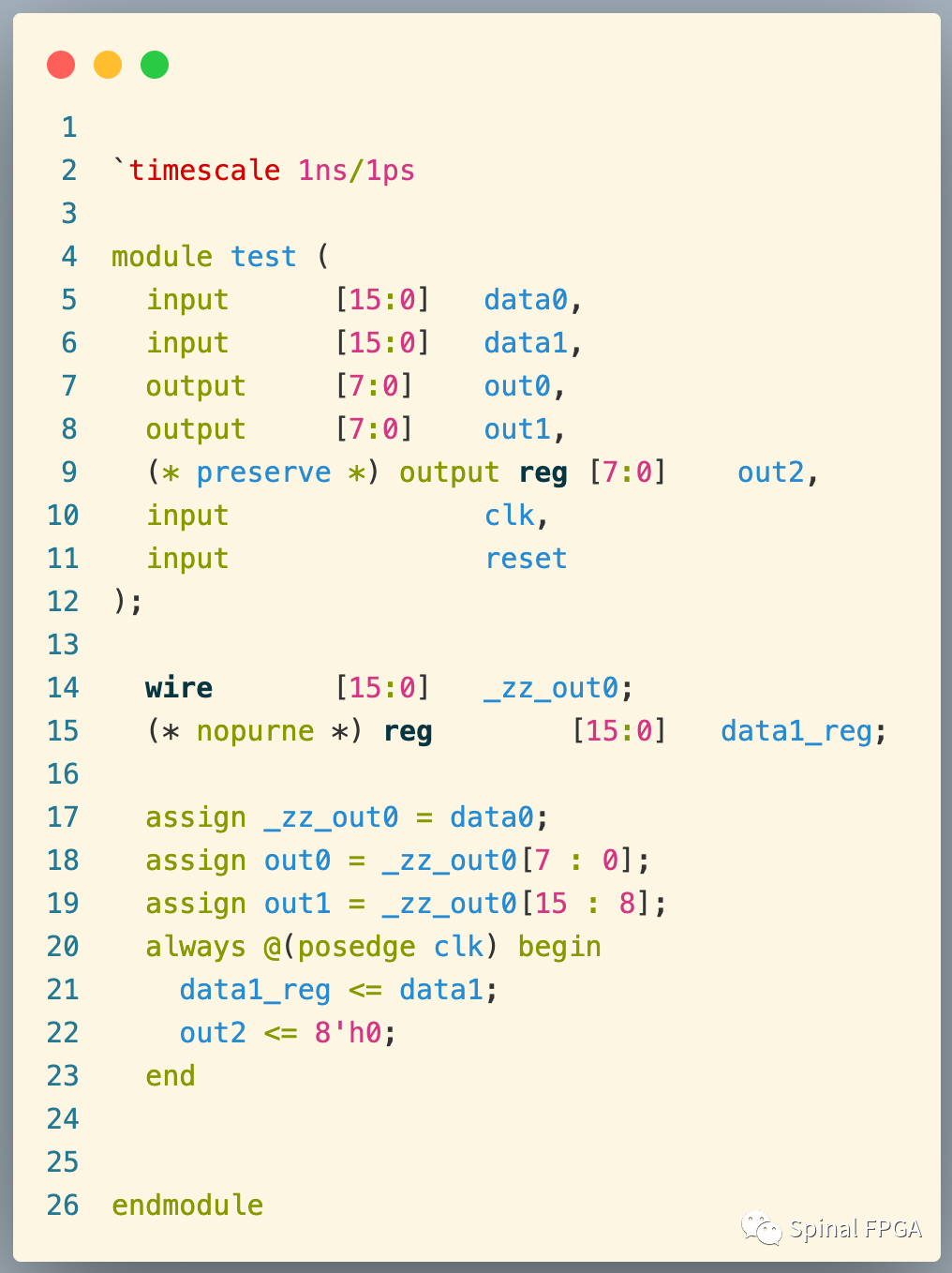

这里我们为模块添加一个PrePopTask。对于io里面的每个信号,都例化一个DataAnalyzer,对于接口为输入信号(port.isInput),并且其没有任何扇出信号(analysier.getFanOut.isEmpty),则将其赋值给一个寄存器,并对该寄存器添加“nopurne”属性。而如果接口信号为输出信号(port.isOutput),并且没有任何的信号给他赋值(analysier.getFanIn.isEmpty),则将其设置为寄存器,赋值为0并添加“preserve”属性。最终生成的代码:

完全符合我们的需求~

结语

能省功夫就省功夫,在Boss的许可下,选择尽可能高效的工具,这周工作里修改一个Verilog代码,在SpinalHDL里面五分钟能实现的需求Verilog里改了小半天,极大打击工作热情~

-

免费三分钟2009-03-02 4509

-

让程序运行三分钟,停一分钟,循环下去,直到设置停止循环的位置2022-06-08 11048

-

三分钟让你明白电池为什么会鼓包2009-11-12 71553

-

Inout双向端口信号处理方法2011-11-11 4142

-

三分钟能做什么?三分钟能让我的iPhone6s重启N次!2017-02-25 2785

-

小米扫地机器人台湾开售 三分钟售罄2017-04-07 1424

-

三分钟来快速回顾!11月无人机大事件2020-11-23 2862

-

三分钟概述8类常用元器件资料下载2021-03-28 1569

-

三分钟看懂工字型功率电感外观破损的常见原因gujing2022-11-09 1225

-

Brocade帮助Netzlink实现三分钟云服务供应2023-08-29 408

-

快乐解说MCU:三分钟,带你了解低功耗MCU2023-09-18 2107

-

三分钟实现MQTT协议网关串口连接三菱FX3UPLC上传腾讯云2023-10-23 1910

-

三分钟看懂雪崩光电二极管2023-11-23 3474

-

三分钟了解飞创直线电机运动模组特点、选型及应用-FCL系列2024-02-05 1327

-

Node-RED初学者教程-三分钟学习2024-06-27 6864

全部0条评论

快来发表一下你的评论吧 !