插值法帧同步解析

描述

1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)帧同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:195.3125kbps

数据内容:帧长16位,帧同步字长7位,同步字为1011000

2) 接收端

系统时钟:发送端送来的数据时或信号,195.3125kbps

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数可通过修改程序参数快速设置。

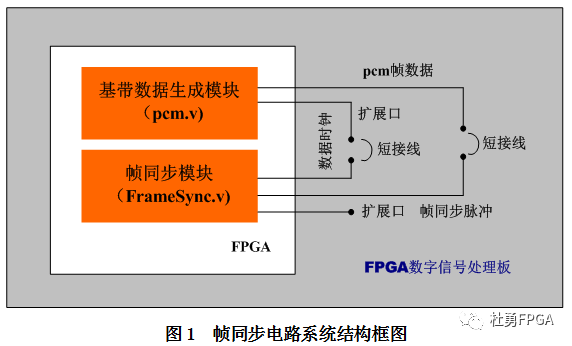

3 程序结构框图说明

帧同步电路系统主要由基带数据生成模块(pcm.v)、帧同步模块(FrameSync.v)模块组成。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是线性插值?一维线性插值和双线性插值在BMS开发中的应用2023-12-24 16136

-

一文简析插值法帧同步2023-02-10 1509

-

插值法帧同步ISE/Verilog/CXD301介绍2023-02-08 2073

-

帧同步通常采用的方法有逐位调整法和置位调整法,对比分析哪个好?2021-04-14 2116

-

基于FPGA的帧同步系统设计方案2013-11-11 5942

-

FPGA设计中帧同步系统的实现2012-08-11 4244

-

一种基于插值算法符号同步的硬件设计2010-07-05 985

-

帧同步,帧同步是什么意思2010-03-17 24798

全部0条评论

快来发表一下你的评论吧 !