多相切换器减少了元件数量,实现了更小、更便宜的移动CPU电源

描述

LTC1709-7 利用了多相的优势™开关技术可减少输入电容器的数量和电感器尺寸,并延长电池寿命。随着 CPU 时钟频率的增加,对内核电源电流的需求也随之增加。当今的 22A CPU 内核电流要求将单级开关稳压器推向了极致。LTC1709-7 中设计的多相开关允许使用成本更低、外形更紧凑的部件,并且还改善了瞬态响应。

LTC®1709-7 是一款双通道、电流模式、多相控制器,其驱动两个同步降压级 180° 异相。这款小型 SSOP-36 封装控制器集成了四个高电流 MOSFET 驱动器、一个用于真正输出远程检测的差分放大器、自动均流电路、一个电源良好指示器和 5 位移动 VID 控制。LTC1709-7 还具有在轻负载条件下的突发模式操作和不连续导通模式操作。由此产生的电源解决方案在任何负载条件下都非常高效,并且占用最小的电路板空间。

1 步、2 相 CPU 内核电源

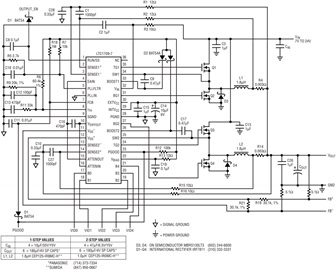

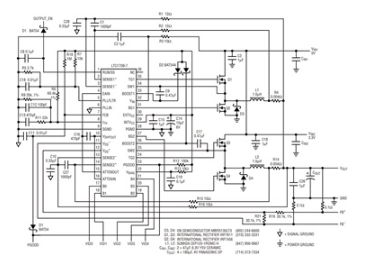

图 1 示出了将 LTC1709-7 用于 CPU 内核电源的典型应用电路。在 1 步配置中,CPU 内核电压直接从墙上适配器或电池降压。输入电压可在 7V 至 24V 之间。输出电压介于 0.925V 和 2V 之间,由 5 位 VID 输入设置。该电源将为 CPU 内核提供 22A 的最大电流。仅采用 8 个 IC、1 个 SO-8 MOSFET 和 83 个 20.1μH 扁平表面贴装电感器,8V 输入和 22.80V/4A 输出的效率高达 22%。在 200A 至 <>A 的负载范围内可保持超过 <>% 的效率。由于输入电压较高,底部MOSFET的体二极管中的反向恢复损耗可能很大。肖特基二极管需要与底部MOSFET并联,以缓解反向恢复问题。由于最大输入电压下的开关损耗相对较高,因此选择了<>kHz的开关频率。

图1.单输入、1 步或 2 步 LTC1709-7 CPU 内核电源。

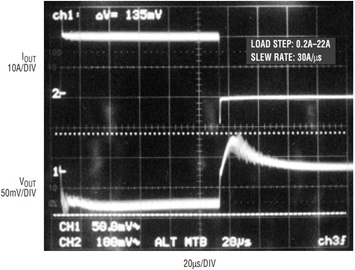

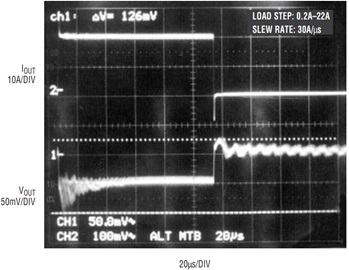

图2显示了在20V输入和1.6V输出下测得的负载瞬态波形。负载电流在0.2A至22A之间变化,压摆率约为30A/μs。由于输出上只有六个低 ESR SP 电容 (180μF/4V),负载瞬变期间的最大输出电压变化小于 140mVP-P.请注意,由于稳态占空比较小,高到低负载阶跃响应比低到高负载阶跃响应慢。本设计采用有源电压定位以减少输出电容器的数量(有关有源电压定位的更多详细信息,请参阅凌力尔特设计解决方案 10)。R9和R6提供输出电压定位,不会降低效率。

图2.图1电路的瞬态响应(1步版本);V在= 20V, C外= 六个 SP 帽。

2 步、2 相 CPU 内核电源

在前面描述的1步解决方案中,CPU内核电源的输入电压可高达24V。由此产生的低占空比会减慢高到低负载瞬态响应(如图2所示),并增加同步FET中的电流应力。这增加了输出电容和MOSFET的尺寸和成本。高输入电压还会增加顶部 MOSFET 中的开关损耗和功耗。为了尽量减少内核电源中产生的热量,CPU内核电源最好从低输入电压源(如5V系统电源)获取电源。由于5V电源通常由电池或墙上适配器产生,因此这种方法总共需要两步电源转换。

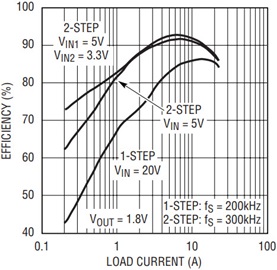

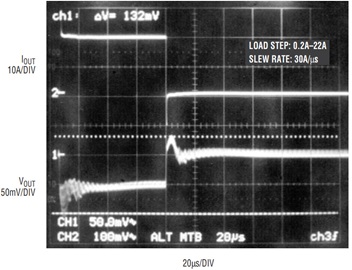

5V输入、两步CPU内核电源设计与图2所示几乎相同。唯一的区别是图 1 表中所示的组件更改。如图1所示,与3步解决方案相比,2步设计将轻负载效率提高了20%,满载效率提高了2%。如图1所示,负载瞬态响应也得到了改善。由于输出端的SP电容少了两个,两步电路实现了与4步相似的性能。

图3.1 步和 2 步设计的效率与负载电流的关系。

图4.图1电路的瞬态响应(2步版本);V在= 5V, C外= 四个 SP 上限。

因为 CPU 功率可以大于 40W,所以为 LT5-1709 供电的 7V 电源的输出电流额定值可能超过 15A。这将显著增加5V系统电源电路的功率损耗、成本和尺寸。如果 3.3V 和 5V 系统电源由两相 LTC2 电路产生,则 LTC1876 电路中两个降压通道的功率不平衡会降低输入纹波电流消除的有效性。LTC1876 电路的输入侧必须使用更多的高电压电容器 (>25V)。有关更多信息,请参见 LTC1876 的产品手册。

为了提高为 LT1876-1709 供电的 LTC7 电路的效率并降低总体成本,可能需要从两个不同的电源 3.3V 和 5V 获取 CPU 内核电源,如图 5 所示。这样,就可以优化 3.3V 和 5V 电源的设计,以最大限度地减小 LTC1876 电路的功率损耗。此外,由于2.3V输入通道上的开关损耗更低,3输入设计进一步提高了轻负载效率。然而,由于没有输入纹波电流消除,因此2输入设计需要在3.3V和5V电源轨上使用更大的滤波电容;如图5所示,从低到高的负载阶跃响应将比单6V输入设计慢,因为3.3V输入通道具有较少的电压来增加电感电流。有关 2 输入、2 相设计的更多信息,请参见凌力尔特设计说明 222。

图5.2 输入、2 步 LTC1709-7 CPU 内核电源。

图6.图5电路的瞬态响应(1步版本);V合1= 5V, V合2= 3.3V, C外= 四个 SP 上限。

表 1 比较了不同设计方法的性能。显然,在CPU电源的性能和尺寸方面,2步设计比1步设计更具优势。5V 输入、2 步设计在内核电源中具有最佳性能。

|

1-Step VIN = 20V |

2-Step |

|

| VIN = 5V |

VIN1 = 5V VIN2 = 3.3V |

|

|

Efficiency at VOUT = 1.8V |

IOUT = 0.2A | 43% |

| IOUT = 22A | 83% | |

|

CIN |

4 × 10µF/35V/Y5V ceramic caps | |

|

COUT |

6 × SP caps | |

|

Inductors |

2 × 1.8µH | |

|

Load transient response: 0.2A–22A |

< 140mVP-P | |

|

Switching frequency |

200kHz | |

结论

基于 LTC1709-7 的低电压、高电流移动 CPU 电源同时实现了高效率和小尺寸。电容器、电感器和散热器的节省有助于最大限度地降低整体电源的成本。本文介绍的 LTC1709-7 电路适合为需要大内核电源电流的高速移动 CPU 供电。与 1 步解决方案相比,2 步设计提供了更好的内核电源效率,并且需要更小的输出电感器和电容器。

审核编辑:郭婷

-

kvm切换器怎么实现键盘热键切换2024-10-17 5117

-

无缝高清矩阵切换器和传统的矩阵切换器有什么区别?2024-01-24 1320

-

HDMI无缝切换器真的是无缝切换吗?HDMI无缝切换器怎么用?2023-12-04 2525

-

集成解决了铁路行业的电源设计挑战2022-08-18 1274

-

减少了组件数量的隔离式正向 DC/DC 转换器2021-03-19 818

-

KVM切换器和KVM矩阵的区别2019-11-19 6635

-

矩阵切换器怎么分类?2019-10-23 2693

-

什么是电脑切换器?4路KVM切换器介绍2018-06-29 5564

-

网络切换器是什么_网络切换器怎么用_网络切换器的操作方法2018-03-29 11080

-

由通用元件组成的8路模拟切换器2010-05-04 2597

-

切换器,切换器的串口/信噪比/屏幕长宽比2010-03-26 770

-

什么是矩阵切换器2009-10-12 2046

全部0条评论

快来发表一下你的评论吧 !