基于20nm工艺制程的FPGA—UltraScale介绍

描述

UltraScale是基于20nm工艺制程的FPGA,而UltraScale+则是基于16nm工艺制程的FPGA。尽管两者工艺制程不同,但内部结构是一致的。若无特殊声明,下文阐述的UltraScale架构也适用于UltraScale+。

全局时钟管脚

在UltraScale中,每个输入/输出区域(I/O Bank)都位于单一的时钟区域CR(Clock Region)内,且都包含52个输入/输出管脚。在这52个管脚中,有4对(8个)全局时钟管脚GC(GlobalClock I/O)。其使用方法与7系列FPGA是一致的。

不同之处在于,这4对GC地位是等同的,不再有MRCC和SRCC之分。UltraScale+新增了高密度输入/输出区域(HD I/O Bank, High Density I/O Bank),位于此区域内的全局时钟管脚HDGC只能通过BUFGCE连接到MMCM或PLL。

时钟缓冲器

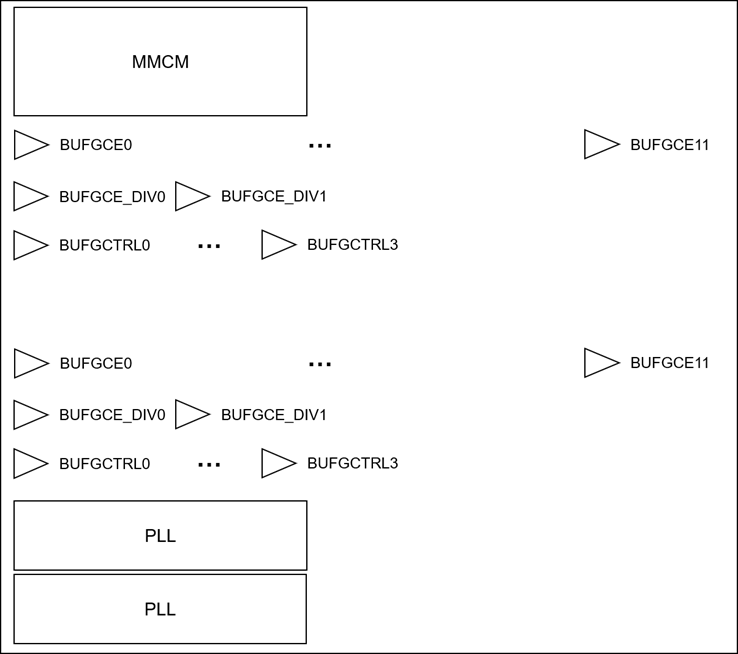

7系列FPGA既包含全局时钟缓冲器,又包含区域时钟缓冲器。UltraScale简化了时钟缓冲器,即只有全局时钟缓冲器。包含输入/输出列的时钟区域内有24个BUFGCE、4个BUFGCE_DIV和8个BUFGCTRL,但同时只能使用其中的24个,如下图所示。

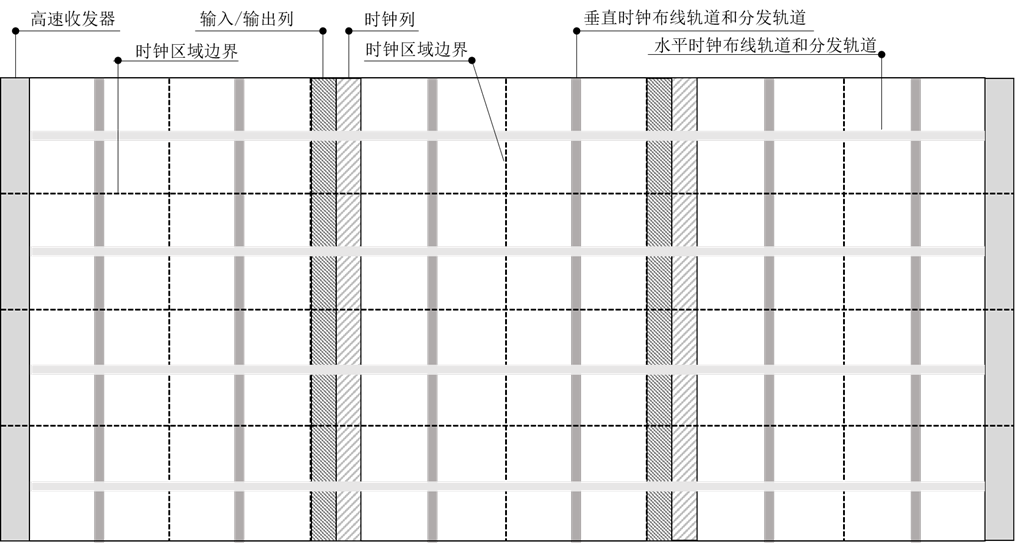

这些全局时钟缓冲器位于时钟列,可驱动水平时钟布线/分发轨道和垂直时钟布线/分发轨道,其中分发轨道是7系列FPGA所没有的。这些轨道均位于时钟区域的中心位置,如下图所示(有的芯片只有一侧会有高速收发器)。不难看出,每个时钟区域的宽度相比于7系列FPGA有所缩减,不再是半个芯片的宽度,高度由7系列中的50个CLB变为60个CLB。时钟区域的粒度更加细化。

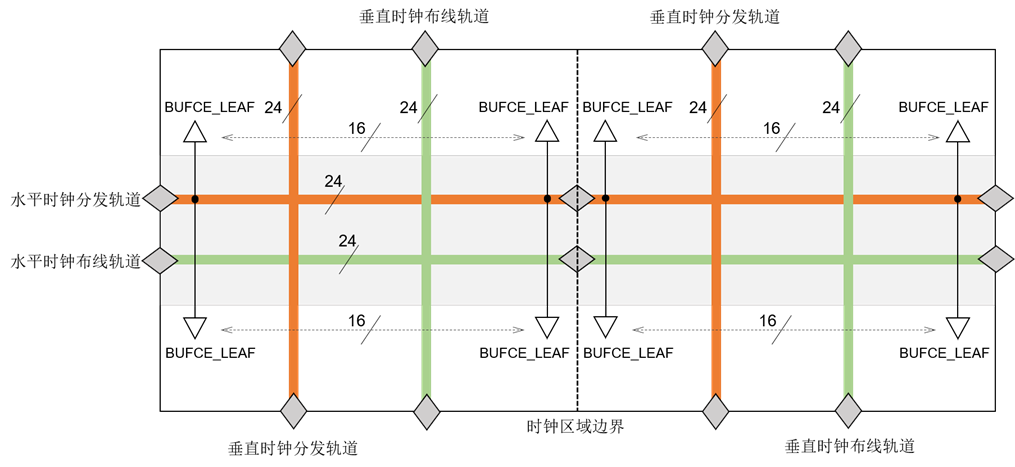

无论是水平时钟布线/分发轨道还是垂直时钟布线/分发轨道,都是以时钟区域作为边界,这意味着如果某个时钟区域内的资源未使用时钟,工具就会关闭相应的轨道,从而节省功耗。布线轨道可驱动相邻时钟区域内的布线轨道和分发轨道,但分发轨道只能驱动相邻时钟区域内的水平分发轨道。

布线轨道的目的是将时钟从全局时钟缓冲器布线到某个中心点。在这个中心点,时钟经分发轨道连接到其负载的时钟端口。分发轨道可进一步移动这个点以改善时钟的局部偏移。这个点我们称之为时钟根节点(ClockRoot)。

每个时钟区域有24个水平时钟布线/分发轨道和24个垂直时钟布线/分发轨道。在水平时钟分发轨道上,有32个BUFCE_LEAF,称之为叶时钟缓冲器。时钟从水平时钟分发轨道上下来之后经BUFCE_LEAF到达逻辑资源的时钟端口,如下图所示。BUFCE_LEAF只能由Vivado自动使用,而不能在代码中实例化。

UltraScale有独立的BUFGCE,无需通过BUFGCTRL配置而成。但BUFGCTRL仍是可配置的,例如,BUFGCE_1、BUFGMUX和BUFGMUX_1都是通过BUFGCTRL配置生成的。BUGCE_DIV取代了BUFR,但比BUFR具有更强大的驱动能力,因为它已成为全局时钟缓冲器。

同时,BUFGCE_DIV还具有分频功能,分频因子可以是1~8(包含1和8)的整数。只是当分频因子为奇数时,输出时钟的占空比将不再是50%。UltraScale新增了BUFG_GT。BUFG_GT只可以由高速收发器或RFSoC中的ADC/DAC模块驱动。

BUFG_GT_SYNC是BUFG_GT的同步器,当Vivado推断出BUFG_GT时会自动在设计中插入BUFG_GT_SYNC。和BUFGCE_DIV类似,BUFG_GT也具有分频功能,可用的分频因子为1~8(包含1和8)之间的整数。分频因子由DIV端口输入。

DIV位宽为3,当其为3’b000时,对应分频因子为1。在包含高速收发器的时钟区域内有24个BUFG_GT。 在Zynq UltraScale+ MPSoC中新增了一种全局时钟缓冲器BUFG_PS(Zynq 7000系列FPGA中是没有的)。该缓冲器位于内部ARM处理器的旁边。

PS侧的输出时钟需经此缓冲器访问PL(Programmatic Logic)侧的时钟布线资源,从而驱动PL侧的逻辑资源。BUFG_PS的个数因不同的芯片而异。例如ZU4EG有96个BUFG_PS,而ZU2CG有72个BUFG_PS。

应用案例:使用BUFG_GT执行简单分频

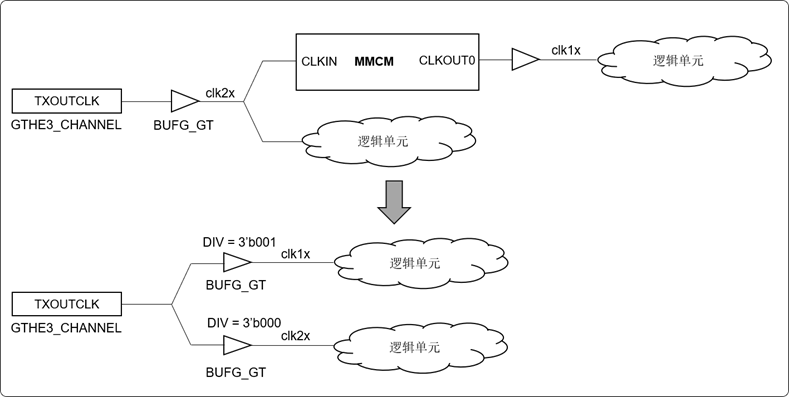

BUFG_GT具有分频功能,可支持的分频因子为1~8(包含1和8)的整数,分频因子控制字由位宽为3的输入端口DIV提供。当DIV为3’b000时,对应分频因子为1。借助BUFG_GT的分频功能可生成分频时钟,从而节省了MMCM,如下图所示。使用BUFG_GT时要注意其时钟源。

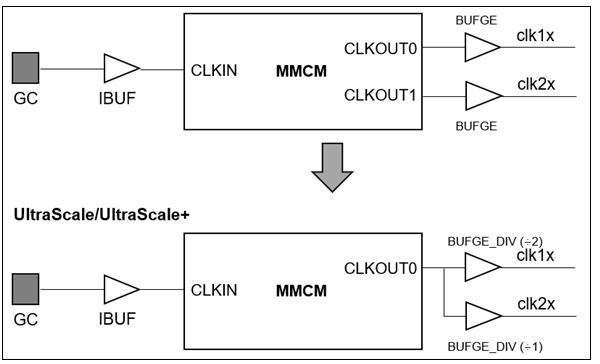

同样具有分频功能的时钟缓冲器还包括BUFGCE_DIV,如下图所示。BUFGCE_DIV的输入可来自于MMCM的输出,图中clk2x的频率是clk1x的2倍。使用BUFGCE_DIV可有效降低同步跨时钟域路径的时钟偏移(Clock Skew)。

审核编辑:刘清

-

唱响2013,20nm FPGA背后蕴藏的巨大能量2013-01-22 1924

-

苹果A8处理器最新消息:采用TSMC 20nm制程工艺2013-12-16 2448

-

Xilinx Ultrascale系列FPGA的时钟资源与架构解析2025-04-24 2910

-

Xilinx UltraScale 系列发布常见问题汇总2013-12-17 4106

-

请问FPGA中的nm是什么意思?2018-10-08 84007

-

台积电又跳过22nm工艺 改而直上20nm2010-04-15 1271

-

台积电将于下月试产20nm芯片2012-07-18 1224

-

深入剖析FPGA 20nm工艺 Altera创新发展之道2012-11-01 2721

-

赛灵思发布UltraScale架构,20nm开始投片2013-07-09 4352

-

Xilinx宣布率先量产20nm FPGA器件2014-12-22 1269

-

Xilinx UltraScale 20nm器件助力打造JDSU ONT 400G以太网测试平台2015-04-09 1125

-

JDSU 400G 以太网测试平台基于Xilinx 20nm UltraScale 器件2017-02-09 464

-

使用Xilinx 20nm工艺的UltraScale FPGA来降低功耗的19种途径2018-07-14 6772

-

Virtex UltraScale FPGA VCU108评估套件的功能介绍2018-11-20 4394

-

赛灵思最新发布的UltraScale+16nm系列FPGA、3D IC和MPSoC介绍2018-12-28 1582

全部0条评论

快来发表一下你的评论吧 !