非隔离式DC-DC转换器的布局注意事项

描述

DC-DC转换器是电场和磁场的极好来源。其EMI频谱从开关频率开始,通常延伸至100MHz以上。为了尽量减少电容耦合和磁耦合,必须在印刷电路板(PCB)布局中小心。必须评估电路的寄生电容和寄生电感,以便在设计阶段的早期进行适当的权衡。

多年来,集成 DC-DC 电源控制器的反复推出为我们提供了更高的性能水平。这些IC通过消除电源设计任务来减轻系统工程师的负担,但这种简化导致了知识的损失。因此,开关转换器应提醒您小心。以下讨论介绍了在为非隔离式DC-DC转换器设计电路板布局时避免意外的规则。

优化这种布局的第一条规则是隔离转换器。DC-DC转换器是电场和磁场的极好来源。其EMI频谱从开关频率开始,通常延伸至100MHz以上。为了尽量减少电容耦合和“磁场到环路”耦合,应将转换器放置在远离其他电路的位置,尤其是低电平模拟电路。

隔离转换器并不总是那么容易。一些电路板在转换器的一侧接受输入电压,在另一侧分配输出电压。例如,VME卡或电信卡包括电流高达20A的非常复杂的路由。单个连接器引入输入电压,并将多个输出电压分配到背板。因此,将转换器放置在此连接器附近以减少电阻降的诱惑力很强。然而,该区域密集的接口驱动器、背板总线等,存在噪声耦合的相关风险。在某些情况下可以添加电源连接器,但该解决方案需要额外的电路板面积和成本。

铜走线中的电阻是最受限制的因素。对于给定长度和厚度的迹线,此电阻为

R = ρ × (升/秒)

其中 l 是以米为单位的走线长度,S 是以平方米为单位的走线面积,ρ(铜的电阻率)是 1.7x10-8Ω - m 在 20°C 或 2.1 x 10-8Ω - 70°C 时的米。 例如,0.5cm宽、35μm厚的铜迹线在20°C时的电阻为1mΩ/cm。该值可能看起来可以忽略不计,但如果通过两个连接器和一个背板将2.5V/10A配电,则会引起注意。

在某些电路板上,走线厚度包括锡铅层。该层几乎可以使等效电阻翻倍:

铅电阻率 = 2.07 x 10-7Ω - 米 20°C

时锡电阻率 = 1.14 x 10-7Ω - 米 在 20°C 时

在精度和走线损耗之间进行权衡,您可以将转换器从连接器移开。您可以通过执行远程 V 来限制电阻降的影响外在连接器附近测量,但要注意电容耦合!要将大电流限制在定义的区域,请将所有电源线通过连接器一端的引脚布线。

场效应管驱动器

随着开关频率的增加,开关时间越来越短:10kHz转换器通常为500ns。在该频率下,即使是最短的走线也具有很大的阻抗。同样重要的是要注意,峰值栅极电流可以在极短的时间内上升到几安培。因此,MOSFET驱动信号的正确路由始于对转换器框图的分析。

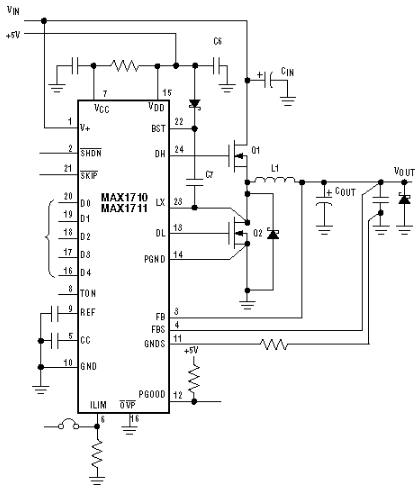

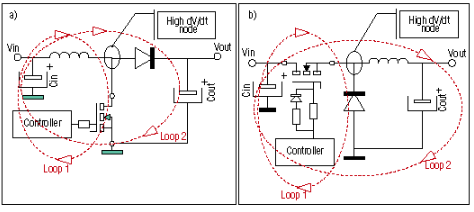

例如,考虑笔记本电脑的同步降压控制器(图 1)。MOSFET 由能量从谐振电容器(C6 和 C7)通过驱动器输出的几欧姆传输到栅极来驱动。请注意,高端n沟道MOSFET (Q1)的栅极驱动是浮动的。n沟道驱动器的工作方式类似于电荷泵!

图 1a.MAX1710同步降压控制器的工作原理由应用电路(a)和内部框图(b)描述。

图 1b.MAX1710同步降压控制器的工作原理由应用电路(a)和内部框图(b)描述。

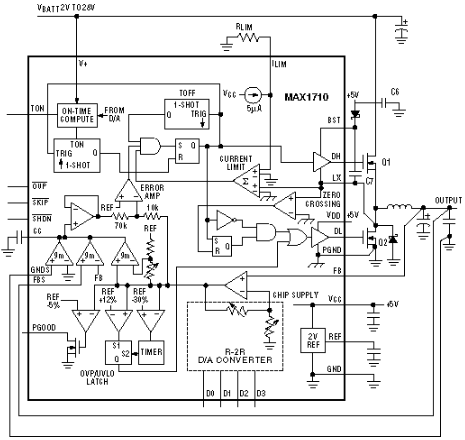

图2突出显示了开启期间的电流路径。任何串联电感都可能导致灾难。在最好的情况下,尖峰较高,但只会增加开关损耗。在最坏的情况下,两个MOSFET可能会因交叉导通(同时导通)而爆炸。因此,最佳布线意味着以下各项之间的走线非常短且很宽:

C6 和 Vdd

C6 和 Q2(S)

C7 和 BST,以及 C7 和 LX

Q1(G)和DH

Q2(G) 和 DL

Q1(S) 和 LX

Q2(S) 和 PGND

请记住,1cm走线的寄生电感约为10nH。

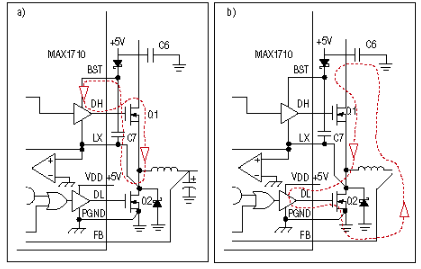

仔细观察 C6,您可以看到它提供 Q1 和 Q2,但方式不同。它用作Q1的滤波电容和Q2的储极电容。因为我们不能同时将C6放置在高端和低边驱动器附近,所以我们将其放置在尽可能靠近V日嘎和PGND(峰值电流流动的地方),以及C7附近(几乎平均电流)。请注意,PGND、DL 和 V日嘎别针是并排的,而不是偶然的!放置Q2和C6以最小化PGND、C6(-)和Q2(S)之间的接地走线长度。将此接地走线连接到 PGND 引脚附近的单个点的接地层。为避免共阻抗耦合,LX应连接到Q1,PGND/C6(-)应连接到Q2的源极。图3突出显示了关断期间的电流路径。

图2.虚线表示栅极驱动电路中Q1 (a) 和 Q2 (b) 的大电流。

图3.虚线表示Q1 (a) 和 Q2 (b) 栅极放电(关断)路径中的大电流。

应尽可能限制“通过”的数量。事实上,当di/dt很高时,过孔添加的几十个纳米亨是令人尴尬的。因此,您应该将所有电源组件放在组件层上,甚至是 SMD 组件。如果您别无选择,请将多个过孔并联。

我们必须记住,控制器对于手头的应用程序来说通常过大。例如,通常的做法是使用10A控制器来产生3A输出。由于我们通常出于成本原因选择最小尺寸的MOSFET,因此片内驱动器仍然尺寸过大,因此能够实现比所需更多的栅极驱动。

由于前面的讨论试图避免减慢MOS栅极驱动速度,因此将一个小电阻(10Ω至100Ω)与栅极驱动串联似乎自相矛盾。然而,过大和/或快速驱动波形会产生更多的开关噪声和RF干扰。在另一个极端,慢波形会在MOSFET和二极管(如果有的话)中产生更多的开关损耗。一个好的折衷方案是通过尽可能减慢波形斜率来降低EMI,同时保持可接受的效率水平。(图4b栅极驱动中的元件允许您分别调整上升和下降时间。幸运的是,大型驱动程序允许最后一点优化。

路由功率级

图4显示了许多电源转换器共有的两个大电流环路。为了响应开关引起的扰动,这些环路支持高di/dt,并且(在某些节点上)还支持高dv/dt。识别这些循环有助于减少其影响。请注意,di/dt 在转换器内(在开关节点处)很大,但在转换器外部很小。实际上,输入电容器之前和输出电容器之后的电流达到很高的值,但它们几乎是连续的。当转换器设计良好时,它们的交流分量为低电平。

图4.这些简单的原理图说明了升压(a)和降压(b)开关转换器的基本工作原理。

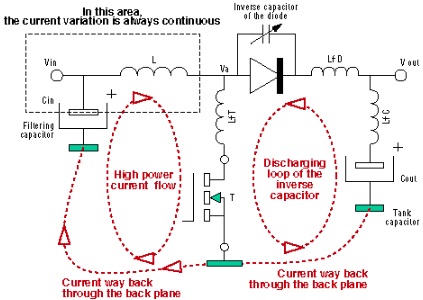

首先,尽量减少寄生电感。我们将考虑升压转换器,但推理可以转换为降压型。图5显示了导致最多问题的寄生电感类型。

图5.当主开关晶体管(T)关闭时,二极管电容放电如图所示。

在不描述开关周期的 10 个相位的情况下,我们可以考虑当电感电流被 MOSFET 短路时,MOSFET 关断。二极管的反向电容通过环路二极快地充电,二极管阳极处的节点电压Va(通常在Vout - Vd)接近0V。串行电感器 (LfT + LfD + LfC) 增加了放电时间,从而增加了 MOSFET 中的开关损耗。这些类型的电感也会产生噪声。

峰值电流受晶体管的限制,晶体管作为电流源工作(Vds 仍等于几伏)。对于 2A MOSFET,该电流源可能为 10A!电流电平在很短的时间内很大(几个10ns)。请记住,改变通过电感器的电流会产生与电流变化成比例的电压:

v = L × [di(t)/dt]

这个过渡阶段是一个很好的尖峰发生器!我们再次通过最小化走线长度并在MOSFET、二极管和Cout周围使用短而宽的走线来最小化寄生电感。现在,您可以看到如何通过控制栅极驱动波形中的斜率来降低噪声。

为了限制阻性压降和过孔数量,功率级SMD元件应放置在电路板的元件侧,电源走线在其元件层上布线。如果可能,电源接地也应在同一层布线。这种布置还有另一个好处:接地层的扰动较小。要消除辐射场,请注意最小化功率电流环路的面积。

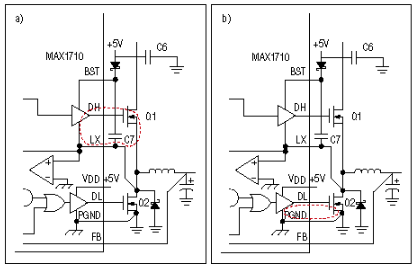

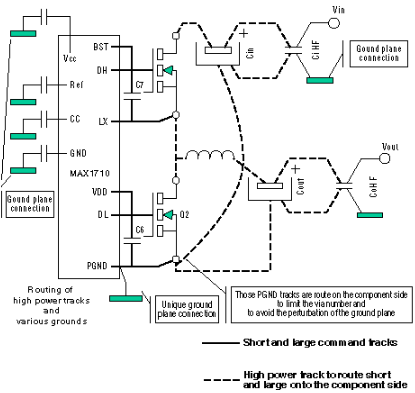

当需要在元件层以外的层上布线电源走线时,请从电感或滤波电容器中选择走线(即,Cout用于降压转换器,Cin用于升压转换器)。由于通过此类走线的电流几乎是连续的,因此不会产生噪声,只会产生电阻降。如果在元件层正下方的层上布线,寄生电感将更小。为避免公共阻抗耦合,应将PGND、电源电路接地和一般接地层分开(图6)。

图6.这些细节说明了控制器电路中PGND与栅极控制走线的路由。

电容器和其他组件

密切注意DC-DC转换器电路中电容端子的走线布线非常重要。大值低ESR电容器价格昂贵,不良布线会抵消其性能。另一方面,良好的布线可以将输出噪声从150mV降低到50mV!

纹波与电感值、电容ESR、开关频率等直接相关,但HF噪声(尖峰)取决于寄生元件和开关动作。我们可以预测从1MHz到10MHz的尖峰频率,具体取决于开关频率。

在不良布线中(图7a),与走线长度相关的寄生电感会引起麻烦:L1会导致噪声增加,L2限制了HF电容CoHF的衰减。解决方法(图7b)是将输入走线引入电容焊盘的一侧,输出走线在焊盘的另一侧。

图7.电容走线布线不当会引入不需要的寄生电感。

现在,在放置和布线了最笨重的部件之后,我们将注意力转向电感器。故意但不需要的耦合(图 8a)允许电源环路中的电流污染控制器电源 (Vcc)。通过切换Lp1产生的高di/dt会导致Vcc过冲,很容易达到几百毫伏。用

v(t) = L × [di(t)/dt]

L = 10nH, ΔI = 1A, Δt = 50ns, ΔV = 0.2V!

如前所述,第一个预防措施是分离电源走线并小心使用PGND。第二种预防措施是避免将走线连接到电源环路(见图8b)。分配输入电压的走线应在输入电容和控制器的Vcc连接之前连接。输出电压在连接到HF输出电容器后分配。

图8.(b)所示的连接可防止不需要的共阻抗耦合(a)。

最后,一些杂项建议:PGND走线的不良布线会导致共阻抗耦合(PGND端子的一个原因是避免污染控制器的内部接地节点)。将高阻抗走线(尤其是调节输出电压的输出电阻分压器)从支持高dV/dt的节点移开。这种耦合引起的电流会使控制器振荡。

审核编辑:郭婷

-

快速输入转换速率应用中DC-DC转换器的设计注意事项2024-10-08 477

-

DC-DC降压转换器PCB布局的技巧2023-06-19 3399

-

接地—升压型DC/DC转换器的PCB布局2022-11-09 1467

-

数控非隔离式DC/DC降压转换器参考设计2022-09-07 895

-

DC-DC升压转换器的资料分享2022-07-26 2944

-

非隔离式DC-DC降压转换器如何实现高降压比2022-04-02 7776

-

DC-DC转换器的相关资料分享2021-12-28 2785

-

非隔离DC-DC转换器的功能特点2021-09-29 3620

-

DC-DC电源有哪些注意事项?2021-02-23 2919

-

正激式和反激式DC-DC转换器介绍2020-12-09 4479

-

DC-DC降压转换器电路布局与设计和实践2019-07-11 13690

-

AC/DC非隔离型降压转换器的设计案例概要2018-11-27 3896

-

数字隔离器为何采用隔离式DC-DC转换器2017-10-24 14308

-

非隔离型DC-DC变换器的布线注意事项2009-05-13 2654

全部0条评论

快来发表一下你的评论吧 !