信号完整性的基本定义

描述

基本定义

一个高速数字信号从IC内部出发 → IC封装(例如键合线和管脚)→ PCB走线 → 到达另一个IC或者连接器/电缆等的过程中,这些物理材料对信号质量和电源质量的影响,称为信号完整性。

在信号波形上,体现为高速信号的电流或者电压的变化速度,即:

dI/dt 和dV/dt。

这些参数变化速度越快,信号完整性问题越严重。

主要带来四类问题:

信号失真

信号间串扰

影响电源分配网络(PDS),例如轨道塌陷、地弹等。

电磁干扰,主要是对外辐射。

信号频率和上升时间的关系

在常见的高速数字信号中,我们有个经验值是:某信号的上升时间是它周期的10%。例如

10MHz信号的上升时间是10ns

100MHz信号的上升时间是1ns

1GHz信号的上升时间是100ps

低频信号也可能有信号完整性问题

通常大多数人按照信号频率来辨别某信号是否属于高速信号,是否需要考虑信号完整性问题,例如以100MHz为界限。100MHz以下的信号不考虑信号完整性问题。

但是随着芯片技术的提升,可以生产更小尺寸的晶体管门沟道。当门的沟道长度越短,空穴和电子需要移动的距离也越短。这意味着门可以在更短时间切换状态,在波形上表现为上升时间的提升。这将使信号完整性问题更明显。

而芯片厂商为了成本考虑,在生产中尽量使所有的硅晶圆标准化,这样随着芯片尺寸的降低,每个硅晶圆上可以包含更多的芯片。因此有可能一颗低速芯片,它和高速芯片是在同一条产线出产的。这样这颗低速芯片在工作时,也会有较短的上升时间。

因此依靠信号频率来决定在设计中是否要考虑信号完整性问题已经不是很可靠的一个方法。建议在设计中,仔细查询原件spec。在PCBA生产后,进行相关电气参数测量。

仿真和模型

在PCB出图之前,通过设计软件进行信号完整性仿真,可以对信号波形有个初步的印象。仿真结果可以作为PCB设计修正的输入依据。

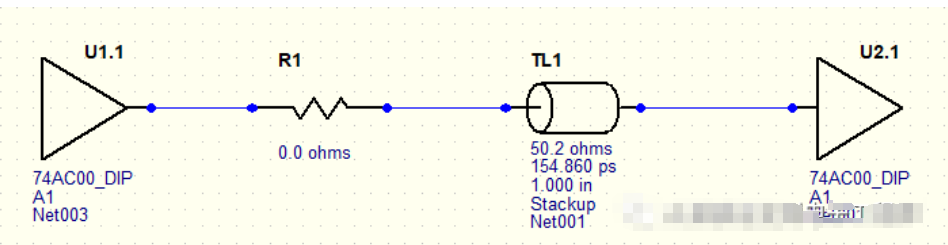

我接触过得仿真软件有Mentor的Hyperlynx,Cadence的Allegro,和安捷伦的ADS。最容易上手的是Hyperlynx。下图是使用Hyperlynx进行的一个基本电路仿真结果。

进行扫描仿真,将R1设定为从0欧姆到50欧姆,每增加10欧姆仿真一次。可以看到R1=50欧姆时(红色波形)效果最好。这是最简单的源端串联阻抗匹配。

<波形仿真结果>

<眼图仿真结果>

高速信号完整性仿真使用的模型称为IBIS模型(输入输出缓冲接口规范)。它是对芯片输入或输出端口的电压-电流曲线、电压-时间的定义。因为不牵扯到芯片内部的设计和工艺,因此和Spice模型(Simulation program with integrated circuit emphasis)相比,更容易获得。大的芯片厂商,例如TI、ST、镁光等官网都可以下载到对应的IBIS模型。在开始使用IBIS模型之前,要先检查模型的正确性。曾经遇到过某DSP厂商提供的IBIS模型中,把DDR3 CLK+和CLK-的定义搞反的情况。除了芯片,其他的无源器件(例如电阻、接插件、走线等),很多都没有专门的电路模型。需要用电阻、电容、电感等来组建无源器件模型。例如下图R1的等效电气模型由R2+C1+L1组成。

构成信号完整性的基本元件

分析信号完整性问题,由四类元件构成。

电阻

电容

电感

互连线

-

串扰和反射能让信号多不完整2017-08-02 3346

-

高速互连信号串扰的分析及优化2010-05-13 2787

-

信号完整性到底要怎么“完整”?2021-03-04 2185

-

何为信号完整性?信号完整性包含哪些2021-12-30 2886

-

信号完整性原理分析2009-11-04 1289

-

信号完整性基础指南2010-08-05 1224

-

信号完整性与电源完整性仿真分析2011-11-30 2120

-

3G网络与PCB信号完整性问题解析2017-12-04 1045

-

信号完整性的定义、干扰因素及解决方法详解2017-12-11 14586

-

PCB板信号完整性的定义及解决方案2019-06-21 6061

-

信号完整性分析2022-11-16 6673

-

信号完整性的定义是什么?何为高速差分讯号传输?2023-08-16 3416

-

EMC和信号完整性,针对的都是干扰,那么二者有什么区别?2024-03-26 2182

-

什么是信号完整性2024-05-28 3985

-

SI合集002|信号完整性测量应用简介,快速掌握关键点2026-01-26 457

全部0条评论

快来发表一下你的评论吧 !