PMOS开关电路分析

模拟技术

描述

概述

负载开关电路日常应用比较广泛,主要用来控制后级负载的电源开关。此功能可以直接用IC也可以用分立器件搭建,分立器件主要用PMOS加三极管实现。本文主要讨论分立器件的实现的细节。

电路分析

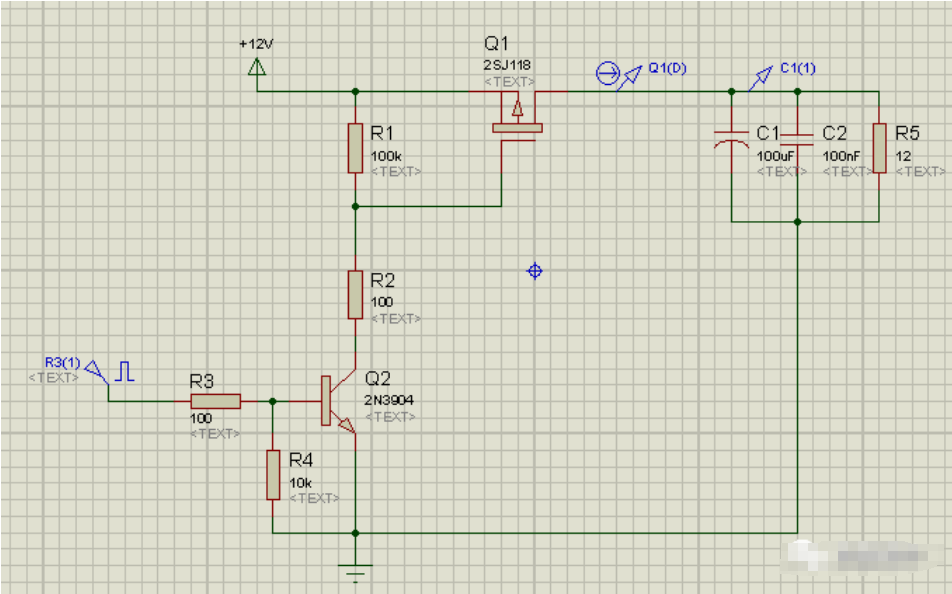

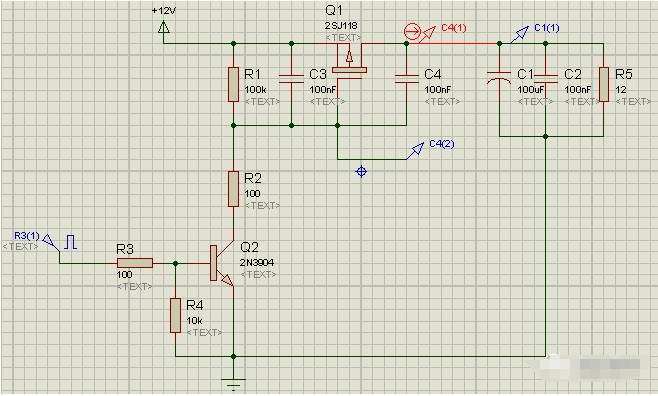

如下图所示R5模拟后级负载,Q1为开关,当R3端口的激励源为高电平时,Q2饱和导通,MOS管Q1的VGS

提出问题

当Q1导通上电瞬间电容两端电压不能突变会出现很高的冲击电流。此电流很可能会损坏MOS管或者触发前级电源的过流保护,所以此冲击电流并不是我们想要的。接下来给R3端口加单脉冲激励源,观察Q1(D)处的冲击电流。

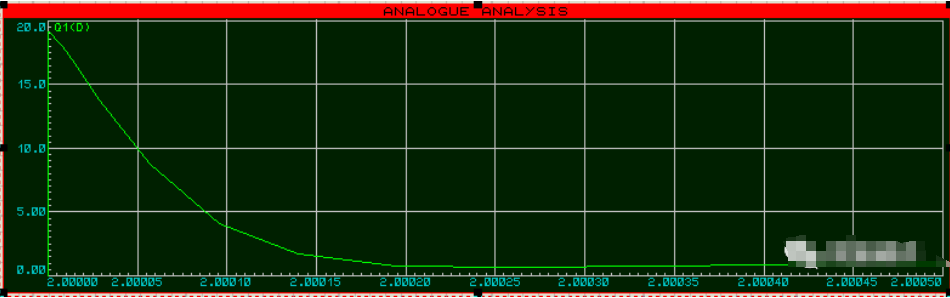

通过仿真观察电流记录数据图表发现Q1(D)处的电流峰值为约20A,稳态电流为1A。峰值较大给电路造成很大压力,接下来我们要想办法将此冲击电流降下来,保障电路的安全。

故障分析

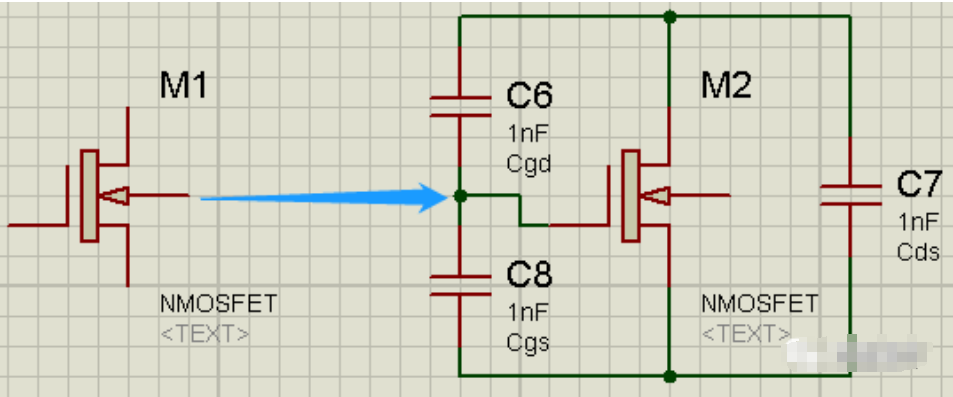

MOS的可以等效成下图右侧的电路模型,

输入电容Ciss=Cgs+Cgd,

输出电容Coss=Cgd+Cds,

反向传输电容Crss=Cgd,也叫米勒电容

MOS的启动波形

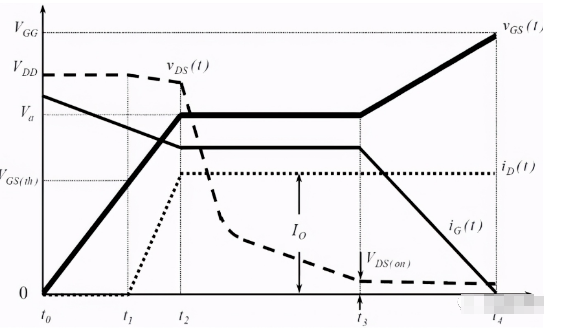

t0—t1阶段

这个过程中,驱动电流ig为Cgs充电,Vgs上升,Vds和Id保持不变。一直到t1时刻,Vgs上升到阈值开启电压Vg(th)在t1时刻以前,MOS处于截止区。

t1—t2阶段

t1时刻,MOS管开始导通,Id开始上升了。这个时间段内驱动电流仍然是为Cgs充电,Id逐渐上升,在上升的过程中Vds会稍微有一些下降,这是因为下降的di/dt在杂散电感上面形成一些压降。

t2—t3阶段

从t2时刻开始,进入米勒平台时期,米勒平台就是Vgs在一段时间几乎维持不动的一个平台。此时漏电流Id最大。且Vgs的驱动电流转移给Cgd充电,Vgs出现了米勒平台,Vgs电压维持不变,然后Vds就开始下降了。

t3~t4阶段

当米勒电容Cgd充满电时,Vgs电压继续上升,直至MOS管完全导通。

从上述周期看出MOS管开启过程主要受Cgs和Cgd共同影响。如果延长开启过程主要是延长t1—t2阶段和t2—t3阶段,在负载确定的情况下主要是增大Cgs和Cgd等效电容来实现。

仿真实践

在原有电路中加入C3和C4 100nF电容

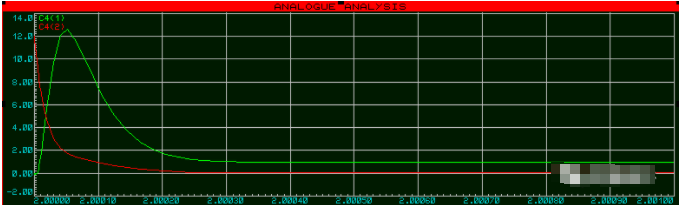

仿真得出启动时电流波形为,其中红线为Q1的Vgs波形绿线为C4(1)测到的启动电流波形

明显对比之前不加C3、C4电容时启动冲击电流波形峰值下降,开通时间变长,并且尖峰后移。

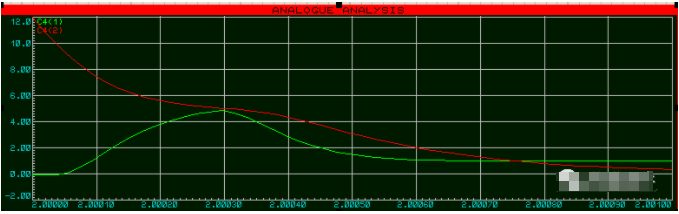

调整C3和C4的值为1000nf时,效果更加明显

实验结论

实验得出增加MOS的Cgs和Cgd可实现开通缓启动功能,保护MOS不受到冲击损坏。

-

pmos开关电路连接方式有哪些2024-10-06 7808

-

NMOS与PMOS经典电源开关电路的深入解析2024-04-10 13253

-

常见的PMOS开关电路问题分析2024-04-07 5343

-

如何设计一个nmos管和一个pmos管的开关电路2023-12-21 10680

-

电源开关电路图讲解:NMOS、PMOS2023-08-14 11843

-

PMOS在开关电路中的应用设计与分析2023-03-26 24850

-

NMOS开关电路分析2023-03-10 11925

-

pmos 电源开关电路_如何验证开关电源电路2021-11-10 1404

-

怎样去做一个PMOS的按键开关电路2021-10-28 3241

-

PMOS按键电源开关电路2021-10-21 1746

-

基于PMOS的高速开关电路求教2020-06-08 6581

-

关于NMOS/PMOS在开关电路中应用的问题2019-04-18 8375

-

开关电路拓扑的分析和推演2017-09-11 890

-

四种常用晶体管开关电路(2种NMOS,2种PMOS)2016-08-30 64888

全部0条评论

快来发表一下你的评论吧 !