介绍一种查找芯片设计中偶发错误的方法

描述

异构设计、定制和日益增加的复杂性带来了很多硬件错误。

将芯片分解为专门的处理器、存储器和架构对于持续改进性能和功率变得必不可少,但它也会导致硬件中异常且通常不可预测的错误,这些错误极难发现。

这些误差的来源可能包括任何事情,从特定序列中的定时错误到封装中芯片之间的键合间隙。随着不同芯片或小芯片中的电路以不同的速度老化,以及随着各种类型的压力将潜在缺陷变成真正的缺陷,它们会随着时间而改变。因此,计算有时可能会产生错误的结果——但并非每次都如此。如果互联网搜索结果错误或流媒体视频出现轻微故障,这不会引起注意,但当涉及金融交易、汽车安全或军用无人机制导系统时,它的重要性就完全不同了。

这些类型的问题并不是全新的。有关该主题的技术论文在 2000 年代初期开始出现,讨论了芯片中的意外行为和偶发故障。然而,他们现在已经达到了一个临界点,问题已经足够严重,数量也足够多,值得关注。但出于多种原因,如何处理它们并不总是很清楚。他们之中:

有更多的组件密集地封装在芯片上和封装中,其中一些具有更薄的金属层和电介质,以及更多的互连。这使得很难预测工艺变化、潜在和实际缺陷,甚至量子效应会在何处引起问题,或者以什么顺序引起问题。

先进节点芯片正被用于比过去利用率更高的系统中,特别是在数据中心和人工智能应用中。这会增加这些设备上的机械和电气应力,从而影响信号质量和时序。除此之外,其中一些系统被设计为更长的生命周期,需要定期的软件更新,这可能会导致一些硬件组件随着时间的推移表现不同。

设计变得更加异构和更加定制化,增加了特定设备独有的可能交互的数量。此外,这些设备越来越多地使用在不同工艺节点开发的组件,有时由不同的代工厂制造,并非所有这些组件都具有相同的特征。

所有这些都增加了复杂性,使得所有极端情况变得更加困难、耗时和昂贵。

Synopsys研究员 Rob Aitken 说:“我们现在观察到的这些问题是因为我们拥有了更大的芯片和更好的仪器,还是因为这是一种新的东西,存在疑问。” “无论哪种情况,这是可以在制造时识别的东西,还是识别它的行为会影响经济收益?我最近和 IBM 的某个人参加了一个座谈会,他说这就是大型机如此昂贵的原因。它们旨在寻找每一个可能的问题。”

悬而未决的问题是,这是否会成为对安全关键和任务关键硬件的要求。如果是这样,解决它的最佳方法是什么。如果一切都必须完美,那将对产量和成本产生影响。但是,如果可以通过在系统中设计弹性来解决其中的一些问题,它可能有助于控制成本。

完美与弹性

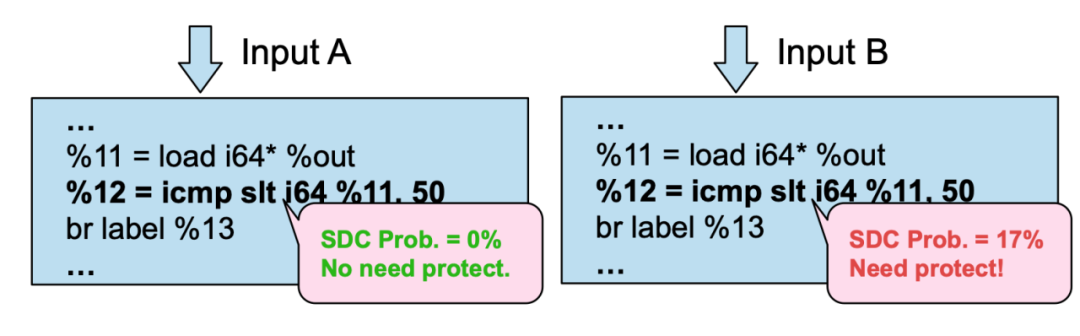

爱荷华大学、百度安全和阿贡国家实验室联手创建了 MinpSID(多输入硬化选择性指令复制),它识别“跨多个输入的难以捉摸的错误传播”。在一份新发布的技术论文中,研究人员声称已经找到了一种提高可靠性并识别导致这些错误的“孵化指令”的方法。

图 1:孵化说明示例。来源:阿贡国家实验室/爱荷华大学

这是这个谜题的一部分。但到目前为止,还没有单一的可重复解决方案,而且未来是否会出现也不明显。事实上,解决方案可能是特定于设计的,有时甚至是违反直觉的。

Movellus的电源架构师 Barry Pangrle 说:“我们看到一个案例,人们在构建电路时,在某些情况下,你可以对不同的计算组合进行统计分析,但有时会出现此错误。”“他们所做的是压低电压。他们知道它不会一直都符合时机,而且它会得出的结果基本上是误报。他们将其用作筛选器以找到好的结果,并采用较小的集合并在真正强大的系统上运行它。现在的问题是一切都变得越来越复杂。随着电路变老,它们往往会变慢。所以现在,从健康的角度来看,我们需要研究老化的技术,监控事物,有延迟循环和类似的东西,看看它是否随着时间的推移而漂移。”

防止这些偶发错误需要首先了解它们的来源。但随着定制芯片或小芯片的集合以及独特架构的加速推出,这是一项非常重要的工作,可能会推高总体开发成本。虽然其中一些问题可以事后用软件解决,但如果硬件本身是可编程的,它会更有效。这为设计增加了一定程度的弹性,以适应任何问题,而不会因修复软件问题而影响功率/性能。

Flex Logix的 CEO Geoff Tate 说:“第一件事就是检测出什么时候会出问题,然后再出问题。”“第二件事是为此做点什么。如果出现问题,你需要进行补偿——就像人脑一样。大脑中的神经元一直在死亡,但我们的通路可以再生。人们可能会对他们的大脑造成非常严重的损害,但大脑的其他部分可以随着时间的推移重新编程以弥补它。现有的芯片不能那样工作。唯一可以弥补它的是处理器或 FPGA,它可以通过编程来做不同事情的东西。”

弄清楚何时以及为什么会出现错误是值得花时间的,但在某些情况下,这可能意味着很多时间。Google 和 Meta 检测到的静默数据错误花了一年多的时间来追溯根本原因。并且通常在开发出整个芯片或封装或在现场使用时才会出现问题。

Imperas Software首席执行官 Simon Davidmann 表示:“构建这些东西并将其整合到设备中的所有物理机制都存在挑战。”“作为一个行业,你还面临着如何在运行时验证整个事物的挑战。我们刚刚开始与一些公司在 SoC 级别进行合作,然后它会进入系统级别。但这是一个涉及系统系统的漫长而缓慢的过程。”

任何可以预先做的事情来找出潜在的问题都是有益的,这可能涉及物理和虚拟因素。

“热分析发挥了作用,”是德科技副总裁兼总经理 Niels Faché 说。“如果电路板和 IC 中有热点,随着时间的推移,它会对设备的性能产生影响并导致其故障。我们看到越来越多的人重视热分析,并且我们在其中添加了热建模,因为这会改变电气性能。机械分析可能也是如此。你可能会在电路板上发生变形,从而改变电气参数。”

热量对芯片或系统的行为方式构成严峻挑战。“你必须密切关注热梯度,”Ansys 半导体部门产品营销总监 Marc Swinnen说。“这给出了不同的扩张。即使堆叠的顶部和底部之间只有 25° 的差异,考虑到这些设备的极薄,我们谈论的是每厘米 10,000° 或该范围内的某个值。对于这么短的距离,这是一个巨大的温度梯度,这会导致相当大的压力。”

制造和封装缺陷

并非所有错误都是由于设计造成的。它们可能由设计到制造流程中任何一点的任何因素组合引起。事实上,它们可能表现为被认为是良性的潜在缺陷,例如纳米级缺陷,或者它可能是在检查和测试中被忽视的缺陷。并且其中一些缺陷可能要等到设备开始老化后才会显现出来。

Cadence数字与签核集团产品管理副总裁 Kam Kittrell 表示:“尤其是现在的 5nm,老化正在影响时序,所以你已经有了这些如何老化的模型”.“但是你怎么知道它在外面放了五年之前会如何老化呢?这意味着你必须仔细检查这样的事情。此外,如果你发现一个特殊的案例失败了——可能是软失败,比如偶尔翻转一下——这不是制造缺陷,但你可以在制造测试中做一些事情。你可以返回并使用已知的坏芯片重新进行制造测试,然后将测试分散到每个单元以查看链中是否存在薄弱环节。这有很多好处。云计算与汽车一起推动了这一点,因为现在汽车领域的复杂性已经超出了图表。你的仪表盘上到处都有超级计算机在运行,当他们的汽车不能工作时,人们会很不安。”

更糟糕的是,随着芯片或小芯片被引入并堆叠在先进的封装中并被大量使用,或者由于这些设备中的任何一个以它们最初设计目的以外的方式使用,潜在的缺陷可能会变成真正的缺陷。并非所有这些都可以修复,但可以在它们成为问题之前识别出来。

“潜在缺陷更多地与热机械方面有关,”proteanTecs业务发展高级总监 Nir Sever 说. “微凸块可能有裂缝或空隙。车道可以有桥梁短裤。TSV 可能有裂纹、部分填充或侧壁分层。由于模具不完美,会发生许多物理缺陷。但即使它们是完美的,当你开始组装过程时,也有很多潜在的故障点。在典型的 HBM 中,大约有 10,000 条不同的通道。如果其中一个有缺陷,除非修复,否则该 SiP 将无法工作。所以你已经放下了所有这些微凸块,你必须将它们组装起来,使它们全部接触。如果其中只有一个有缺陷,芯片变形,或者材料移动了一点并且没有完全对齐,你将获得影响信号质量的电阻行为。”

挑战在于找出可能发生的地点和时间,以及如何准确识别问题。

“所以首先你必须能够测试,因为产量不是 100%,”Sever 说。“很有可能至少有一条车道在组装后会出现缺陷。其次,因为它正在老化,你需要在产品的整个生命周期中,在现场和任务模式下持续监控接口。如果它从一开始就处于边缘状态,因为存在未产生测试失败的潜在缺陷,随着时间的推移它会退化。

最终,时序余量或眼图将开始闭合,你将在总线上遇到错误。这是一场灾难,因为与在具有纠错机制的 SERDES 中不同,在典型的 D2D 中你没有。协议中不一定内置纠错功能。你假设误码率几乎为零,就像常规 I/O 一样。这将导致数据错误,表现为静默数据损坏,没有人真正知道它们来自哪里。但事实是,数据开始在芯片内部某处损坏,你必须有办法从内部进行测量,可视化数据,理解它,然后能够追踪根本原因并修复它。”

提高弹性

这就是弹性发挥作用的地方,而内存行业在这方面一直遥遥领先。例如,众所周知,NAND 闪存会随着时间的推移而退化。在它不再工作之前,你只能向闪存写入这么多内容。

Flex Logix 的 Tate 说:“有一些磨损均衡算法可以在其中多放 30% 的位,这样它们就可以在 10 年以上可靠地工作。”“但他们必须在它们变坏之前找到这些位,然后换上仍然好的位。对于弹性逻辑设计,你将需要嵌入式 FPGA 之类的东西,其中你有一些可用的未编程计算能力,可以承担系统其余部分出现故障的任何内容。所有芯片都有错误。有一些错误会杀死芯片,因此它无法正常工作。有bug导致性能不好,所以无法发货。还有各种你可以解决的错误。在我们的芯片中,我们有一个无法解决的错误,除了我们在处理器总线上有 4,000 个嵌入式 FPGA 查找表之外。我们能够在该查找表上编写一些 RTL 代码,以弥补芯片其余部分中的错误。然后我们可以运送芯片,而客户并不知道我们以这种方式修补了它。”

大多数弹性解决方案都依赖于某种程度的冗余。这可以包括可编程性,这减少了对全新电路的需求,它可以包括软件,它效率低下但重新编程容易且相对便宜。在所有情况下,都会有一些开销。关键是在选择在功率、性能和面积/成本方面进行权衡时,将其保持在最低水平。因此,如果面积/成本至关重要,则添加在线监控可以代替添加的电路。如果功率至关重要,那么冗余可能会以可重新编程逻辑的形式出现。如果性能是最关键的因素,则可以添加额外的电路并根据出现问题的位置动态打开和关闭。

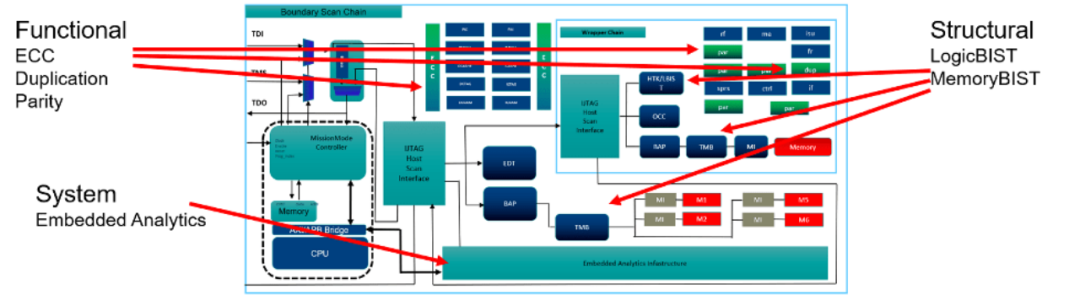

“这最终是一个经济学问题,”Siemens Digital Industries Software的 Tessent Embedded Analytics 产品经理 Richard Oxland 说. “无声数据错误给我们造成的损失是否超过了拥有冗余计算的硅片成本?这是一个大多数半导体公司无法回答的问题,因为这是一个系统级问题。它需要更好地了解静默数据错误的经济影响。如果你想想 Meta、谷歌或 AWS,那很快就会变成非常高度专有的信息。如果这些要求变得有意义,这些人将开始降低这些要求。我们可能并不总是知道这一点,因为他们正在设计自己的芯片。所以在你的系统中,你可以在那里有一些冗余。或者在 NoC 中,你可以做一些聪明的事情,比如路由来避免问题。”

图 2:冗余和自测试。来源:西门子 EDA

不过,这增加了另一层复杂性,因为复杂设计中不只有一个 NoC。可以有很多,需要在整个系统的上下文中查看它们。“然后你必须开始处理 NoC 之间的时序,因为它们没有完全同步,”Arteris IP解决方案和业务开发副总裁 Frank Schirrmeister 说。“你必须处理外设连接的时序,以及各种时钟域交叉。”

Schirrmeister 说,在这幅图景中增加弹性是一项挑战,但使用分而治之的策略比试图立即解决整个问题更容易使各个部分具有弹性。“你不想同时处理一堆信号。因此,如果你正在查看安全说明,例如,你可以添加检查器以确保其正常运行。”

弹性在汽车领域引起了广泛关注,该领域的芯片被用于对安全至关重要的应用,并且法规要求进行某种形式的故障转移。“汽车行业一直对其半导体的可靠性充满热情,”Oxland 说。“一些大型供应商在这个领域活跃了一段时间,比如 NXP 等——非常擅长这类事情。该应用程序的复杂性可能略低,因为我们谈论的是 ECU。但总的来说,它们的部署数量巨大——尽管它们在运行方式方面更具确定性。由于大规模运行非常高度并行化的工作负载的复杂性,我们现在看到了静默数据错误的问题,所以它更像是一个新问题。

极端的权衡

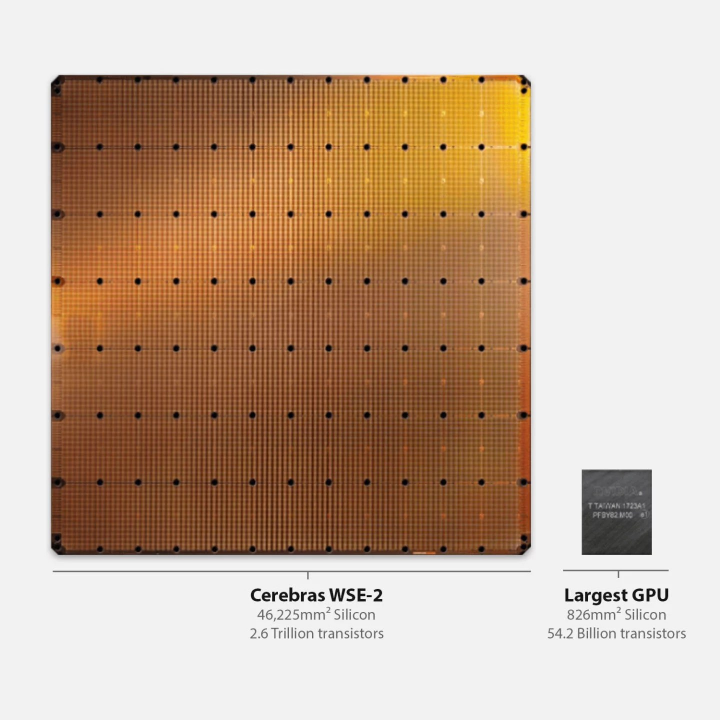

当 Cerebras 开发其晶圆级芯片时,它认识到没有任何东西可以 100% 地产出,并且芯片的某些部分——从整个晶圆上切下的 800 平方毫米的正方形——会以不同于其他部分的方式老化,并且潜在的缺陷会变成真正的缺陷。

“从历史上看,DRAM 实现非常高产量的方式是拥有冗余的位单元行和列,”Cerebras 的首席执行官安德鲁费尔德曼说。“我们有 850,000 个相同的可编程元件,这是一个核心加内存加一个小路由器。它用电线连接到下一个。每个可编程元素都与其四个邻居中的每一个相关联,并通过冗余链接与其邻居的邻居相关联,从而使其能够与其邻居对话。我们所做的是构建一个测试芯片,并与台积电合作处理他们的良率数据。如果代工厂在控制范围内工作,你应该拥有的是随机分布的缺陷。这样一来,冗余应该可以让你找出缺陷。所以当我们说我们有 850,000 个核心时,我们实际上有 870,000 个左右的核心,因为我们将保留大约 1.5%。”

图 3:晶圆级芯片内置约 1.5% 的冗余度。

费尔德曼说,其他关键部分是在映射之前烧入,并将芯片暴露在超出规范的温度下。“从那里开始,自检会检查每个核心以及每个核心之间的每条电线的行为,”他说。“如果失败,它会激活绕过路由协议并重新进行自检。所以有一个硬件自检在启动时运行,然后定期运行。”

虽然这对大多数应用程序来说仍然不切实际,但它确实证明了一点。通过足够的努力和创新,这些问题中的大部分都可以得到解决。挑战在于确定应用程序可接受的权衡,然后真正理解这些权衡实际上需要什么。在当今的硬件和系统设计中,并非所有这些都是显而易见的。

结论

所有这些都指向一个更广泛的问题,即管理由于更密集的电路、更多的定制和功能、新材料和不同的使用模式而导致的复杂性增加的能力。结果,未知数呈爆炸式增长。并非所有这些都可以被完全理解或调试,但对于许多应用程序来说,这是可以接受的。但对于任务关键型和安全关键型应用程序,故障规划至关重要。

不可能在紧迫的市场窗口内抓住一切,但只要有足够的时间和努力,似乎可以制造出能够应对大多数问题的芯片。毫无疑问,需要在更多芯片中构建弹性。解决方案这是一个如何以可接受的价位获得足够弹性的问题。芯片行业才刚刚开始认真看待这个问题。

审核编辑:刘清

-

vlookup常见的12种错误2023-12-01 5717

-

linux查找ip地址的三种方法2023-08-02 1055

-

一种AUTOSAR软件架构中RTE的实现方法2022-07-13 908

-

使用静态分析查找并发错误2022-06-19 1866

-

介绍一种嵌入式系统仿真方法2021-11-08 1620

-

介绍一种基于分级的RFID隐私保护方法2021-05-26 2099

-

一种利用调试软件Valgrind进行嵌入式应用程序错误查找的技术2021-04-23 1543

-

干货 | 电机控制器出现的一种偶发故障排查与分析2021-01-27 2239

-

嵌入式C语言程序软件中的缺陷怎么查找?2019-11-04 1898

-

一种使用无源RFID替代EEPROM代码芯片来存储血糖试纸的方法介绍2019-07-26 3111

-

一种错误签名混合筛选算法2017-12-07 594

-

抗突发错误的短码长随机LDPC码设计2017-12-01 1017

-

一种查找最新数据地址的方法2010-05-19 475

-

一种系统芯片的功能测试方法2009-12-21 1123

全部0条评论

快来发表一下你的评论吧 !