基于DDR4讨论DRAM的颗粒容量规格

存储技术

描述

DDR4 协议标准中规定了几种 DRAM 颗粒的容量规格,这些规格包含哪些方面?本文将讨论这个话题。

DRAM 容量规格

DDR4 (下文可能混合使用 DDR4/DDR/DRAM, 皆为同义)颗粒在容量上有四种规格,分别为 2Gb、4Gb、8Gb 以及 16Gb。

DRAM 颗粒的容量 = 地址数量 x 位宽

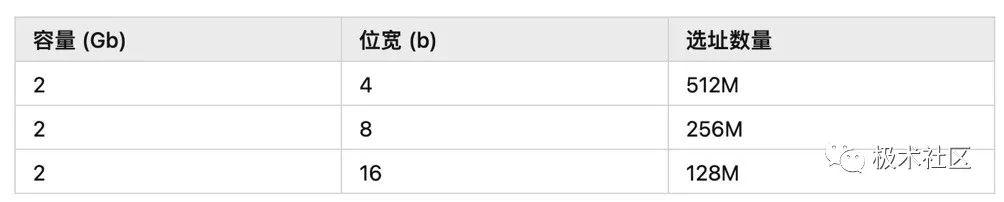

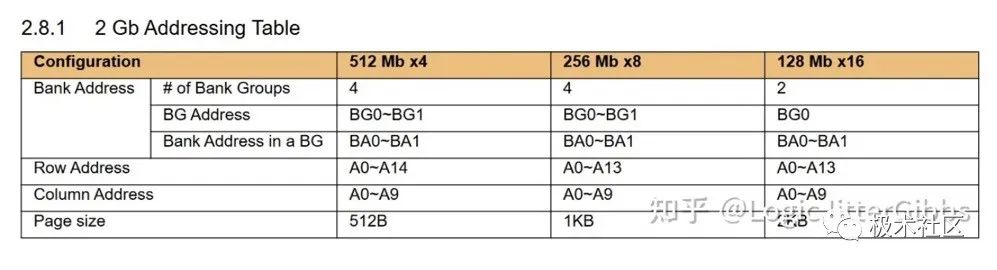

每种颗粒容量规格,提供了 3 种地址数量和位宽的组合,以 2Gb 颗粒为例:

提供多种组合目的是为了提供灵活的配置方案。因为一个嵌入式系统的 DRAM 位宽一般为 32 或者 64 比特(在 PC 上有更大的位宽),需要拼接多片 DDR4 颗粒才能提供这么多比特,那么使用不同位宽的 DDR 颗粒就会有不同拼接方案。 以 32 比特位宽,嵌入式系统为例,使用不同位宽的 2Gb 颗粒,有以下几种组合:

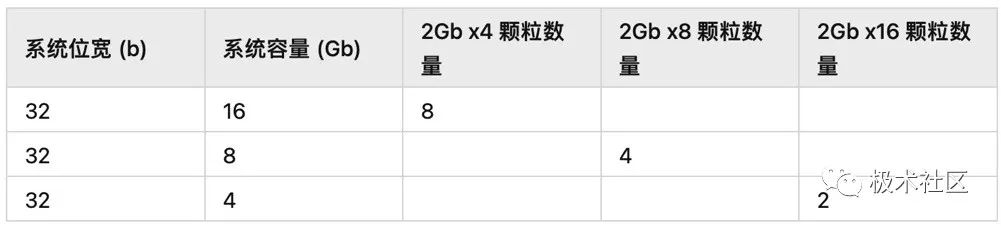

一般系统位宽的需求是固定的,而颗粒容量和位宽是一对可调整的参数,提供不同的系统容量,仍以 32 比特系统 DRAM 位宽为例:

上表中的数量指的是系统的 DDR 颗粒总数量。有点与直观感觉违背的事实是,采用的位宽更大的颗粒,系统的总容量更低。 这是因为相同容量的颗粒,位宽越大,地址数量也就越少,所以系统位宽固定时,决定系统容量的是颗粒的地址数量: 系统容量 = 地址数量 x 系统位宽

接下来我们来看颗粒的地址数量以及其寻址方式。我们知道 DDR4 的寻址由 COL _- ROW_* - BANK- BANKGROUP 组成(单个 RANK 时)。

*COL, column, 指 DRAM 内部存储阵列中的列 **ROW, row , 指 DRAM 内部存储阵列中的行

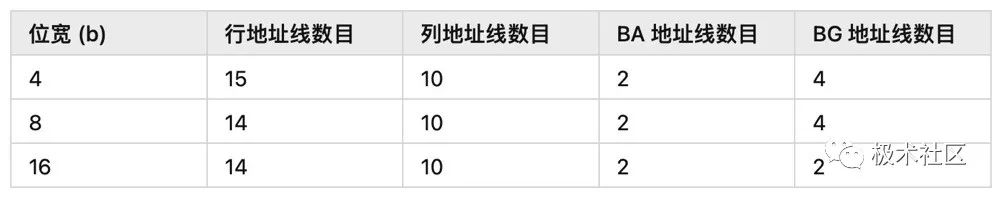

颗粒的列数量是固定的 1024 列,而行、Bank(BA)、Bank Group (BG) 数量在不同位宽时则是不同的。

地址所属的行、列、BA 以及 BG 的寻址是通过对应的地址线寻址得到,所以不同位宽的颗粒地址线的数目也不同。

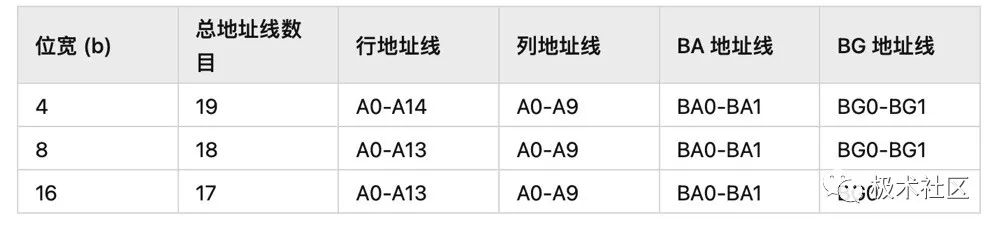

由于行列地址线是分时复用的,以 x4 位宽为例,行列共享 A0-A14 地址线中的 A0-A9,所以 x4 位宽总地址数量为 15 (A) + 2 (BA) + 2 (BG) = 19。 这里我们看到使用小位宽颗粒虽然能够拼接更多颗粒,提供更大的系统容量,但是所需要的地址线较 x8 和 x16 的颗粒也更多。这是更大系统容量的代价,或者说是系统容量与地址线数量的折中考量( trade-off)。

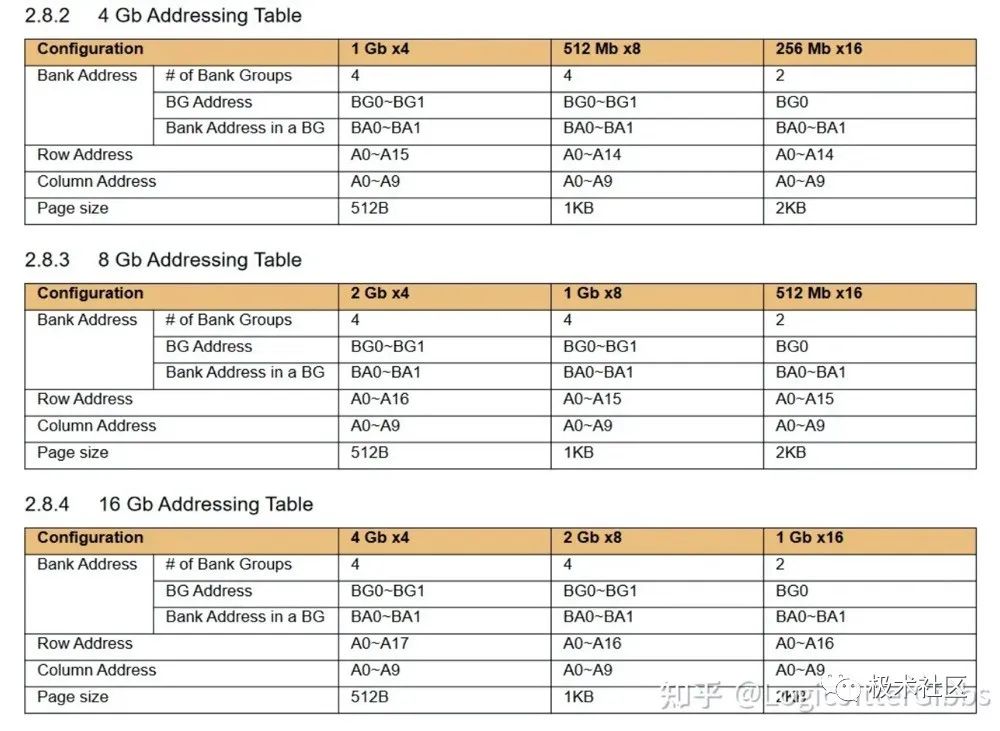

下面几张图都摘自 DDR4 协议 2.8 节,列出了 DDR4 支持的四种容量颗粒的属性,从中我们可以发现几点:

地址线最多的是 16Gb 容量的 x4 颗粒,使用 A0-A17 地址线。需要注意的是所有 PHY 都会有 A0-A16 (因为 RAS\_n 复用为 A16),但有些 PHY 可能不支持 A17。

所有颗粒每个 Bank Group 都有 4 个 Bank

但是,x16 颗粒只支持 2 个 Bank Group,而其他颗粒支持 4 个

x4 颗粒的地址线最多,而 x8 和 x16 颗粒的地址线数目相同,比 x4 少 1。x8 和 x16 的选址数目差异体现在 x16 的 Bank Group 少一半

另外值得一提的是页大小(Page size),等于一行中的数据数量,直观来说页大小与位宽直接相关。 Page size = 位宽 x 列数量 = 位宽 x 1K 对于 x4 颗粒,页大小 = 4b x 1k = 4kb = 512B 顺序读取同页数据时,每次读取之间是基本无需等待的。而非同页数据之间,则需要按照协议要求,在两次读取之间增加延迟。举例而言, x16 颗粒上可以无延迟顺序读取 2KB 数据,但是如果是一个 x8 颗粒,则需要在读取完 1KB 数据后,关闭当前行并且打开下一行,才能读取后 1KB 数据,需要增加的延迟大约在几十个时钟周期量级。 最后,我们在前文中使用 4b x 512M 来描述一个 x4 颗粒,这是从颗粒位宽 x 地址数量的角度出发。协议中的称呼为 512Mb x 4,个人觉得两种称呼都可使用吧,笔者自己平时也没特别在意。 DDP 颗粒

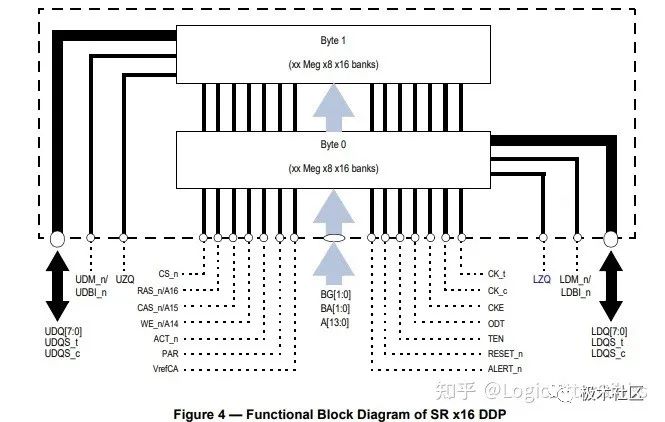

最后讨论一种容量比较特别的颗粒,也是最近工作中遇到的。事情是这样的,客户提问说 SoC 能不能支持一种 4GB 的 DDR4 颗粒。阅读完本文的读者知道,DDR4 最大只有 16Gb(2GB)的颗粒,哪来的单颗 4GB 颗粒? 看了客户发来的颗粒 spec (是三星的颗粒)才知道,客户想使用的是一种特殊封装的颗粒,DDP(Dual Die Package),在协议的 2.9 节有简略的介绍。 DDP 颗粒顾名思义就是将两个 x8 Die 封装在一起,这样最大能够提供单颗 32Gb (2 x8 16Gb)的容量。 两个 Die 的连接方式如下图所示,它们的 CA 在封装内被堆叠(或者焊接)到一起,往封装外引出各自的 DQ 和 DQS 引脚。

协议中提到,除了具体产品手册的特殊注明外,DDP 颗粒的特性以及时序和普通的 x8 颗粒相同。 DDP 的好处是可以节省 PCB 的空间和布局布线时的难度,另外,因为两个 Die 之间的 CA 信号延迟会非常小,笔者觉得或许可以跳过两个 Die 之间的 write leveling 训练。 DDP 的劣势就显然易见,或许因为额外的封装成本,价格会相对更高,自然用户就会比较少,用户越少,价格也就越昂贵,供货越得不到保证,半导体行业典型的恶性循环就出现了。基于这些考虑,我们的客户后来也放弃了这个想法。:)

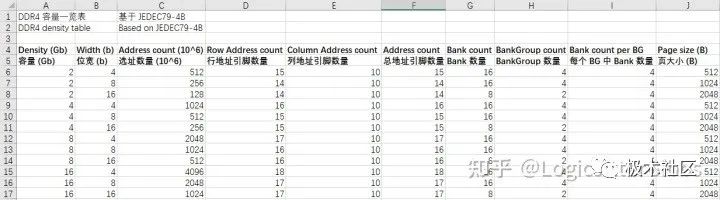

DRAM 容量与其配置选择文档

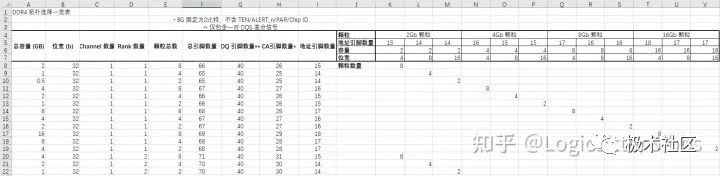

笔者在工作中整理了一份 DRAM 容量和其容量配置选择的文档,可以从以下链接获取。 (临时放在这个 PCIe 的仓库下面) 内容包括 DDR4 颗粒容量一览表以及不同配置方案一览表,大致的内容贴在下图中。

编辑:黄飞

-

DDR4涨价20%,DDR5上调5%!2025-05-13 7804

-

DDR内存格式发展历程(DDR~DDR4)2011-02-27 3529

-

DDR4的工作原理以及寻址方式2021-11-11 2513

-

DDR4,什么是DDR42010-03-24 4255

-

三星历史首款DDR4 DRAM规格内存条的开发完成2011-01-05 1732

-

怎样降低DDR4系统功耗2017-10-13 2067

-

紫光DDR4内存挂羊头卖狗 并没有使用国产颗粒还是韩国的2018-03-05 3695

-

DDR4封装规格2018-06-26 3631

-

JEDEC的DDR4技术标准的公布2018-09-30 3107

-

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?2018-10-14 28356

-

SK海力士研发完成基于1Ynm工艺的DDR4 DRAM芯片2018-11-13 8565

-

DDR4原理及硬件设计2021-11-06 3439

-

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板2022-10-10 9491

-

ddr4 3200和3600差别大吗 ddr4 3200和3600可以混用吗2023-08-22 64816

-

DDR4价格疯涨!现货市场狂飙!2025-06-19 11053

全部0条评论

快来发表一下你的评论吧 !