跨时钟域CDC之全面解析

电子说

描述

跨时钟域(Clock Domain Crossing,CDC)作为数字芯片设计中的经典问题,也历来是各面试官常问的问题。今天我们来分析一下跨时钟域的相关问题,希望对你有所启发。

一、什么是时钟域?

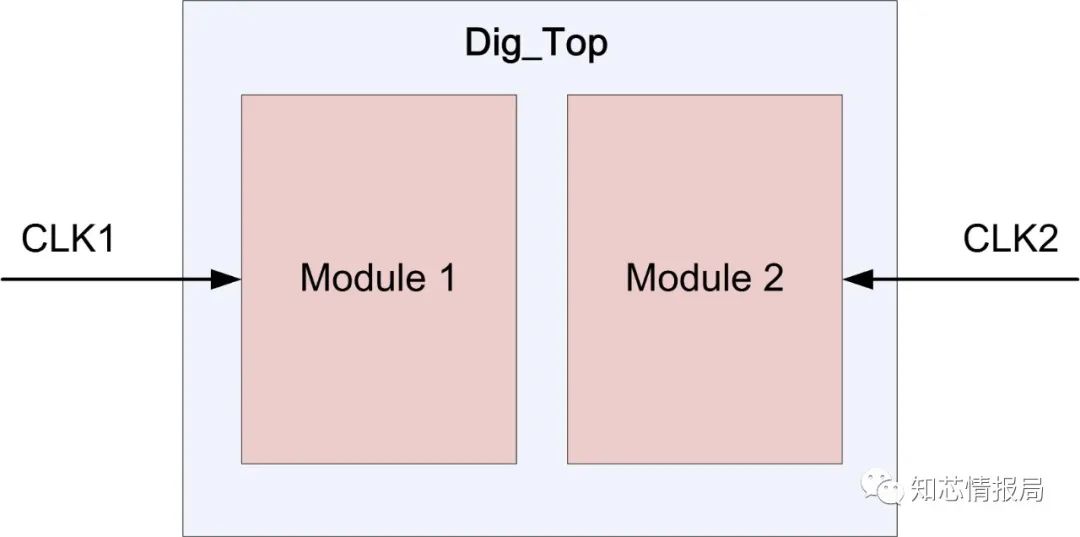

在一些较为简单的数字电路中,只有一个时钟,即所有的触发器都使用同一个时钟,那么我们说这个电路中只有一个时钟域。对于功能较为复杂的芯片,如下图所示,电路中往往存在多个时钟,不同的模块使用不同的时钟,那么我们说这个设计中有多个时钟域。当信号在不同时钟域之间传输时,就被称为跨时钟域。

二、什么是亚稳态?

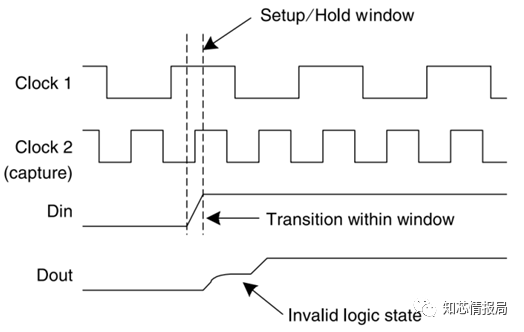

当数字信号跨时钟域传输时,就会产生亚稳态问题。亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。每一个触发器都有其规定的建立(setup)和保持(hold)时间参数, 在这个时间窗口内, 输入信号在时钟的上升沿是不允许发生改变的。如果触发器的数据输入端口上数据在这个时间窗口内发生变化(或者数据更新),那么就会产生时序违规,触发器的输出将徘徊在不可预知的电平状态,即亚稳态。

如下图所示,在CLK2的上升沿到来的时候,触发器Din的数据在发生变化,那么Dout的数据将会徘徊在一个中间电平状态(这个中间电平可能正确值,也可能是错误值)。也就是说,电路处于中间态的时间变长,使得电路“反应”迟钝,这就是“亚稳态”。亚稳态信号的稳定时间通常比一个时钟周期要短的多。

一般情况下不会超过一个或者两个周期,取决于触发器的性能。如果亚稳态超过一个或者两个周期,那么就会被下一个触发器采样到,这样就会造成亚稳态的传播。但是需要强调的是,如果产生亚稳态,亚稳态恢复稳定后的电平不一定是正确的电平,如果稳定后的电平是错误的,那么就很有可能引起后面的逻辑的错误。

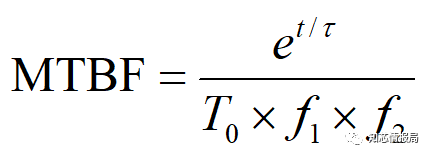

再深入一点,触发器进入亚稳态的时间可以用参数 MTBF(mean time between failures)来描述, MTBF即触发器采样失败的时间间隔,其公式描述如下:

其中:

t:在不引起synchronizer failure的前提下,亚稳态持续的最长时间

τ和T0:触发器工艺相关的参数

F1:输入的异步信号频率

F2:起同步作用的的触发器时钟频率

通常,MTBF越大说明系统采样失败的可能越小。从上面公式可以很明显的看出,对于高速数字电路,MTBF发生的概率更大。此外,对于不同的系统和应用场景,MTBF的要求也不同。比如对于一些消费级的产品,比如手机,智能手表等,MTBF的要求要远远低于军工级和航天级别的产品,比如卫星,导弹等。

三、怎么降低亚稳态?

首先,亚稳态是不可避免的,是器件的固有属性。通过适当的方法,可以将亚稳态带来的消极影响将至最低。一般来讲,主要有下面几种方案:

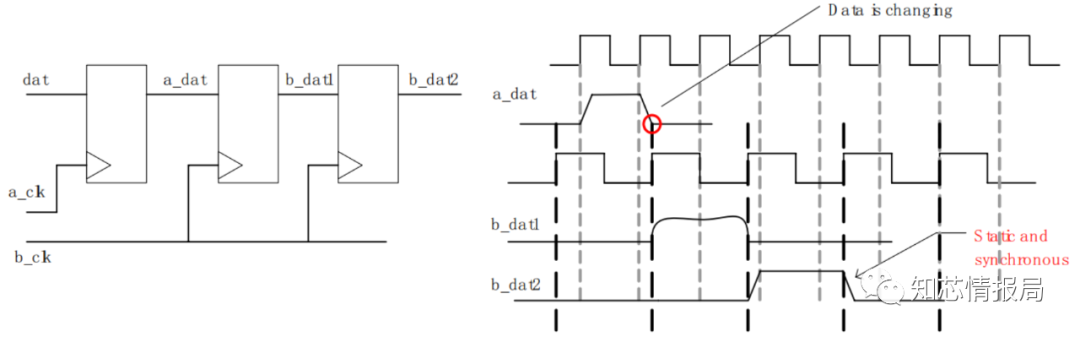

使用两级寄存器同步

也就是俗称的“打两拍”。两级寄存是一级寄存的平方,两级并不能完全消除亚稳态危害,但是大大降低了亚稳态的发生概率。a_dat是时钟域a_clk的数据,需要传输到时钟域b_clk。假设在b_clk的上升沿正好采到a_dat的跳变沿(从0变1的上升沿,实际上的数据跳变不可能是瞬时的,所以有短暂的跳变时间),那么此时a_dat为一个不确定的电平状态。所以b_dat1的值也不能确定.但至少可以保证,在b_clk的下一个上升沿,b_dat1基本上已经稳定,可以满足下一级触发器的setup/hold要求,出现亚稳态的概率得到了很大的改善。

如果再加上第三级寄存器,由于第二级寄存器对于亚稳态的处理已经起到了很大的改善作用,第三级寄存器在很大程度上可以说只是对于第二级寄存器的延拍,所以意义是不大的。

异步双口RAM

在处理多bit数据的跨时钟域时,采用较多的是异步双口RAM。假设我们现在有一个信号采集平台,ADC芯片提供源同步时钟20MHz,ADC芯片输出的数据在20MHz的时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据(多bit)。

在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。先利用ADC芯片提供的20MHz时钟将ADC输出的数据写入异步双口RAM,然后使用100MHz的时钟从RAM中读出。在能使用异步双口RAM来处理跨时钟域的场景中,也可以使用异步FIFO来达到同样的目的。

格雷码

在上面的第二种方案中,master要等RAM中有ADC的数据之后才去读RAM。这就需要100MHz的时钟对RAM的写地址进行判断,当写地址大于某个值之后再去读取RAM。程序员们使用直接用100MHz的时钟于RAM的写地址进行打两拍的方式,但RAM的写地址属于多bit,如果单纯只是打两拍,那不一定能确保写地址数据的每一个bit在100MHz的时钟域变化都是同步的,肯定有一个先后顺序。如果在低速的环境中不一定会出错,在高速的环境下就不一定能保证了。所以更为妥当的一种处理方法就是使用格雷码转换。

首先什么是格雷码?在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。在数字系统中,常要求代码按一定顺序变化。例如,按自然数递增计数,若采用8421码,则数0111变到1000时四位均要变化,而在实际电路中,4位的变化不可能绝对同时发生,则计数中可能出现短暂的其它代码(1100、1111等)。在特定情况下可能导致电路状态错误或输入错误。

使用格雷码可以避免这种错误。格雷码有多种编码形式。格雷码(Gray Code)又称Grey Code、葛莱码、格莱码、戈莱码、循环码、反射二进制码、最小差错码等。如下图所示,若不作特别说明,格雷码就是指典型格雷码,它可从自然二进制码转换而来。二进制格雷码的生成方法有很多,具体可自行搜索。

| 十进制数字 | 自然二进制码 | 典型格雷码 | 十进制余三格雷码 | 十进制空六格雷码 | 步进码 |

| 0 | 0000 | 0000 | 0010 | 0000 | 00000 |

| 1 | 0001 | 0001 | 0110 | 0001 | 00001 |

| 2 | 0010 | 0011 | 0111 | 0011 | 00011 |

对于格雷码,相邻的两个数间只有一个bit是不一样的,如果先将RAM的写地址转为格雷码,然后再将写地址的格雷码进行打两拍,之后再在RAM的读时钟域将格雷码恢复成10进制。这种处理就相当于对单bit数据的跨时钟域处理了。

审核编辑:刘清

-

多位宽数据通过握手方式跨时钟域2023-05-06 2442

-

处理跨时钟域(CDC)信号同步的最常见方法2023-09-20 6799

-

关于cdc跨时钟域处理的知识点,不看肯定后悔2021-06-21 2230

-

cdc路径方案帮您解决跨时钟域难题2017-11-30 8909

-

关于FPGA中跨时钟域的问题分析2019-08-19 4098

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 4536

-

CDC跨时钟域的基础概念2022-08-29 3686

-

CDC跨时钟域的基础概念介绍2022-12-26 2997

-

单位宽信号如何跨时钟域2023-04-13 2365

-

跨时钟域电路设计总结2023-05-18 1626

-

CDC跨时钟域处理及相应的时序约束2023-06-21 3473

-

跨时钟域电路设计—单比特信号传输2023-06-27 2308

-

跨时钟域电路设计:单位宽信号如何跨时钟域2023-08-16 2535

-

如何处理跨时钟域这些基础问题2024-01-08 1541

-

一文解析跨时钟域传输2024-11-16 2213

全部0条评论

快来发表一下你的评论吧 !