简述Duplicate Net Names的解决方法

电子说

描述

我们在日常画板子的时候,有时会出现一个比较尴尬的问题:同一个工程下不同原理图之间的相同网络标号导入到PCB文件之后,pin没有连接在一起;编译是还会出现报错,error:Duplicate Net Names。可以直接忽略,但存在报错实在让人难受。

解决这个问题,就要先了解网络标识符的几种方式。查找了相关的一些资料和大家分享下:

网络标识符有Automatic、Flat、Global、hierarchical四种方式;

四种方式的用法分别为:

①Flat方式:不同页之间只有Port(端口)具有全局属性,即在不同的sheet之间进行同名端口的连接;缺点是难于追踪。

②Global方式:不同页之间Port和netlabel都具有全局属性,缺点也是难于追踪。

③Hierarchical方式:这种适合于分等级的原理图设计中,必须有顶层和底层(每一页),顶层和底层之间是只通过SheetEntry(页入口)和各页的Ports建立对应关系,这种方式适合多页分等级的设计,各页之间的关系比较明晰,也容易追踪。

④为Automatic方式:根据判据自动判断选择上述三种方式中的一种进行设置;

具体是这样:当检查到原理图中具有页符号采用Sheet Entry和/或Ports连接子图,则自动选择HIerarchical方式;若没有Sheet Entry则判断有没有Ports,如果有Ports,则采用Flat方式进行设置作用域范围;如果没有Ports,则自动设置为Global方式。也就是说,若采用Automatic方式,当电路图中有SheetEntry时采用Hierarchical方式;当电路图中有Ports(不管不同页之间有没有同名的netlabel)时采用Flat方式;当电路图中仅有Netlabel时才采用Global方式。

出现编译错误的原因也就在于Automatic方式时软件采用的判据,如果电路中没有SheetEntry,既有natlabel又有Ports,当设置为Automatic时会按照④所述的判据自动设置为Flat方式,由①可知是Flat方式只有Port在不同页之间具有全局属性,所以软件不认为不同页之间的同名netlabel是连接在一起的,进而出现了“Duplicate Net Names Wire XXX”的错误提示,这里边字面意思是网络名重名,个人认为出现这种错误时,是设计Altium Designer的人人为设定的,不然的话设计软件的难度太大,需要检测有没有netlabel和port,一共有四种情况,况且每一种情况具有包含与被包含的关系。

所以解决的办法有:

采用层次原理图设计,顶层的SheetEntry仅仅和子页的Port之间建立连接关系。

将不同页之间同名netlabel修改为port,然后通过port建立连接关系,作用域设置为Flat或者Global或Hierarchical。 (注意:当将出现上述错误信息的原理图工程作用域设置为Hierarchical时,尽管很多错误都消失了,但是会有一个“Multiple Top Level Documents”的错误,即多个顶层文档。)

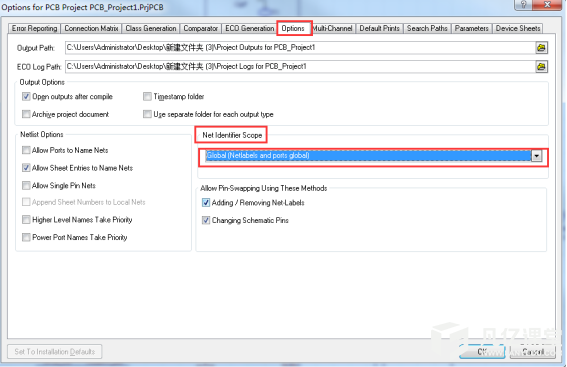

最简单但比较懒惰的方式,将作用域设置为Global方式;Project-》Project options中的Options选项下设置了一下Net Identifier Scope(网络标识符作用范围),由原来的Automatic改为Global。

-

linux中运行ifconfig出现错误解决方法2020-10-21 1161

-

总线出现-- [Error]Duplicate Net Names Element[0]: RB2014-03-12 20890

-

AD winter09出现“Duplicate Net Names Bus Slice D[0..15]j解决办法2014-03-26 20807

-

编译pcb文件时出错,Duplicate Net Names Bus Slice N000-1[0..15]2014-05-13 9181

-

altium designer编译时出现错误 Duplicate Net Names Wire Net*_12014-06-04 13525

-

不理解~~~~AD6.6 原理图出现大量duplicate net names 错误2015-07-12 30141

-

在多通道设计中出现Duplicate Net Names Bus Slice问题2018-01-08 6234

-

Duplicate Net Names Wire解决办法2019-07-23 7888

-

Altium 原理图中移动网络标号(Net Label)线也会跟着移动的解决方法2019-11-07 5384

-

Altium error:Duplicate Net Names的解决方法2019-11-12 5849

-

“Duplicate Pin Name found on P2010-01-25 2035

-

短波通信盲区现象解决方法介绍2015-11-10 1393

-

Altium-Designer-Duplicate-Net-Names-Wire-XXX解决办法2016-09-18 2369

全部0条评论

快来发表一下你的评论吧 !