触发器使用中的几个问题

描述

触发器使用中的几个问题

触发器逻辑功能的转换

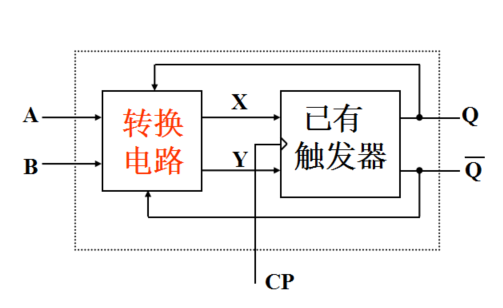

触发器逻辑功能转换示意图:

将已有触发器转换为所需触发器的功能,实际上是求转换电路,即求转换电路的函数表达式:

代数法

通过比较已有触发器和待求触发器的特性方程, 求转换电路的函数表达式.

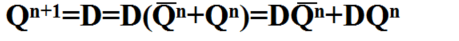

例: 把JK触发器转换为D触发器.

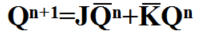

解: 已有JK触发器的特性方程为:

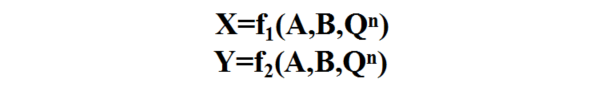

待求D触发器的特性方程为:

为求出转换电路的函数表达式,可将D触发器的特性方程转换为:

比较JK触发器的特性方程,可得:

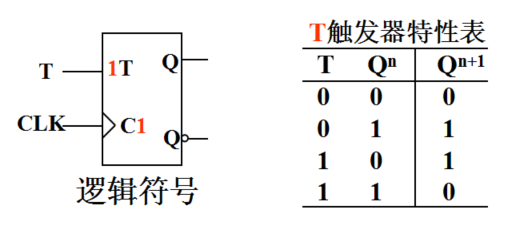

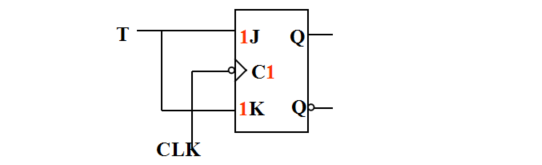

例: 将JK触发器转换为T触发器.

T触发器的特性

归纳为:

T=0 保持

T=1 翻转

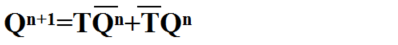

T触发器的特性方程:

将上式和JK触发器特性方程

比较,可得 J=K=T

注意:在这个电路中,由于采用的是下降边沿JK触发器,所以得到的T触发器也是下降边沿的。

图表法

例: 把RS触发器转换为JK触发器.

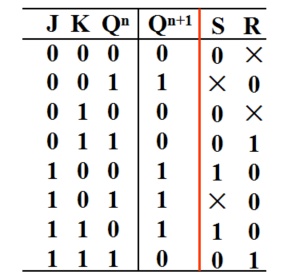

① 首先列出JK触发器的特性表;

② 根据RS触发器的特性,列出当满足JK触发器特性时S、R端应加的信号;

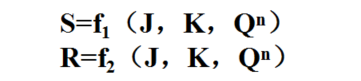

③ 写出下列两个表达式:

转换电路图

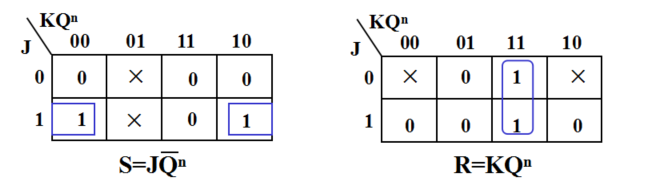

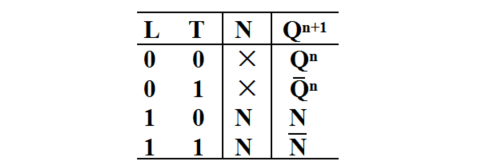

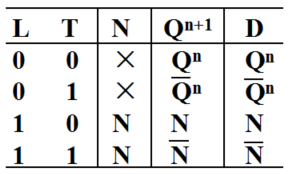

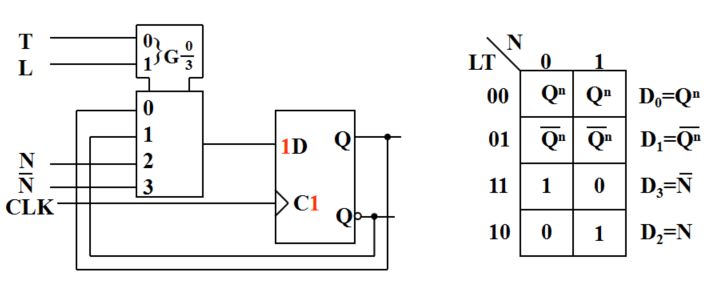

例:试用D触发器和四选一MUX构成一个多功能触 发器,其功能如下表所示。 表中L、T为控制变量,N为数据输入变量。

解:① 列表;

② 设L、T为MUX的地址 变量,求MUX的数据端输入信号;

③ 画逻辑图。

触发器的脉冲工作特性

触发器的脉冲工作特性:

指为了保证触发器可靠的动作,而对时钟脉冲、输入信号以及它们之间的时间关系所提出的要求。

输入信号的建立时间和保持时间

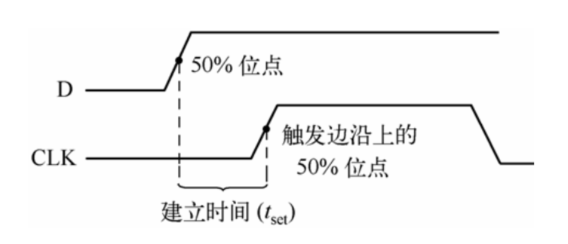

(1)建立时间

为使触发器做好触发准备,要求输入信号在时钟脉冲的边沿到来之前,提前一段时间到来,提前的这段时间叫建立时间,用t_set表示。

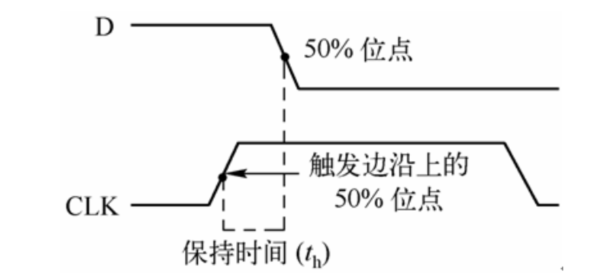

(2)保持时间

为了保证触发器可靠翻转,在时钟脉冲到达后,输入信号必须维持一段时间不变。 这段时间称为保持时间,用t_h表示。

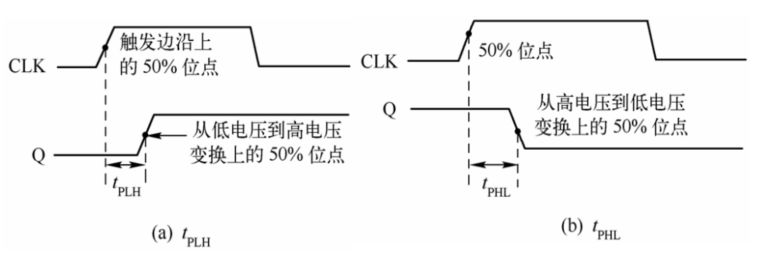

触发器的传输延迟时间

从时钟脉冲边沿到达到触发器的新状态稳定建立起来,所需要的时间叫做传输延迟时间。

tPHL表示输出端由高电平变为低电平的传输延迟时间

tPLH表示输出端由低电平变为高电平的传输延迟时间

触发器的最高时钟频率

在保证触发器可靠翻转的条件下, 所允许的时钟频率有一个上限值 (最高频率) ,该上限值即为触发器的最高时钟频率,用f_max表示。

脉冲宽度

为保证时序逻辑电路能够正常稳定地工作,要求输入信号的脉冲宽度大于最小脉冲宽度(tw)

功耗

数字电路的功耗是指它的总功率消耗,

根据该参数可以确定所需直流电源的输出容量。

例:在+5V直流电源上工作的一个D触发器,如果流经它的电流是5mA,那么功耗就是

P=VCC×ICC=5V×5mA=25mW

假设某数字系统总共需要10个触发器,并且每一个触发器都耗用25mW的功率,则总功率需求是

PT=10×25mW=250mW

说明直流电源所需要的输出容量是250mW。

如果该数字系统也工作在+5V的直流电源上,那么电源必须提供的电流量为

触发器的合理选用

1.从逻辑功能来选择触发器

如果要将输入信号存入到触发器中,则选择 D触器。

如果需要一个输入信号,且要求触发器具有翻转和保持的功能,则选择 T 触发器。

如果只需要翻转功能,则选用 T’触发器。

如果需要两个输入信号,要求触发器具有置 0、置 1、保持、翻转功能,则选用 JK 触发器。

从电路结构形式来选择触发器

如果触发器只用作寄存一位二值信号,则可以选用门控锁存器 ,这种器件电路简单、价格低廉。

如果输入信号不够稳定或易受干扰,则选用边沿触发器; 可以避免空翻现象的发生,提高电路的可靠性。

从制造工艺来选择触发器

TTL触发器的速度较快。

CMOS 触发器的优点是功耗低和抗干扰能力强。

触发器使用的注意事项

(1)集成触发器中一般都设有异步置 0 和置1端,可以利用它们给触发器设定初始状态。

(2)每一片集成触发器都有且只有一个公共的电源和地,若电路输入信号 1 则和电源相连,若输入信号 0 则和地相连。

(3)在使用触发器时,应当注意其脉冲工作特性,时钟脉冲输入和信号输入在作用时间上要很好地配合,否则就不肯能可靠地工作。

(4)一个集成电路中可能集成了一个或几个触发器,它们之间是相互独立的,可以单独使用。

-

t触发器变为d触发器的条件2024-08-22 4584

-

单稳态触发器有几个稳定状态 单稳态触发器的特点2024-02-21 4523

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 6380

-

rs触发器电路图与rs触发器内部电路图2022-10-19 35133

-

触发器的种类与触发方式2022-09-12 61111

-

电路在线维修测试中的几个问题2021-09-24 730

-

电平触发器,脉冲触发器和边沿触发器的触发因素是什么2021-02-11 11121

-

什么是触发器 触发器的工作原理及作用2019-12-25 5663

-

触发器有几个稳态2018-03-27 28753

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192895

-

电路设计中应该注意的几个问题2016-10-10 587

-

pH电极使用中应注意的几个问题2009-04-10 804

全部0条评论

快来发表一下你的评论吧 !