浅谈电磁兼容性设计

EMC/EMI设计

描述

序:电子电路在通信、计算机、自动化和其它领域被广泛应用,各种各样的电路必须在互相靠近的情况下工作,很多时候这些电路彼此间会产生不利的影响。对与电路设计工程师来说,电磁干扰(EMI)已成为一个主要问题,对于产品需要取得各种证明来说,这个问题变得更为重要。时代的发展造就集成电路的使用和大规模的集成芯片减小了电子产品的尺寸。由于电路越来越小,越来越复杂,更多的元器件被塞进极小的空间,增加了干扰的概率。此外,多来年时钟的频率急剧增加,很多情况下超多了1000MHz。现在很多家用电脑的时钟速度超过1GHz已经很普遍。

产品设计者不仅需要所设计电路在实验室理想环境下运行,还需考虑设计产品工作在其它设备附近的“现实环境”环境中正常运行,并要遵守相关电磁兼容性(EMC)规定。所有电磁兼容性应该是一个主要的设计目标。

电磁兼容性设计

电磁兼容性(EMC)是一个电子系统在预定的电磁环境下正常工作和不对电磁环境产生污染的能力,电磁环境是由辐射能量和传导能量组成的。因此电磁兼容有两个方面:发射和敏感源。

敏感性是一个设备或电路对不需要的电磁能量(即噪声)响应的能力,与敏感性相对的是抗扰度。一个电路或设备的抗扰度是指一个电磁环境,在该电磁环境下该设备可以没有下降性且良好的运行,并且有一定的安全裕量。确定抗扰度(或敏感性)水平的难度在于界定什么是性能降级。

发射涉及一个产品造成干扰的可能性。控制发射的目的是为了限制电磁能量的发射,从而控制其它产品必须工作的电磁环境。控制一个产品的发射可能会消除很多其它产品的干扰问题。因此,要产生一个电磁兼容环境最好的方法就是控制发射。

设备开发时间

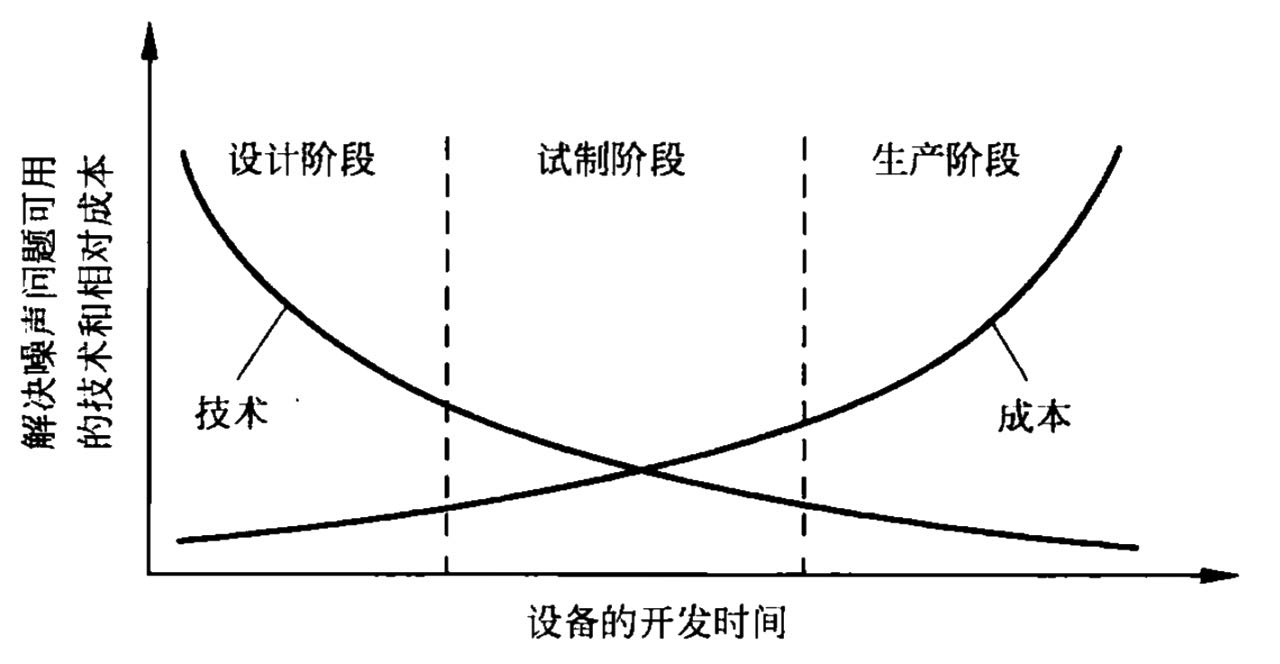

注:随着设备的开发进程,可用噪声控制技术的数量下降,与此同时,降噪成本上升。

电磁兼容可以用两种方式实现:一种是危机处理方法,另一种是系统处理方法。在危机处理方法中,设计师不考虑电磁兼容,直到完成功能设计和试制,或更糟糕的是凭经验判断问题的存在。往往实施的解决方案代价是最昂贵的,并且由不期望的附加元器件构成。通常被称“创可贴”方法。

随着产品开发的进程,从设计到测试到生产,设计师可以的降噪技术逐步减少,同时成本增加。在上图中。因此早期解决干扰问题,通常是最好的选择,成本也最低。

-

电磁兼容性分析的方法2016-08-25 0

-

怎么提高电磁兼容性2019-05-31 0

-

PCB布线对电磁兼容性的影响2020-04-13 0

-

怎样去设计高速电路的电磁兼容性?2021-04-26 0

-

如何确保满足电磁兼容性的要求?2021-05-13 0

-

进行开关电源的电磁兼容性设计2021-10-29 0

-

通信开关电源的电磁兼容性2009-07-16 602

-

电源转换器的电磁兼容性原理及设计2010-03-11 730

-

手机PCB的电磁兼容性设计2016-11-24 1561

-

一文看懂电磁兼容性原理与方法及设计2018-04-03 35075

-

浅谈电磁兼容性设计的三规律三要素五层次2019-02-14 4715

-

电磁兼容与电磁兼容性有什么区别2020-07-28 2766

-

电磁兼容性的基本概念详细说明2021-03-03 1264

-

解密EMC与EMI:电磁兼容性与电磁干扰?2024-03-29 1681

全部0条评论

快来发表一下你的评论吧 !