S32K1xx的ECC错误处理机制

描述

1. 背景

ECC(Error Correcting Code)的目的是保证RAM和Flash等存储器中数据和程序代码的完整性和可靠性,在汽车MCU中被广泛应用,引起位错误的原因有多种,包括辐射(中子或阿尔法粒子)、电磁干扰、电噪声或电路短路等原因。在原理上ECC是在对用户开放的存储器之外的区域额外增加存储单元来存储ECC计算结果,所以通常不占用额外的RAM空间,当数据被读取时ECC会实时校验待读取数据的正确性,在检测到错误时及时进行自动纠正或者产生错误通知,进而产生实施相应的安全机制。

KW45也支持RAM的ECC错误检测,最近有用户问到其工作机制和错误处理机制,刚好看到S32K1有篇文档AN12522介绍相关内容,尽管两者在RAM区间的划分,ECC支持的范围以及错误注入功能上有很多区别,但其思想基本一致,可以作为借鉴,此文直接分享(仅修改一个翻译错误之处)。

S32K1xx系列中使用的ECC方法提供单错误纠正(SEC)和双错误检测(DED)功能。本应用笔记旨在描述如何在S32K1xx系列中实现ECC保护,并了解S32K14x和S32K11x器件的特定ECC事件响应。

2. SRAM ECC错误处理

2.1 上电复位后SRAM初始化

S32K1 SRAM分为两个区域:SRAM_L和SRAM_U。RAM的实现使得SRAM_L和SRAM_U位于内存映射中的一个连续块。有关更多详细信息,可以参阅参考手册中随附的S32K1xx_memory_map.xlsx文件。

Note: S32K11x器件的SRAM_L不受ECC保护, 用作系统RAM的FlexRAM 没有ECC, LPUART和FlexCAN RAM受 ECC保护。

SRAM的复位状态未知,因此数据可能包含随机数据。对任何地址的第一次读取尝试都很可能会产生不可纠正的ECC错误。在读取每个内存地址之前,必须将其写入一个已知值。如果读取未初始化的内存地址,则读取操作可能会导致多位ECC错误和AHB上的错误。因此, SRAM必须在上电后初始化,包括外设RAM存储器,如LPUART和FlexCAN RAM。

2.2 使用的ECC算法

SRAM的ECC实现使用修改汉明码方案,该方案具有40位校验基,由32位数据和8奇偶校验位组成。

2.3 单比特错误的ECC

S32K14x 和S32K11x设备以相同的方式处理单比特错误。错误报告模块(ERM)可以生成中断(如果已启用)以通知单比特位更正事件,该事件可以通过将CR0[ESCIEx]位设置为1来启用。在事件发生后,可以通过三种方式处理错误:

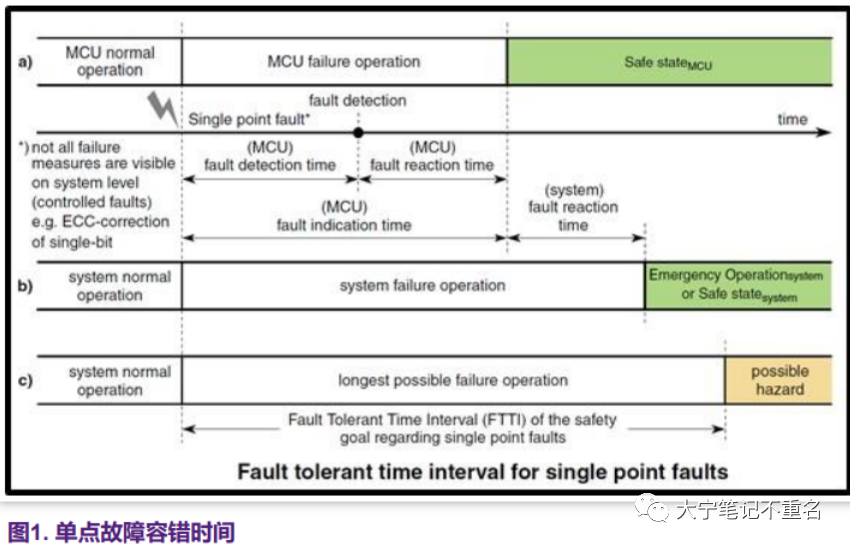

MCU正常运行:MCU检测到故障(故障检测时间)然后纠正(故障反应时间)。此时MCU继续正常运行。

具有适当的功能安全机制来管理故障:MCU检测故障(故障检测时间)然后纠正(故障反应时间)。此时软件必须切换 到safe_state_system(safe_state_system是一种没有不合理的概率发生对任何人身体伤害或健康损害的操作模式)。Safe_state_system必须由用户定义。

有任何合适的功能安全机制:MCU检测到故障(故障检测时间),然后纠正它,但没有通知用户发生了错误。容错时间间隔(FTTI)过后,可能会出现危险。

2.4 不可纠正错误的ECC

S32K14x和S32K11x设备以不同的方式处理不可纠正的错误。错误报告模块(ERM)可以生成中断(如果已启用)以通知双位错误事件,可以将CR0[ENCIEx]位设置为1来启用该事件。

S32K14x错误处理:当故障发生时,CPU跳转到错误报告模块(ERM)中断处理程序(如果启用)。

S32K11x错误处理:

当发生故障时,CPU首先跳转到硬故障(hard fault)错误中断处理程序,紧接着,ERM中断标志被置位。

此时,用户必须检查ERM状态寄存器是否显示不可纠正的ECC错误事件。

如果是,建议遵循推荐的反应(系统复位)。

Note: 必须确保在硬故障异常处理期间不对SRAM_U进行读访问,否则会导致内核锁定。因此,应更新链接器文件, 以使堆栈、向量表、硬故障处理程序中使用的变量等不应位于SRAM_U, 建议放置在SRAM_L和FlexRAM。(此处原文翻译有错)

一旦发生此事件,有三种方法可以继续:

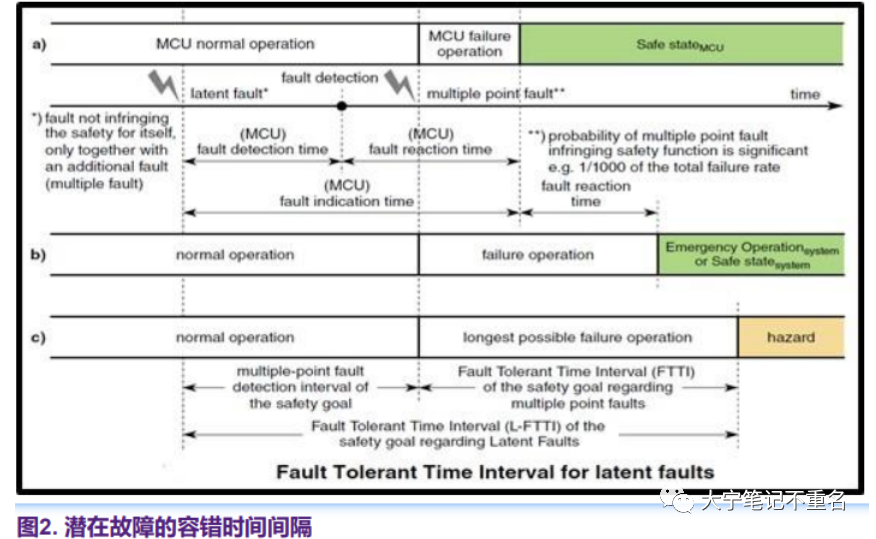

MCU正常运行:MCU检测到故障(故障检测时间)然后上报(故障反应时间)

具有适当的功能安全机制来管理故障:MCU检测到故障(故障检测时间)然后上报(故障反应时间)。

有任何合适的功能安全机制:MCU检测故障(故障检测时间)。容错时间间隔(FTTI)过后,将出现危险。

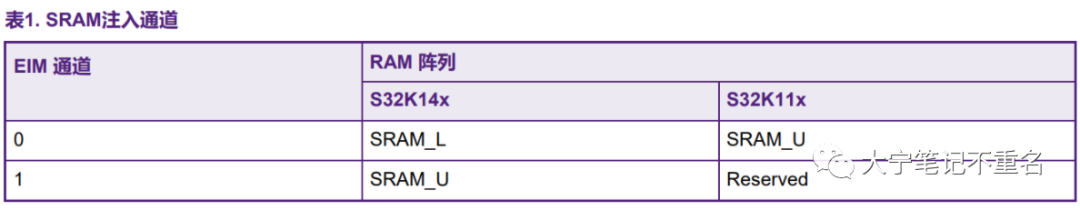

2.5 SRAM错误注入

错误注入模块(EIM)用于诊断目的,以便在访问SRAM时引发读取数据的单位和多位反转。当EIM用于向内存注入故障时,对SRAM的任何访问都会产生相应的注入错误(单位或双位错误)。EIM支持两个错误注入通道,分别对应于特定的RAM阵列。下表显示了不同S32K1xx衍生产品的通道分配。

对于安全应用,建议检查将错误注入SRAM的ECC功能,以检查此类错误的报告。

3. FLASH ECC错误处理

S32K1xx Flash中实现的ECC逻辑可以自动纠正单比特故障,并可以检测每个NVM分区(section)的多比特故障。使用 FERCNFG[DFDIE]位启用多位故障。当检测到多位错误时,FERSTAT[DFDIF]标志置位,产生中断请求。当FlexNVM区域配置为模拟EEPROM时,在从模拟EEPROM读取数据复制到EEERAM之前,任何单位ECC错误都会自动更正。在有效的模拟EEPROM位置上的任何双位ECC错误,包含需要复制到EEERAM的数据,反映为EEERAM中都为1的相应数据记录。

3.1 使用的ECC算法

NVM存储器的ECC实现使用修改汉明码方案,该方案具有72位校验基,由64位数据和8个奇偶校验位组成。

3.2 不可纠正错误的ECC

S32K14x和S32K11x设备以相同的方式处理不可纠正的错误。闪存模块(FTFC)可以生成中断(如果已启用)以通知多位错误事件,该事件可以通过将FERCNGFG[DFDIE]位设置为1来启用。

• S32K1xx错误处理:当故障发生时,FERSTAT[DFDIF]标志置位,通知检测到双位故障。闪存控制器将生成导致总线故障 (bus fault)的AHB错误响应(如果启用)。处理总线故障后,跳转到闪存模块(FTFC)中断处理程序(如果已启用)。软件可以根据错误发生在代码空间还是数据空间来处理错误。

如果在执行机器异常过程中出现不可纠正的错误故障,则应进入安全状态。

默认情况下禁用总线故障。因此,它将升级为硬故障(hard fault)。

3.3 闪存错误模拟

闪存模块(FTFC)允许用户模拟FERSTAT[DFDIF]标志的设置已检查相关的中断程序。设置FERCNFG[FDFD]位会创建错误仿真。

考虑到真正的流程是在进入闪存错误处理程序之前首先跳转到BusFault(如果启用)。

不允许对闪存位置内的位进行累积编程(没有擦除的情况下连续编程操作)

审核编辑:汤梓红

-

嵌入式编程错误处理机制设计2023-04-28 1565

-

S32K1XX系列MCU复位问题的解决方法2023-08-23 4401

-

Rust语言中错误处理的机制2023-09-19 2673

-

S32K1xx系列MCU的EEE(Emulated EEPROM)使用详解 精选资料分享2021-09-13 2548

-

S32K1xx系列MCU启动过程是怎样的2021-11-01 1728

-

如何搭建s32k1xx的环境?2022-02-09 1641

-

安装S32SDK S32K1XX RTM 4.0.2,IDE无法识别安装是怎么回事?2023-03-30 816

-

S32K3xx EMIOS模块与S32K1xx FTM模块相比有什么优势?2023-03-31 1000

-

S32K1xx开发包和S32K1实时驱动的区别是什么?2023-05-24 713

-

AN5426,S32K1XX微控制器的硬件设计指南2020-12-22 2169

-

NXP半导体产品S32K1XX数据手册下载2021-08-02 1860

-

vb关闭当前应用重新加载_S32K1xx系列MCU应用指南之芯片锁死(lockup)复位原因分析与恢复方法详解...2021-10-28 1319

-

S32K1xx系列MCU的EEE(Emulated EEPROM)使用详解2021-11-18 2014

-

西门子博图:错误处理机制概览2023-11-25 5423

-

C语言中的错误处理机制解析2024-02-26 1353

全部0条评论

快来发表一下你的评论吧 !