一文详解锁存器

描述

锁存器

存储电路由存储器件组成,能存储一位二值信号的器件称为存储单元电路,存储单元电路大多是双稳态电路。

双稳态电路特点:

①具有两个稳定状态,用0 和1表示,在无外信号作用时,电路长期处于某个稳定状态,这两个稳定状态可用来表示一位二进制代码。

②它有一个或多个输入端,在 外加信号激励下,可使电路从一个状态转换成另一个状态。

两类存储单元电路 :

(1) 锁存器 (2) 触发器

锁存器: 直接由激励信号控制电路状态的存储单元.

触发器: 除激励信号外,还包含一个称为时钟的控制信号输入端. 激励信号和时钟一起控制电路的状态.

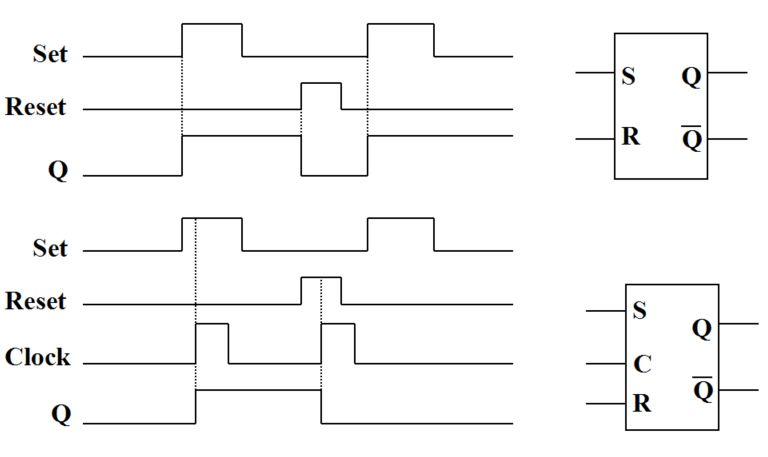

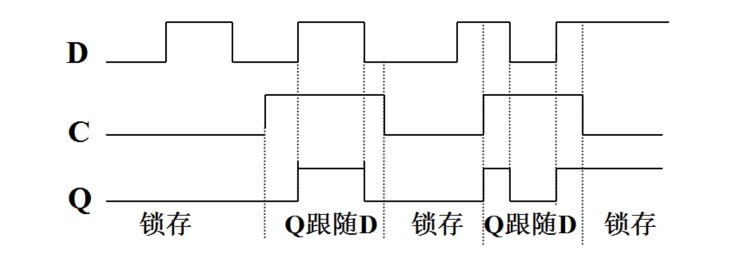

锁存器和触发器工作波形示意图:

普通锁存器

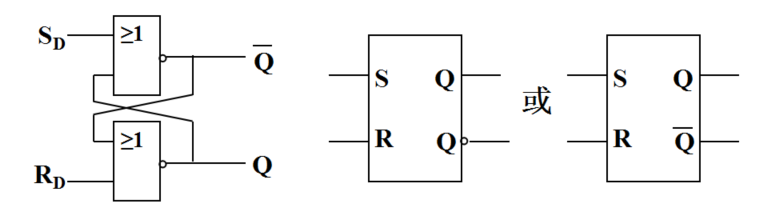

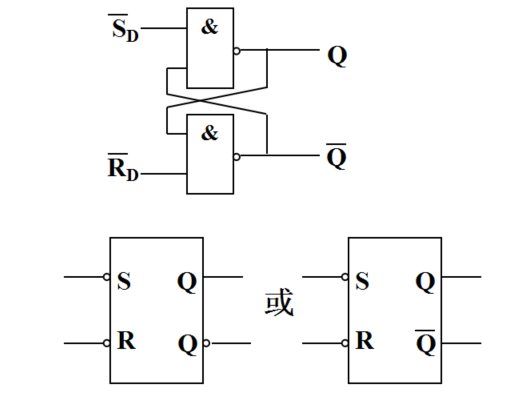

1. RS 锁存器的电路结构及逻辑符号

两个输入端(激励端):

SD :置位端(置1端);

RD :复位端(置0端);

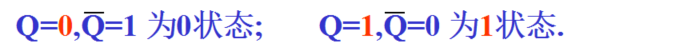

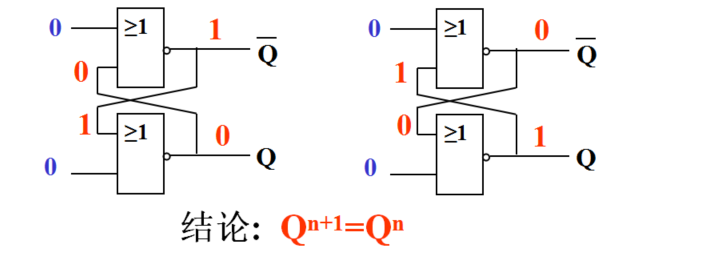

定义:

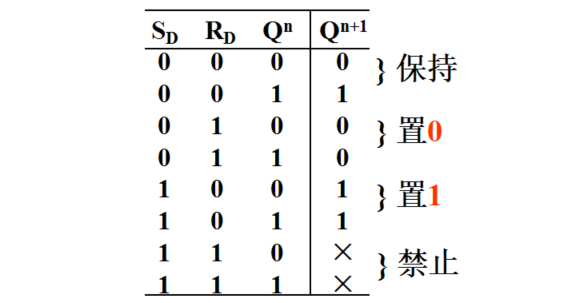

2. RS 锁存器的逻辑功能分析

设: 电路的原状态表示为Q^n,新状态表示为Q^n+1.

① SD=0; RD=0 (无激励信号),有下列两种情况:

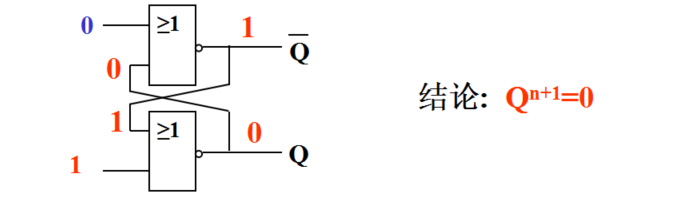

② SD=0; RD=1 (置0信号有效):

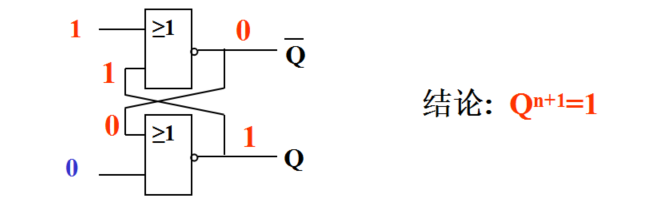

③ SD=1; RD=0 (置1信号有效):

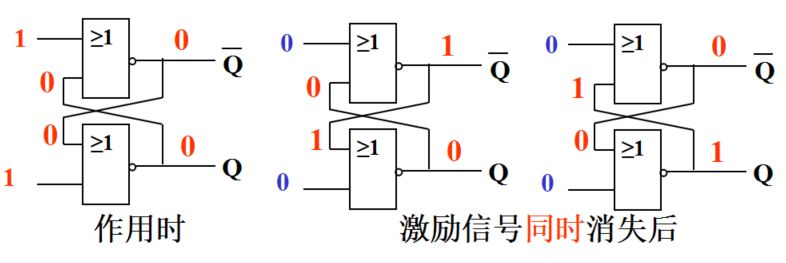

④ SD=1; RD=1 (置0、置1同时信号有效):

一般情况下,SD=RD=1应禁止使用。

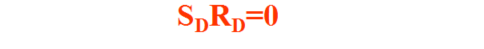

RS锁存器的约束条件:

由与非门构成的RS锁存器:

3 RS锁存器的功能描述

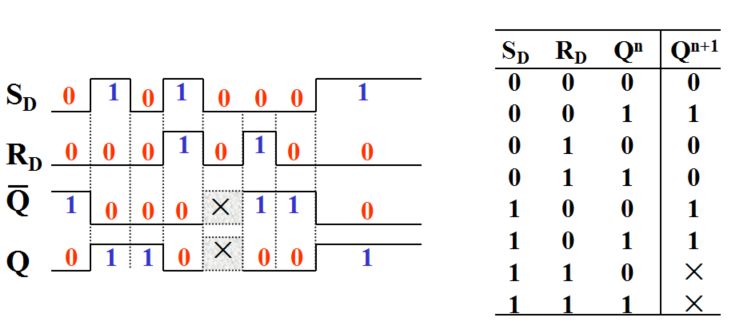

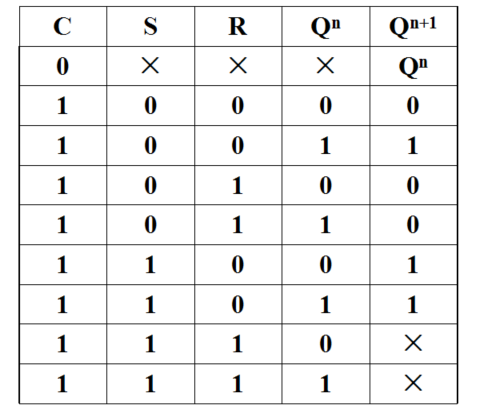

① 特性表

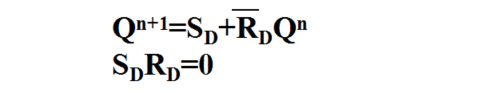

② 特性方程

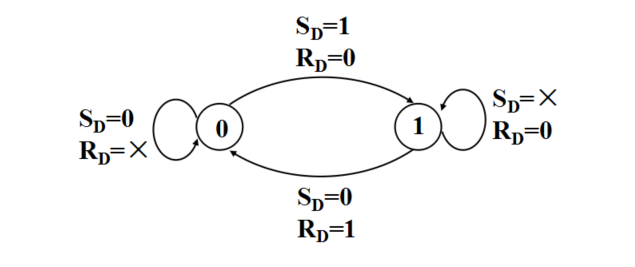

(3)状态图

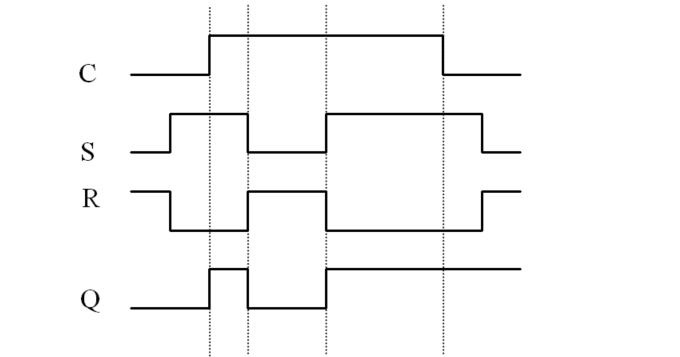

(4) RS锁存器工作波形图

(初态假设为0)

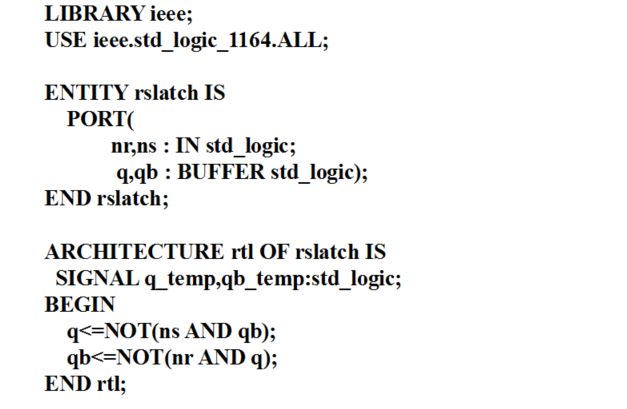

4. RS 锁存器的 VHDL 描述

门控锁存器

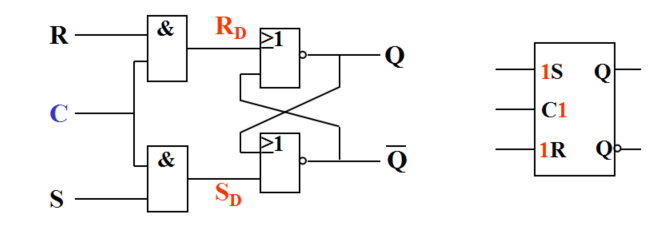

1. 门控RS锁存器

在RS锁存器的基础上, 加控制信号,使锁存器状态转换的时间,受控制信号的控制.

(1)门控 RS 锁存器的电路结构及逻辑符号

(2)门控 RS 锁存器的逻辑功能分析

当C=1时:门控RS锁存器功能和RS锁存器完全相同;

当C=0时:RD=SD=0,锁存器状态保持不变.

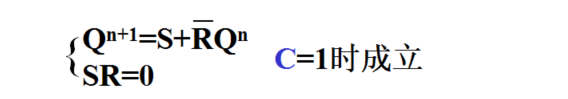

(3)门控 RS 锁存器的逻辑功能描述

1) 门控RS锁存器特性方程:

2) 门控RS锁存器特性表:

3) 门控RS锁存器工作波形图:

2. 门控 D 锁存器

能将呈现在激励输入端的单路数据D存入交叉耦合结构的锁存器单元中.

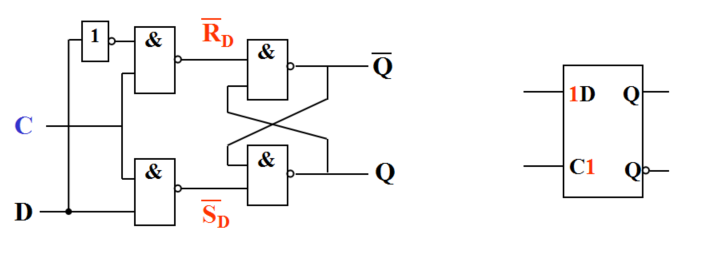

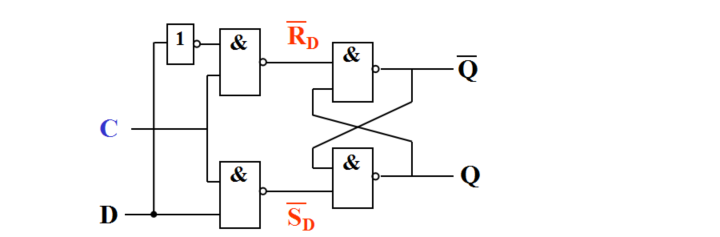

(1)门控 D 锁存器的电路结构及逻辑符号

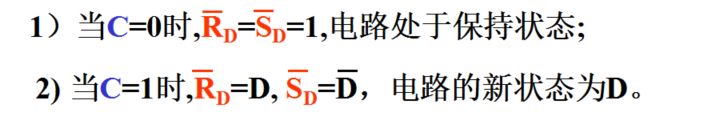

(2)门控 D 锁存器的逻辑功能分析

(3)门控 D 锁存器的逻辑功能描述

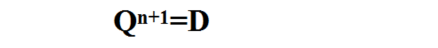

1)D锁存器特性方程:

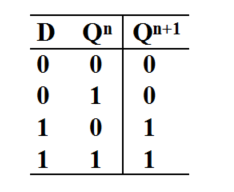

2)D锁存器特性表:

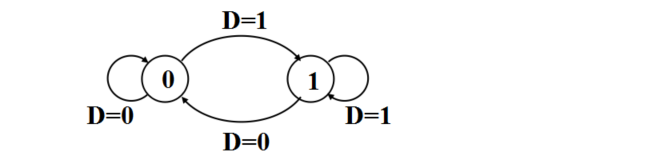

3)状态图:

4)D锁存器工作波形图: (假设初态为0)

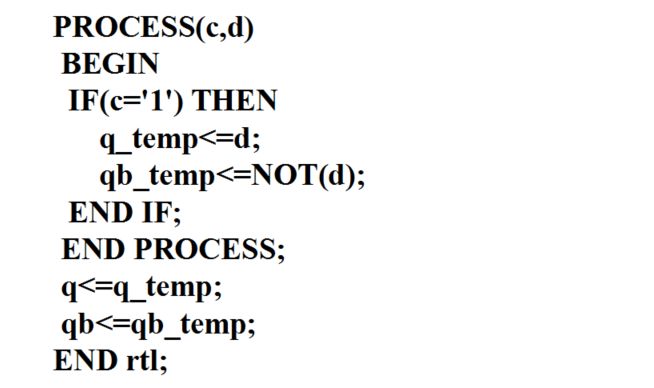

(4)门控 D 锁存器的 VHDL 描述

部分常用集成锁存器

-

一文详解pcb回流焊温度选择与调整2023-12-29 3116

-

一文详解pcb的组成和作用2023-12-18 3380

-

一文详解pcb微带线设计2023-12-14 6146

-

一文详解pcb的msl等级2023-12-13 15621

-

一文详解PCB半成品类型2023-12-11 2985

-

一文详解smt钢网开口要求2023-12-04 5323

-

一文详解TVS二极管2023-11-29 3021

-

一文详解pcb地孔的作用2023-10-30 2803

-

一文详解pcb和smt的区别2023-10-08 5477

-

一文彻底理解锁存器2023-04-25 15801

-

一文详解分立元件门电路2023-03-27 4564

-

一文详解精密封装技术2022-12-30 2350

-

一文详解蓝牙模块原理与结构2020-11-26 5228

-

51内核迪文串口屏模拟手势解锁功能(九宫格&滑动)2018-10-31 5085

全部0条评论

快来发表一下你的评论吧 !