对输出端的噪声进行建模

描述

看razavi射频微电子中,LNA设计的一章,发现上面计算架构的噪声系数时,基本的步骤是,先算出每个器件在输出端的噪声贡献,然后再将其叠加。

要做到这一步,即可以分析器件的噪声性能,可以通过电压源和电流源等熟悉的元件对器件的噪声进行建模。

电阻的热噪声

环境热能导致电阻中的电荷载流子随机运动,从而产生噪声。

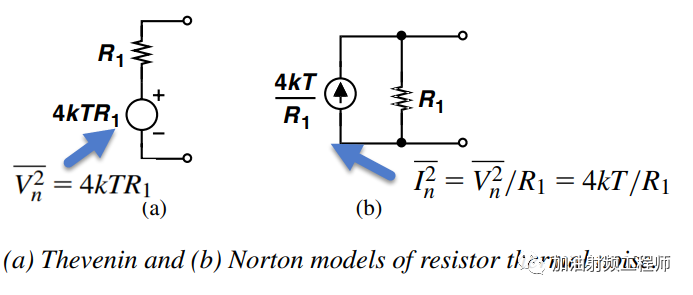

这个噪声可以通过一个级联电压源,或者并联的电流源来模拟。电压源和电流源的功率谱密度(PSD,power spectral density), 如下图所示。模型有时候可以简化分析,电压源和电流源的极性并不重要,但是在给定电路的计算中,需要保持一致。

那么,如果电阻将环境热量转换为噪声电压或电流,我们能否从电阻中提取能量呢?

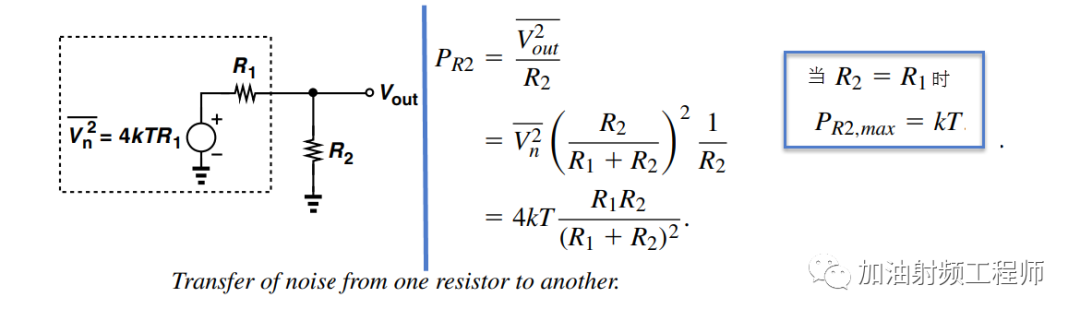

有趣的是,如果R1和R2处于同样的环境温度,它们之间没有净流量传递,因为R2同样会产生同样的噪声电压。但是,如果R2的环境温度T=0K ,那么R1会持续地从它的环境中吸收能量,把它转换为噪声,然后把能量传输给R2.

传递给R2的平均能量为:

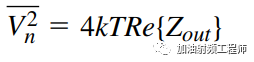

对于一个热噪声噪声密度为4KTR1的电路来说,它不需要一定要包含电阻R1.

如果无源电路耗散能量,那么它一定包含一个物理电阻,因此一定会产生热噪声。我们可以笼统的说,有耗电路就有噪声。

比如:如果一个无源(互易)网络的两个端口之间的阻抗的实部等于Re{Zout}, 如下图所示,那么这两个端口间热噪声的PSD为:

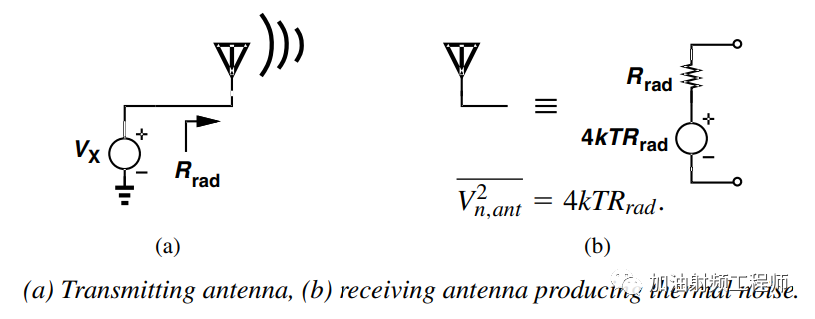

这个理论,并不局限于集总电路。

比如说,一个天线,如果作为发射天线,则其向外辐射能量,其中Rrad称为辐射电阻,作为接收天线,天线会产生热噪声,如下图所示。

严格来说,这是不正确的,因为接收天线的噪声实际上是由“背景”噪声(例如宇宙辐射)给出的。然而,在 RF 设计中,通常假设天线噪声为 4kTRrad。

MOSFET中的噪声

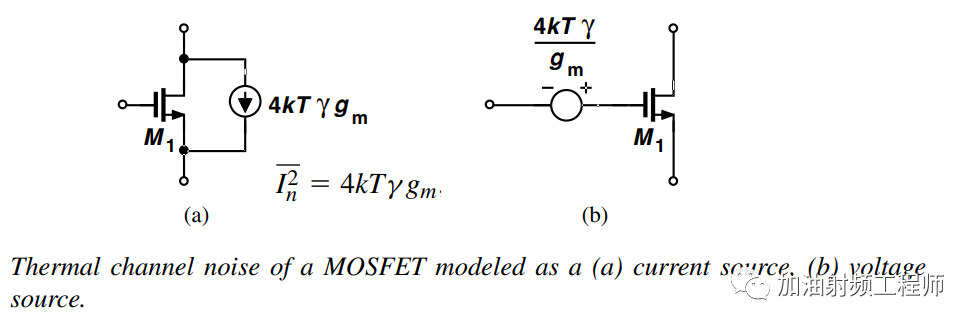

工作在饱和区的MOS晶体管的热噪声,可以近似地用源极和漏极之间的电流源表示。如下图所示。

其中, γ为过量噪声系数,"excess noise coefficient",gm为跨导(transconductance).

对于长沟道晶体管,γ的值为2/3;对于短沟道晶体管,γ的值为2.

γ的实际值,还取决于其他因素,通常通过对每一代 CMOS 技术的测量获得。

噪声也可以用电压源与MOS管的栅极级联来模拟,如上图所示。

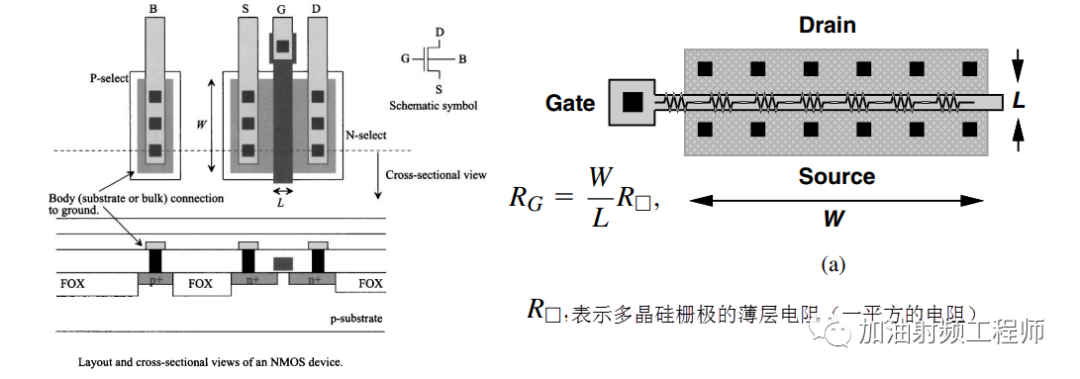

热噪声的另一个组成部分,是来自MOS管的栅极电阻,而且当栅极长度缩小时,这个效应会变得更加重要。

如下图所示,MOS管的宽度为W,长度为L。

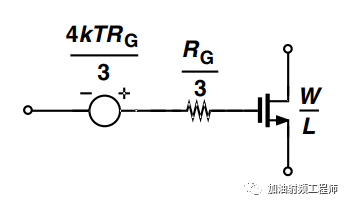

可以证明,这个结构,可以简化成一个集总模型,其等效栅极电阻为RG/3,热噪声PSD为4KTRG/3.

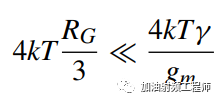

在一个好的设计中,这个噪声必须小于沟道的噪声,即

栅极和漏极之间也存在电阻,但是这可以通过使用multiple fingers来减小。

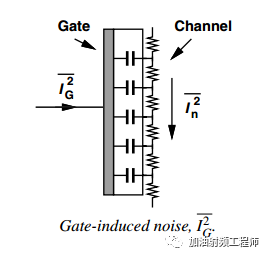

高频的时候,从沟道流过的热噪声电流会通过电容耦合耦合到栅极,因此产生栅极感应噪声电流“gate-induced noise current”。如下图所示。该效应,并未在典型的电路放置器中建模,但其重要性仍然不清楚。

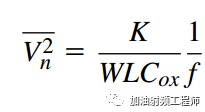

MOS管也有闪烁噪声,又称为"1/f"噪声。

可以用与栅极级联的电压源来模拟,这种噪声的功率谱密度为:

其中,K是一个与工艺相关的恒量。在大多数的CMOS工艺中,PMOS 器件的 K 低于 NMOS 晶体管,因为前者携带电荷远低于氧化硅界面,因此受“表面状态”(悬空键)的影响较小。

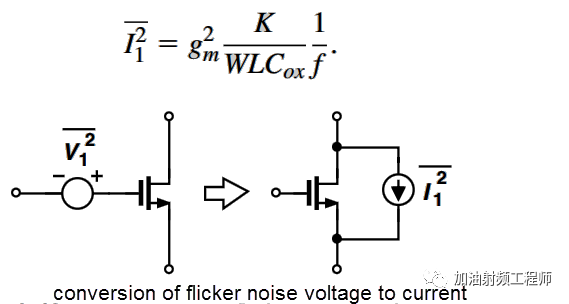

同样的,闪烁噪声也可以通过一个电流源来模拟。

如下图所示,与MOS管栅极相连的电压源,可以等效为连接在漏极和源极之间的电流源,其值为gmV1。

所以,可以得到下图。

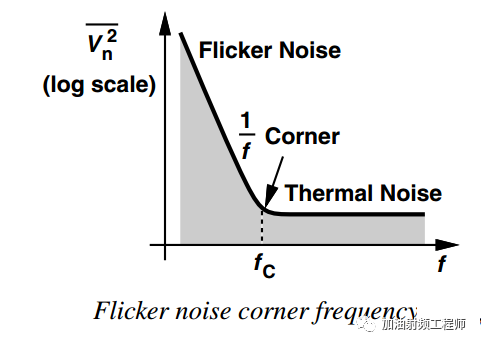

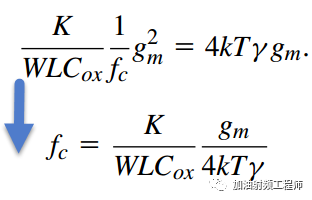

给定器件尺寸和偏置电流,1/f噪声的功率谱密度和热噪声的功率谱密度,在某个频率点相交,称为“1/f 噪声转角频率”,如下图所示。

将热噪声电流等于闪烁噪声电流,求得的f即为1/f噪声拐角频率,如下式所示。

在现代CMOS工艺中,拐角频率处于几十甚至几百MHz的范围内。

虽然闪烁噪声的影响在高频下似乎可以忽略不计,但我们必须注意,混频器和振荡器等电路中的非线性或时间变化,可能会将1/f闪烁噪声转换到射频领域。

审核编辑:刘清

-

如何评估ADA4610的偏置电流噪声给输出端带来了多大的噪声?2023-11-13 511

-

低噪声放大器输入端和输出端匹配原则是什么?阻抗匹配的目的是什么?2023-10-20 3400

-

怎么使用LTspice教程进行噪声分析?2023-10-02 6714

-

为什么漏端输出阻抗没有噪声效应?2023-09-20 1241

-

新型电荷泵提供低输入和输出噪声2023-02-08 1826

-

verilog_a怎么进行建模?怎么去表征PLL每个子模块的噪声?2021-06-25 3182

-

LTC6360:具有真零输出的超低噪声单端SAR ADC驱动器2021-04-22 751

-

偏置电流、失调电流与噪声增益对输出直流噪声的影响2020-12-24 2225

-

最领先的噪声建模与噪声测试技术2018-11-11 587

-

AD8421的差分输出噪声正端信号噪声较大2018-10-25 4751

-

使用TINA-TI进行噪声分析的噪声仿真特性2018-09-17 13481

-

低噪声前级视频链路的建模与仿真_陈智2017-03-19 584

-

铝基板输出纹波噪声的测试方法2010-06-10 709

-

PLL-FS 行为级建模仿真进行噪声和抖动性2009-12-14 785

全部0条评论

快来发表一下你的评论吧 !