汽车SoC之16-32核心的CPU架构设计

处理器/DSP

描述

汽车SoC尤其是针对自动驾驶的,更强调多核性能,手机领域则强调单核性能,所以手机领域ARM特别推出了特大核Cortex-X系列,且频率越来越高,下一代的Cortex-X4据说频率接近4GHz,可以说已基本走到了尽头无法再前进了,只能靠提高频率来提高性能了。

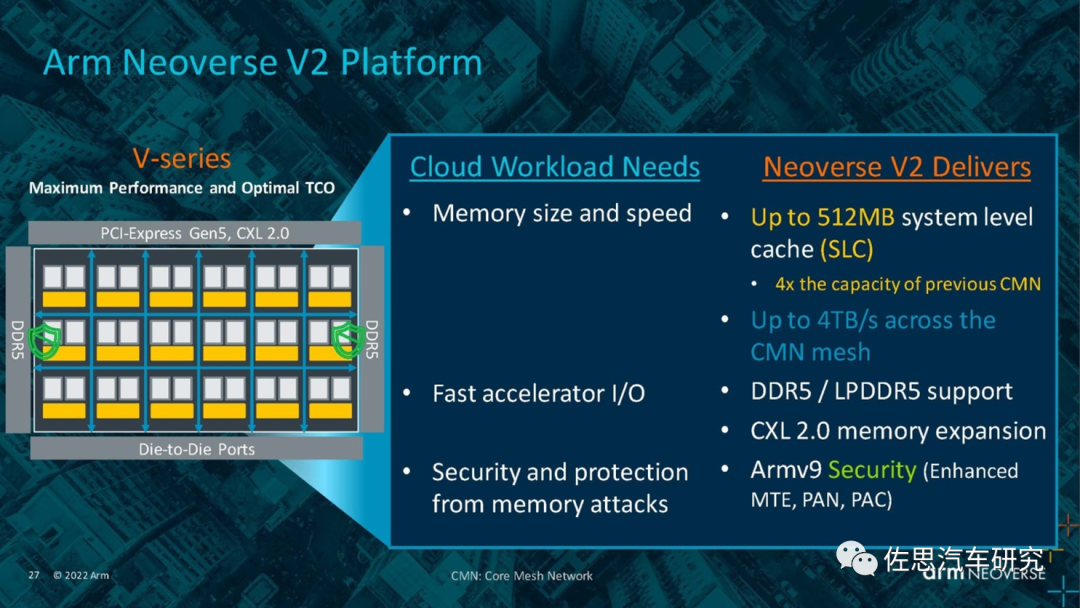

汽车领域则核心数量越来越多,高通的SA8540P、安霸的V3都是16个核心,V3是16个Cortex-A78,而特斯拉的二代FSD是20个Cortex-A72,英伟达的下一代Thor可能是32核心。座舱领域也有这个趋势,例如芯驰的产品X9U,使用了14个Cortex-A55核心,地平线的下一代J6也很有可能使用16个Cortex-A55核心。比较在意成本的厂家一般还是选择Cortex-A系列,比较重视性能的则采用ARM的Neoverse系列,这个系列就是针对服务器开发的,特别适合多核系统,这一代如华为的MDC系列SoC就是采用了ARM Neoverse的N1内核,英伟达的下一代Thor则是采用了ARM Neoverse的V2内核,Waymo和Cruise也很有可能采用了ARM Neoverse的N2内核。

ARM服务器芯片最早可追溯到2013年,华为在2013年开始用ARM架构与指令集设计服务器芯片,2015年基于Cortex-A57推出第一款ARM服务器芯片Hi1610。2019年推出鲲鹏920,也就是Hi1620,MDC的车载SoC实际就是ARM服务器CPU(即鲲鹏系列)加达芬奇AI加速器(即昇腾系列)。

图片来源:ARM

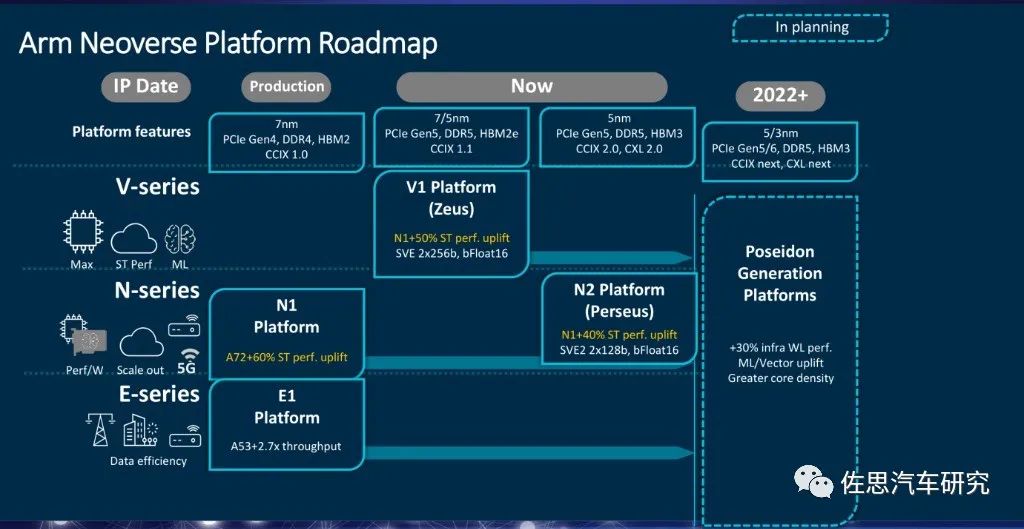

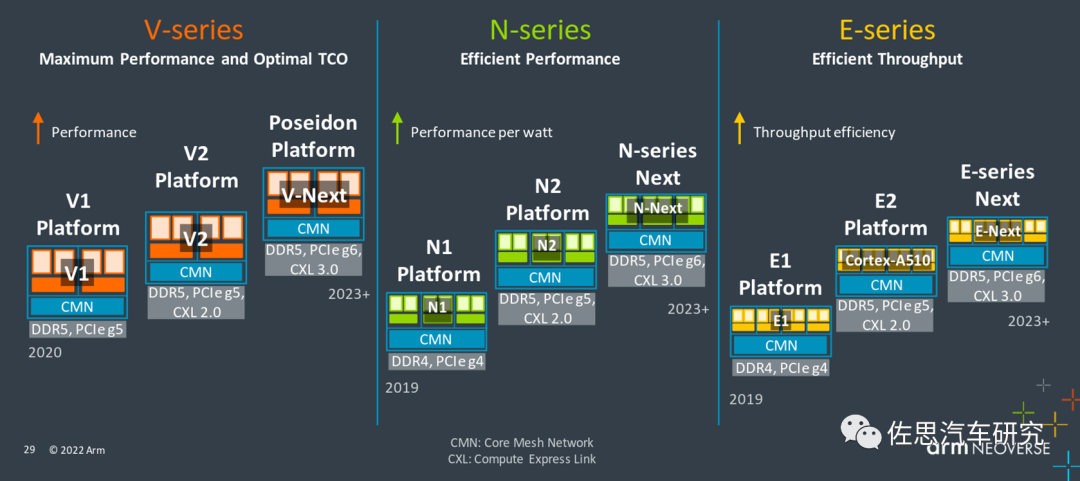

ARM Neoverse分V、N和E三个系列,V系列强调性能,E系列强调效率,N系列是性能与效率的平衡,E系列实际就是手机领域的小核心。

图片来源:ARM

原本计划2022年推出的Poseidon即波塞冬推迟到了今年下半年或明年,而E2平台就是目前旗舰手机常用的A510核心。

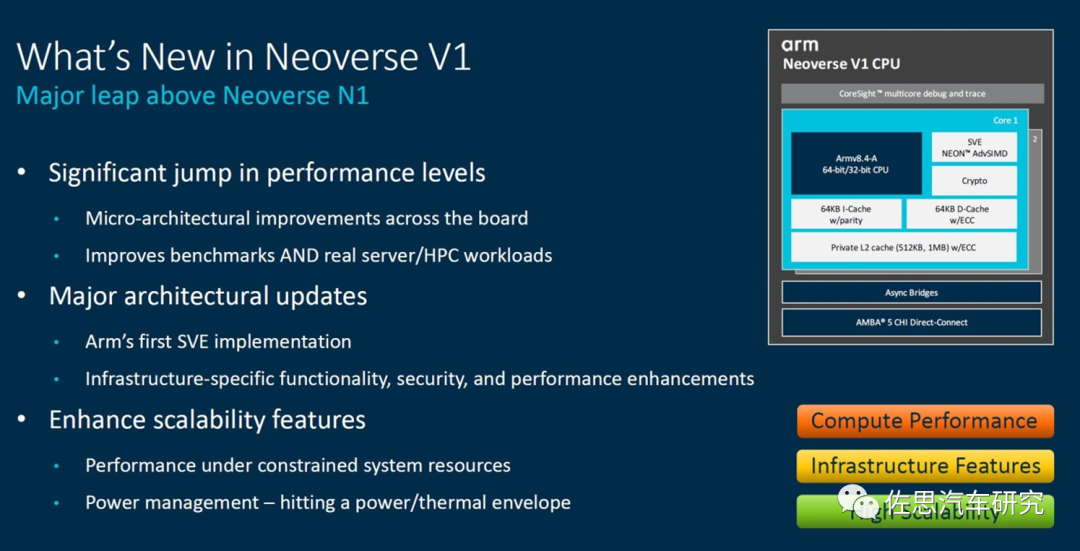

图片来源:ARM

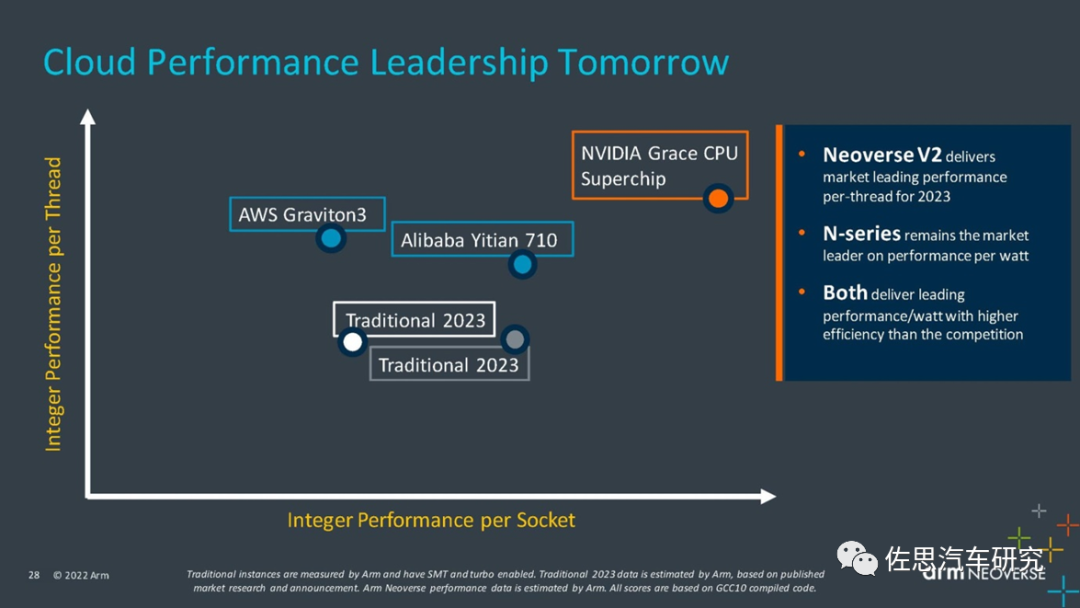

所谓“传统”就是指x86服务器,ARM服务器芯片典型代表有阿里的倚天710、亚马逊的Graviton3,倚天710使用了N2内核,亚马逊使用了V1内核。

图片来源:ARM

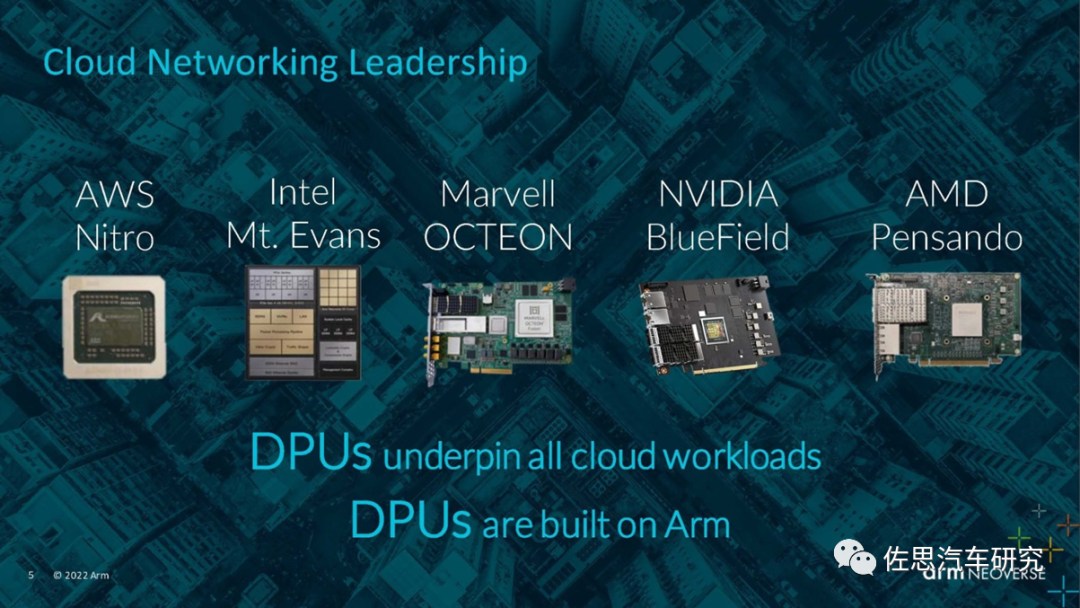

除了服务器,还有很多DPU使用了ARM的N2内核,典型代表如上图中Marvell的Octeon,采用了8-36个N2核心,均采用5纳米工艺。

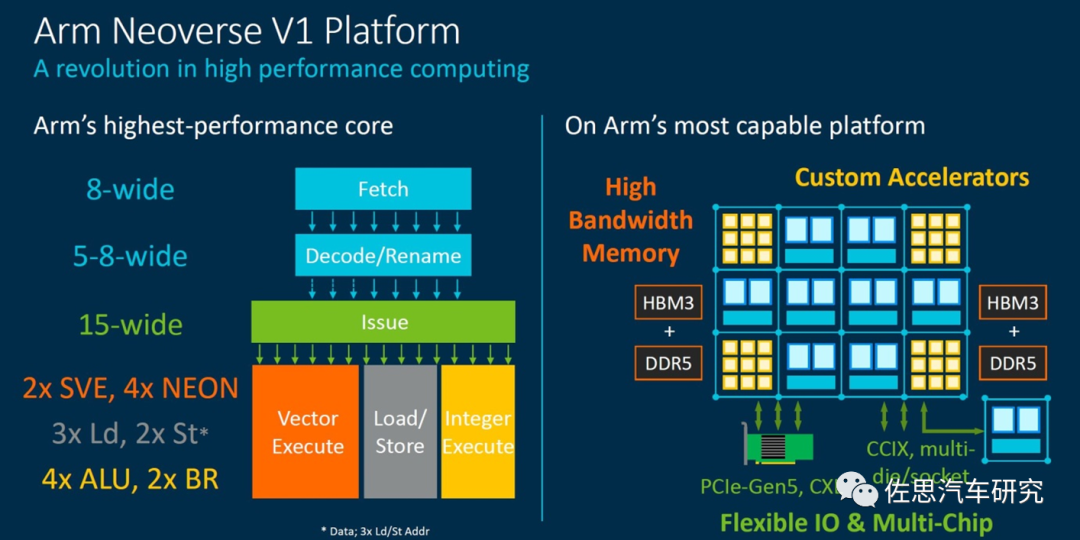

V1平台简介。图片来源:ARM

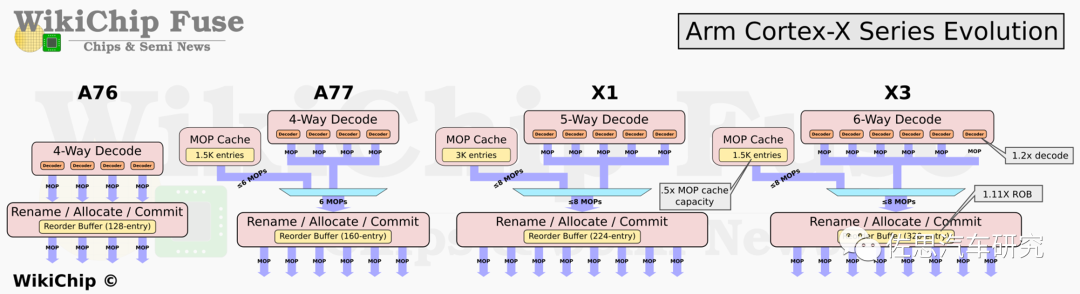

图片来源:WikiChip

和手机领域的旗舰架构X3比,V1显然要更强,ARM为自己留下了充足的挤牙膏空间,X3仅有6路解码,V1则是5-8路可选,解码器宽度是衡量CPU性能最关键的参数,没有之一。解码器宽度即IPC(每周期执行指令数),解码器宽度8,简单地说就是一个周期能执行8条指令,而X3是6条,英伟达Orin和安霸V3用的Cortex-A78解码器宽度是4,单这一点上,V1的性能就是其两倍。顺便说下,苹果M1的Firestorm核心是8路,所以苹果的单核性能一直吊打安卓的ARM。

图片来源:ARM

除了IPC宽度,其次就是L1/L2缓存大小,因为指令是从缓存中取得的,L1缓存有分为L1i和L1d,分别用来存储指令和数据。L2缓存是不区分指令和数据的。L3缓存多个核心共用一个,通常也不区分指令和数据。还有一种缓存叫TLB,主要用来缓存MMU使用的页表,通常我们讲缓存(Cache)的时候是不算它的。L1/L2缓存通常都是最快的SRAM,L3则可以用Chiplet的形式外接HBM或DDR5。当然缓存越大,Die Size就越大,成本就越高。

数据来源:各公司资料

苹果的优势非常明显,实际上这主要是台积电的功劳,为了照顾大客户,台积电的工艺特别配合苹果的设计,能够放下超大容量4MB的L2缓存但又不特别占面积,成本不至于高出ARM太多,所以苹果离不开台积电,一旦台积电不供应苹果芯片,苹果5年内都不可能把订单转移到三星,打击台积电可以轻易击倒苹果。性能上,V1/V2系列比X1/X3要高出许多。

图片来源:ARM

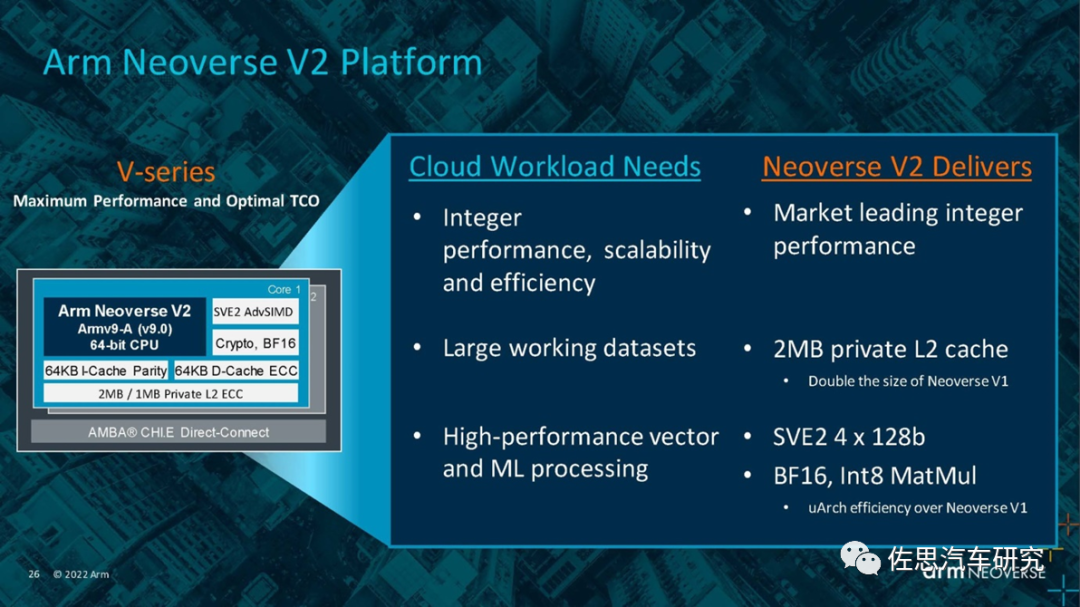

V2相对V1系列,主要就是把L2缓存提高到2MB,V1是基于Armv8.4-A指令集,V2是基于Armv9.0-A指令集,针对矢量计算和机器学习,V2将SVE升级到SVE2代,4个128比特宽度,一次可执行64个Int8指令。CPU基本可以等同于DSP做机器学习计算。对应数据格式增加了BF16。

编辑:黄飞

-

汽车电子电气架构设计仿真解决方案2023-11-13 2439

-

架构与微架构设计2023-05-08 2290

-

汽车SoC电源架构设计2022-12-21 1103

-

ARM推荐的SOC架构设计是各自独立复位?还是关联同时复位?2022-08-03 2150

-

如何有效地开展FPGA/SoC架构设计工作?2021-06-23 2747

-

多核心CPU和SoC芯片及其工作原理2021-01-06 17061

-

【设计技巧】FPGA架构设计漫谈2019-08-02 2648

-

Intel首推大小核混合CPU架构2019-02-05 5583

-

基于ARMCortex_M3核的SoC架构设计及性能分析2017-09-29 1056

-

【汽车电气架构设计软件】2017-04-18 6220

-

汽车电子电气架构设计及优化措施2016-10-18 5491

-

软件架构设计教程2016-09-26 3361

全部0条评论

快来发表一下你的评论吧 !