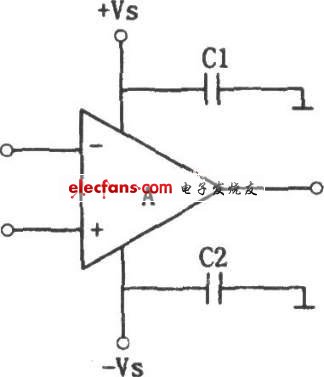

运放电源去耦旁路图

运算放大器电路

252人已加入

描述

每个集成运放的电源引线,一般都应采用去耦旁路措施,如图所示图中的高频旁路电容,通常可选用高频性能优良的陶瓷电容,其值约为0.1μF。或采用lμF的钽电容。这些电容的内电感值都较小。在运放的高速应用时,旁路电容C1和C2应接到集成运放的电源引脚上,引线尽量短,这样可以形成低电感接地回路。

注:当所使用的放大器的增益带宽乘积大于10MHz时,应采用更严格的高频旁路措施,此时应选用射频旁路电容,对于通用集成芯片,对旁路的要求不高,但也不能忽视,通常最好每4~5个器件加一套旁路电容。不论所用集成电路器件有多少,每个印刷板都要至少加一套旁路电容。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

风舞秋

2014-07-27

0 回复 举报受教了,谢啦~ 收起回复

风舞秋

2014-07-27

0 回复 举报受教了,谢啦~ 收起回复

-

yu872006

2013-10-17

0 回复 举报板子上面是在每个运放电源引脚旁加,还把所有旁路电容集中放在一起呢? 收起回复

yu872006

2013-10-17

0 回复 举报板子上面是在每个运放电源引脚旁加,还把所有旁路电容集中放在一起呢? 收起回复

-

EE-253:SHARC处理器的电源旁路去耦2025-01-06 363

-

[转] 去耦电容和旁路电容的区别2022-11-04 14326

-

旁路电容和去耦电容的基础知识2022-10-25 2331

-

旁路(输入)和去耦(电源和输出)2022-01-11 691

-

旁路电容与去耦电容到底是什么?2021-06-23 5130

-

旁路电容、去耦电容及滤波电容的作用详解2021-06-22 6233

-

去耦电容和旁路电容相关资料分享2021-05-25 2147

-

旁路电容、去耦电容、滤波电容的作用分别是什么2021-03-17 3445

-

电容去耦和旁路的区别2021-01-11 2147

-

旁路电容和去耦电容总结2018-12-07 2699

-

高速电路去耦和旁路特性2018-11-23 2301

-

滤波电容、去耦电容、旁路电容作用2015-10-29 1572

-

去耦电容和旁路电容的区别2011-02-15 9050

全部0条评论

快来发表一下你的评论吧 !