怎样才叫学好了FPGA?

电子说

描述

今天在群里有工程师问我,怎么才叫学会了FPGA,怎么才叫学好了FPGA?我相信有很多朋友有类似的问题,因为在多数人的潜意识里,FPGA是非常高深莫测的技术,能够玩转FPGA的都是大神级的人物。

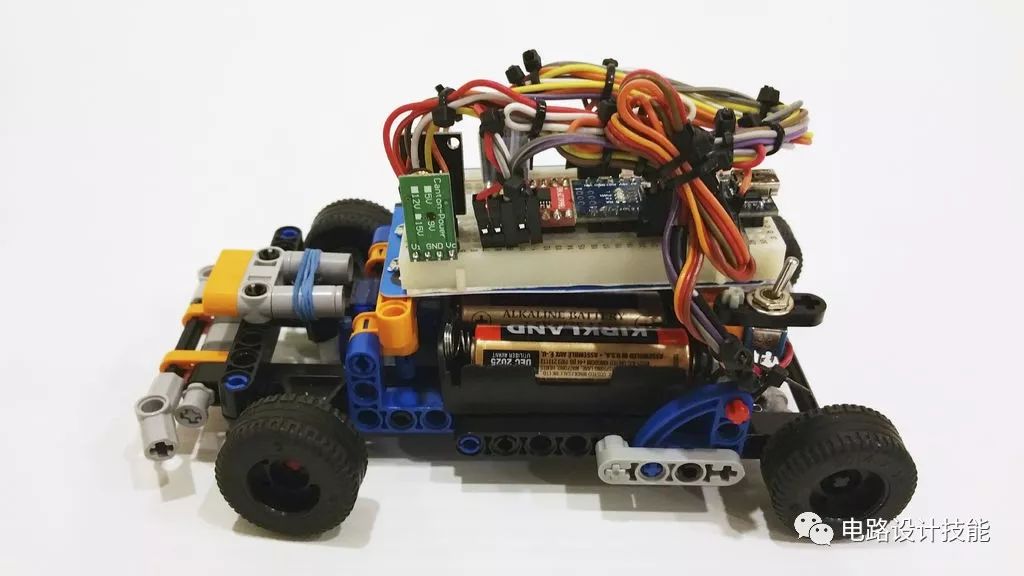

其实呢,这是一种误解,你可以把FPGA当做是数字世界的乐高(Lego),它由几种最基本的单元(每种单元数量有很多很多)让你组成自己想实现的功能。能玩好乐高就一定能玩好FPGA。乐高玩得好不好,取决于什么因素?

通过一些最基本的积木块可以拼出任何复杂的物体

- 第一要素 - 先要了解供你玩的“乐高”套装里都有哪些单元?每个单元都有哪些特性?不同单元之间是如何拼接的?没有这些全局的信息和知识在你的脑子里,你要从几千个piece里面去组装一辆车、构建一个城堡,将是非常困难甚至不可能的。

- 第二要素 - 要有正确的思维方式。你至少要知道搭建一辆车需要四个轮子、一个方向盘、一个发动机,这些部件之间如何通过其它的单元有机组合在一起,彼此之间如何搭配。不知道车子需要轮子,不知道轮子要装在底盘上是无法组装出一辆车来的,即便有再多的单元也没有用。

要通过积木构建一辆车,首先要知道都有哪些积木零件可以用,其次要知道这些部件之间的逻辑关系

学习使用FPGA的道理跟玩乐高没啥区别,同样是:

- 了解FPGA是什么?玩乐高的人不用操心什么是乐高,这个知识是由玩乐高的人的父母掌握了,并帮他选好型了;

- 要充分了解FPGA内部都有什么功能单元(逻辑单元、存储器、时钟产生、可编程IO等) ,这些单元都有什么用?用起来都有哪些要注意的地方,各个单元之间如何配合?尤其是针对你要用的具体型号,你要知道你用的这个型号的器件内部的各种功能单元具体有多少数量,够不够你项目使用的;

- 数字逻辑的设计思想 - 针对任意一项具体的功能,如何组合你器件内的单元来实现,需要哪些单元?如何连接这些单元?各个单元之间连接的先后顺序如何?这就需要比较扎实的数字电路/数字系统设计的基础知识以及逻辑思维能力。

当然你也需要一些工具来帮助你实现,比如一套从头到尾执行的设计环境(FPGA厂商提供的编译工具 - Lattice的Diamond、Intel的Quartus、Xilinx的Vivado),一种连接你的逻辑思维和机器操作之间的沟通工具 - 设计语言(原理图、Verilog、VHDL等等)。

下面我们以小脚丫FPGA为例,看看我们要学好FPGA必须掌握哪些知识。

首先FPGA是什么?

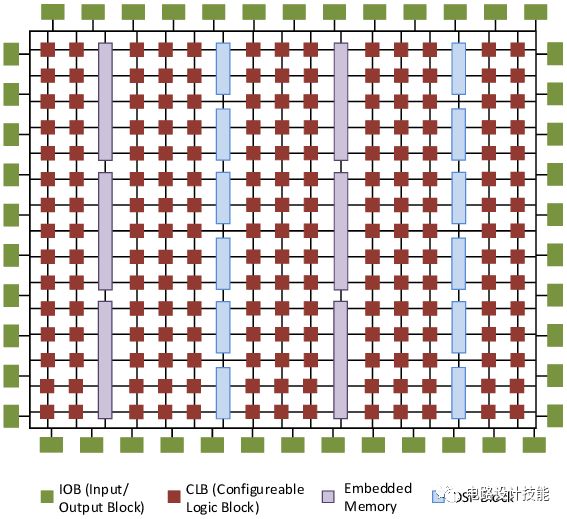

四个字母Field(现场) Programmable(可编程) Gate(逻辑门) Array(阵列)凸显了大量的 逻辑门单元 ,这些逻辑单元是可以在任何地方随时进行组装的,这是不是跟乐高玩具一样?逻辑门单元是构成一切数字逻辑器件的基本单元,在数字世界里你想做任何事情、实现任何功能,都可以通过逻辑门的堆砌来实现,也就是说FPGA在数字领域里几乎无所不能,因此n年前我国的某一个FPGA公司在向国务院领导描述其产品的时候称他们做的是“万能芯片”(用这种通俗易懂的说法忽悠国家的经费)。万能有些夸张,但FPGA高度灵活,理论上来讲,只要有足够的资源(积木数量足够多)几乎可以实现数字域的任何功能,受限的是速度、功耗以及系统的成本。

一个典型的FPGA架构及其内部主要功能单元

FPGA里面有什么?

我们以基于Lattice的FPGA的小脚丫看一下该FPGA内部都有哪些资源以及相应资源的数量,如下是该器件LCMXO2-4000HC-4MG132C内部的功能框图:

Lattice版本小脚丫FPGA芯片内部的主要功能单元

该器件的具体资源参数如下:

- 4320个LUT资源 - 每个LUT(查找表)有4个输入,16种状态,并一个寄存器,这就像乐高里的积木块,用来实现各种逻辑功能,至于4320是多还是少?这个要看你做的项目需要的逻辑资源,对于FPGA的初学者来讲4000多个LUT已经足够多,实现很多没听说过的功能都已经绰绰有余了;

- 92Kbit RAM - 这是在逻辑之外的成块状的存储器,可以灵活配置成各种位宽、各种读写模式的存储功能,比如FIFO、双口RAM等;

- 96Kbit用户闪存 - 这是Lattice 的一个创新,后来Altera/Intel也学着做了MAX10,就是将配置FPGA的存储器从外面的PROM变成了集成在FPGA内部的Flash,可以反复编程,从此FPGA不再外挂一个累赘了,用起来就像PLD一样方便;

- 嵌入式功能块(硬核):一路SPI、一路定时器、2路I2C,这可是MCU除了ALU、总线之外最基本的功能模块,都硬化到该FPGA内部了,也就意味着如果你想用这个FPGA做一个MCU玩玩,可以直接将这些已经硬化的功能块通过总线挂在处理器上,没必要再写这些功能,并且占用逻辑资源了;

- 2+2路PLL+DLL - 我们前面讲过外部常用的时钟产生器(比如晶振)产生的频率不高,但FPGA内部可以工作到很高的速度,因此现在几乎所有FPGA器件都有内置的PLL将外部的低频率的时钟整到很高频率,比如小脚丫的外部时钟为12MHz,内部PLL可以将它倍频到400MHz,非常快吧?

- 支持DDR/DDR2/LPDDR存储器 - 这是说该器件能够直接挂这些存储器,适配它们的电平和时序;

- 104个可热插拔I/O - 每个I/O管脚可以单独编程为输入、输出、上拉或下拉、并可以设置器输出阻抗,以便支持不同的接口协议,就像城市连接外部的道路可进可出、有的铺沥青、有的是土路;

- 内核电压2.5-3.3V,供电电压的范围比较宽;

- 132脚BGA封装,引脚间距0.5mm,芯片尺寸8mm x 8mm;

FPGA能做什么?

知道了FPGA内部的资源,也就心里有数它能做什么了。就像一座城堡,内部居民的生活丰富多彩,无论他们以何种形式进行组合,他们所做的事情取决于这些居民以及他们拥有的资源,其生活模式被城堡的设计者所定义(城市管理、文化等等等)。

但从宏观上来看这个城堡起到的功能很大程度上取决于这个城堡同外部世界的连接,没有这些同系统的连接,城堡内部的任何行为对于系统来讲都没有意义。FPGA可以是系统的一个重要组成部分,但它仅仅是一个部分而已,就像一个城堡一样,它只有同外部进行连接并执行系统通过这些连接给其分配的功能才有意义。

因此FPGA通过其I/O管脚连接外面的世界,我们使用的小脚丫芯片有132个管脚,除去电源、地之外还有104个管脚可以用来同外界进行联系。

)

做为一款让FPGA初学者学习的平台,首先要满足初学者基于掌握的数字电路知识进行做项目的定位,先要体验组合逻辑、时序逻辑、状态转换等数字电路的基础概念,而体验这些概念就需要一些必要的输入(按键、开关)和必要的输出(通过单色LED灯、三色灯、数码管进行各种方式的显示),综合考虑板子的尺寸以及初学者随时随地能练习的要求,我们经过取舍后选定了如下的板上功能及连接:

通过FPGA的IO管脚连接的板上的功能

板载资源:

- 两位7段数码管 - 可以以状态、数值的变化来显示内部逻辑运行的信息;

- 两个RGB三色LED - 可以以LED的亮度、颜色灯的变化显示内部逻辑运行的信息;

- 8路用户LED - 可以通过组合来形象地显示内部逻辑运行的信息;

- 4路拨码开关 - 做为状态的输入;

- 4路按键 - 做为外部条件变换的输入;

板子上的这些功能说明

当然作为一个灵活的学习模块,我们还要给用户留下一定的灵活扩展的空间,让用户以各种方式来连接其计划连接的其它器件,在这个模块的周边我们留出了36个信号管脚(4个电源、地除外)给用户,用户可以灵活配置、应用这些管脚,让自己的系统充分利用这些管脚让FPGA内部的逻辑资源执行分配的任务。

-

请教怎么样才算学好了单片机2012-02-10 3233

-

怎样才能学好fpga???2012-07-29 3698

-

新手求指教---怎样学好FPGA呀2013-05-29 2989

-

怎样才能学好arduino?2015-11-13 8972

-

华和机电分享怎样学好嵌入式?2017-01-09 4597

-

初学者怎样学好电子知识2017-04-21 3233

-

请问怎样学好C语言?2019-04-12 1309

-

飞机表现出什么现象才叫调好了?2019-08-01 2335

-

怎样的倒车影像才算好用2016-08-03 1107

-

三大前辈教你怎样学好模拟电路2016-09-13 1666

-

怎样学好模拟电路2016-09-20 965

-

怎样才能学好电路分析2018-03-23 22826

-

如何学好FPGA呢2019-02-23 860

-

FPGA视频教程之如何学好FPGA的视频教程资料免费下载2019-02-28 1528

-

直线模组怎样保养才合理?2023-07-03 1269

全部0条评论

快来发表一下你的评论吧 !