一文详解算术运算电路

描述

算术运算电路

算术运算电路的核心为加法器.

基本加法器

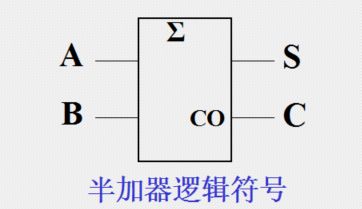

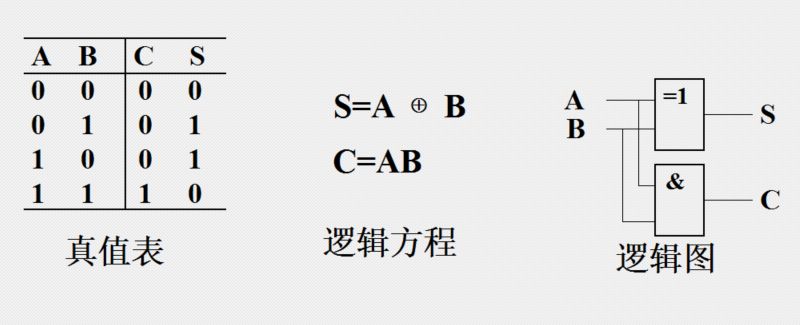

1. 半加器(HA)

仅考虑两个一位二进制数相加,而不考虑低位的进位,称为半加。

设: A、B为两个加数,S 为本位的和,C 为本位向高位的进位。则半加器的真值表、方程式、逻辑图如下所示

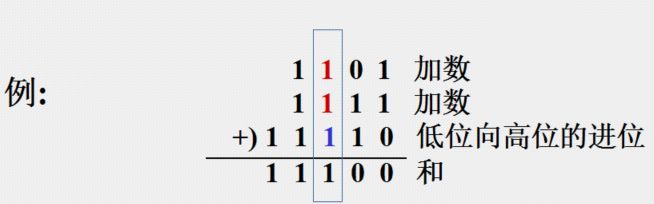

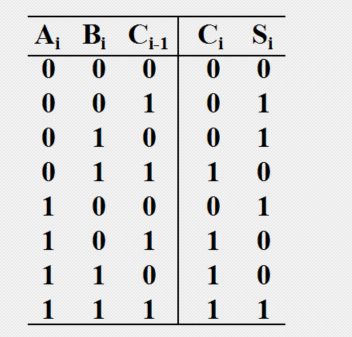

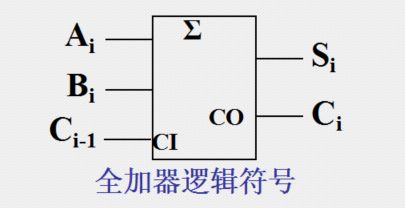

2. 全加器

在多位数相加时,除考虑本位的两个加数外,还须考虑低位向本位的进位.

实际参加一位数相加,必须有三个量,它们是:

本位加数 Ai 、Bi ;

低位向本位的进位 Ci-1

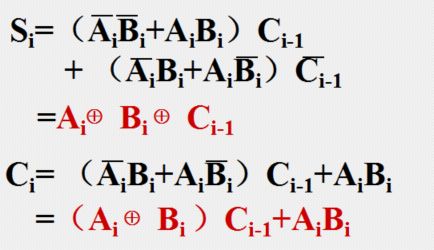

一位全加器的输出结果为:

本位和 Si ;

本位向高位的进位 Ci

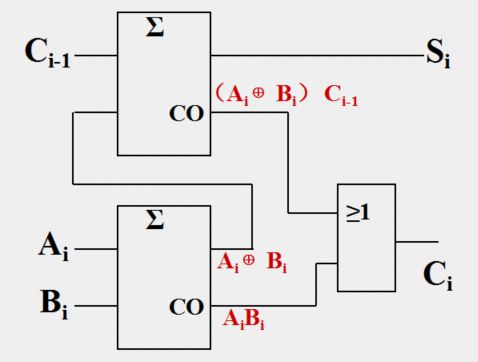

全加器电路设计:

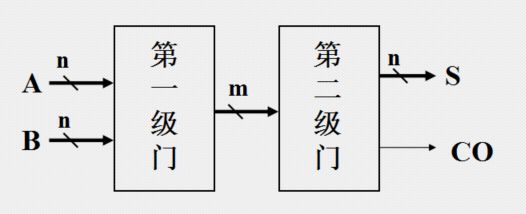

由两个半加器实现一个全加器

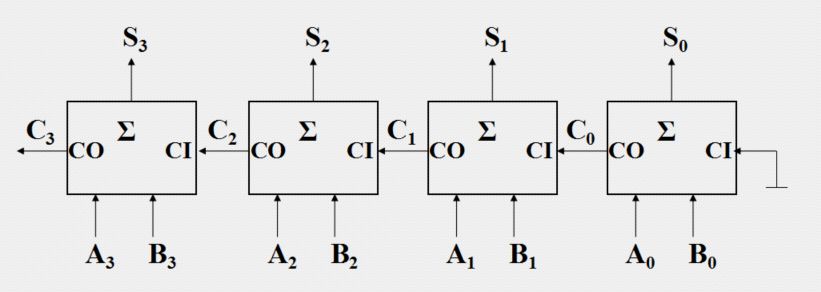

3. 串行进位加法器

当有多位数相加时,可模仿笔算,用全加器构成串行进位加法器.

四位串行进位加法器

串行进位加法器特点: 结构简单; 运算速度慢.

高速加法器

(1) 全并行加法器

特点: 速度最快,电路复杂。

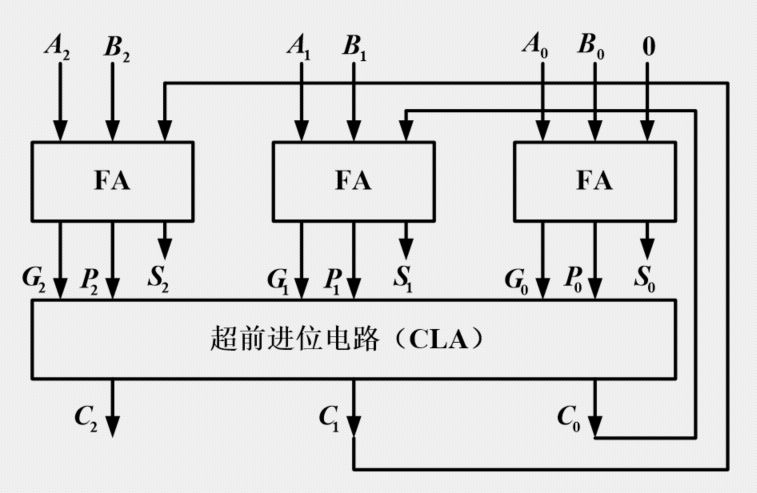

(2) 超前进位加法器

设计思想: 由两个加数,首先求得各位的进位,然后再经全加器算出结果.

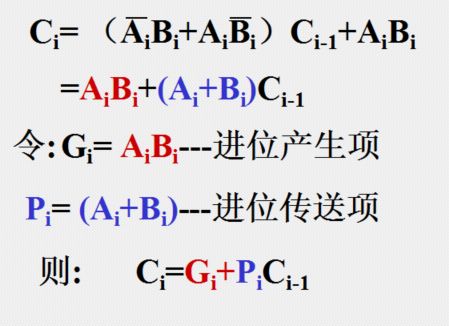

全加器的进位表达式:

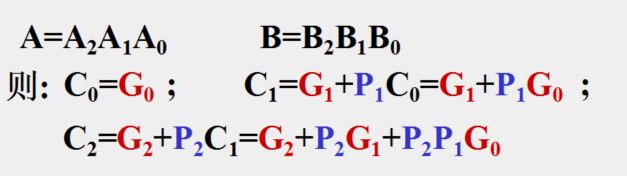

若两个三位二进制数相加

由Pi 、Gi 并经过两级门电路就可求得进位信号C.实际实现中,是将求Gi和Pi的电路放进全加器中,而将全加器中求进位信号的电路去除.

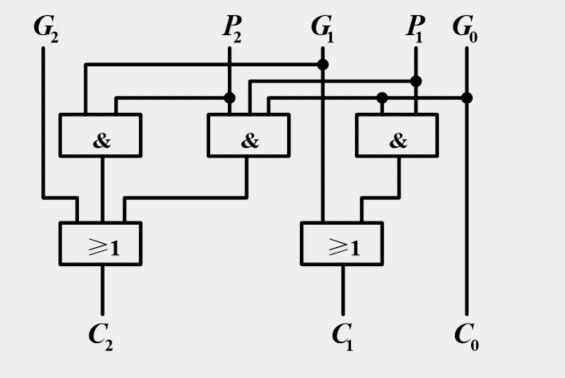

根据Gi 、Pi 来求进位信号C 的电路称为超前进位电路(CLA)

CLA逻辑图:

3位超前进位加法器

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

可变精度算术运算2009-09-22 3067

-

FPGA基础学习笔记--组合逻辑电路-算术运算电路2012-02-23 5016

-

算术运算符的相关资料分享2021-11-30 1030

-

LabVIEW对8-bit图像进行滤波或算术运算2022-06-16 13667

-

MCS-51算术运算指令2006-04-03 1930

-

算术运算指令2009-03-14 2424

-

集成算术/逻辑单元举例2009-04-07 1605

-

多功能算术/逻辑运算单元(ALU) ,什么是多功能算术/逻辑2010-04-13 29818

-

一文读懂如何验证74ls181运算和逻辑功能2018-05-09 43770

-

51单片机的算术和逻辑运算功能介绍2019-09-14 5326

-

计算机算术运算实现原理全解2021-03-26 1036

-

一文详解分立元件门电路2023-03-27 4972

-

一文详解pcb地孔的作用2023-10-30 3136

-

一文详解pcb电路板是怎么制作的2023-12-05 3156

-

74F382 4位算术逻辑单元:功能、特性与应用详解2026-04-10 135

全部0条评论

快来发表一下你的评论吧 !