PCIE协议及PCIE体系结构说明

接口/总线/驱动

描述

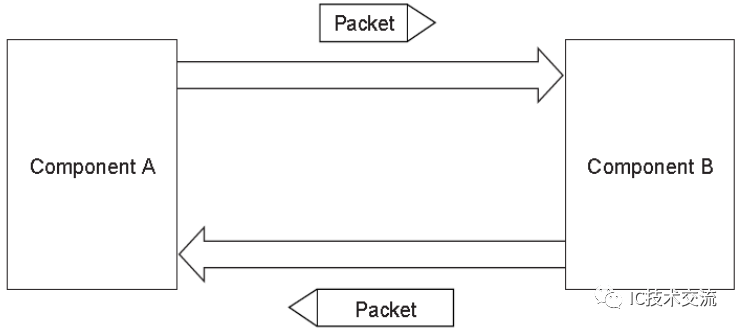

一、link和lane

一组link就是连接两个port之间的若干条lane,通常为x1/x2/x4/x8/x16。每条lane包含四根线tx_p/m,rx_p/m(两组差分对)。这里的port/component可以理解为一个设备,如果pcie支持bifurcation,则一个x16的接口可以连接多个port(2个x8/1个x16/4个x4/8个x2等),每个port中每条lane的linkID相同,不同port间的linkID不同。

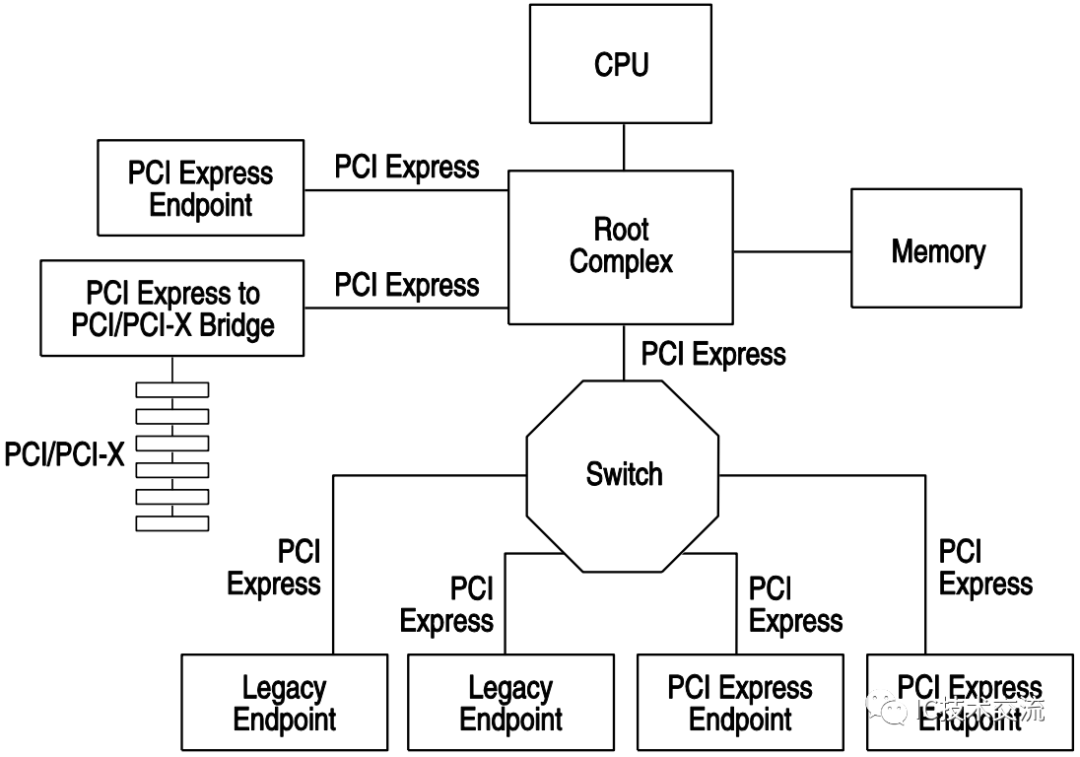

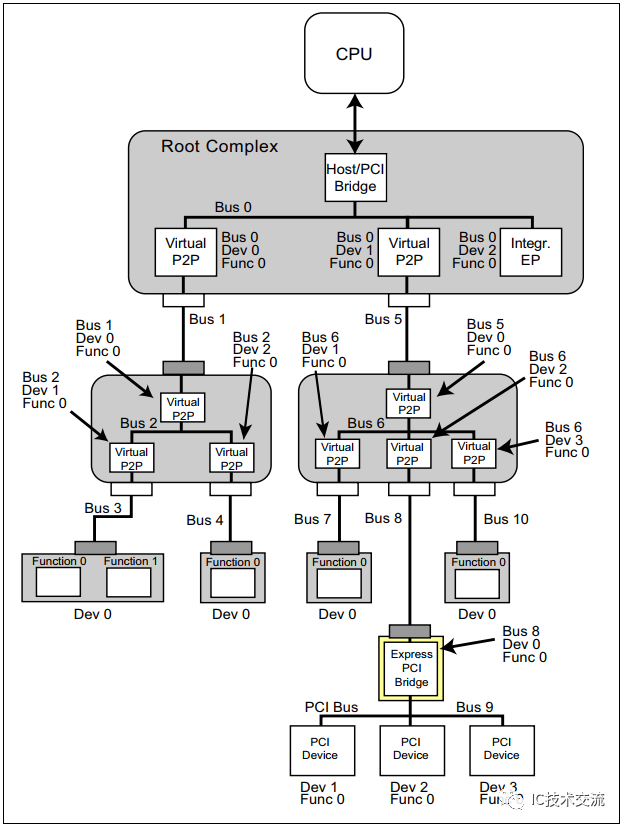

二、PCIE体系结构说明

Root Complex:

RC是CPU和PCIE总线连接的接口。主要功能是完成存储器域到PCIE总线域的地址转换,随着虚拟化技术的引入,RC功能也越来越复杂。RC把来自CPU的request转化成PCIE的4类request(configuration、memory、I/O、message)并发送给下面的设备。

Switch & Bridge

Switch提供了分散/聚合的功能,它允许更多的设备接入到一个PCIE port。它扮演了数据包路由的功能。Bridge提供了一个转换接口用来连接其他的总线,如PCI/PCI-X。这样可以允许在PCIE的系统中接入一张旧的PCI设备。

PCIE Endpoint:

它只有一个上游端口,位于PCIE拓扑结构的树的末端。他作为请求的发起者或者完成者。分为Legacy Endpoint、PCIE Endpoint和Root Complex Integrated Endpoint三种。

虚拟化技术:

虚拟化可以理解为一台电脑运行了两套系统,比如我们在windows下安装linux虚拟机,两套操作系统共用一套硬件,这要求每套系统的存储域范围不重叠,即对应了两套地址转换,将存储器地址转换为不同的物理地址,以此实现一套硬件运行多系统。虚拟化技术的核心是地址的映射和转换。

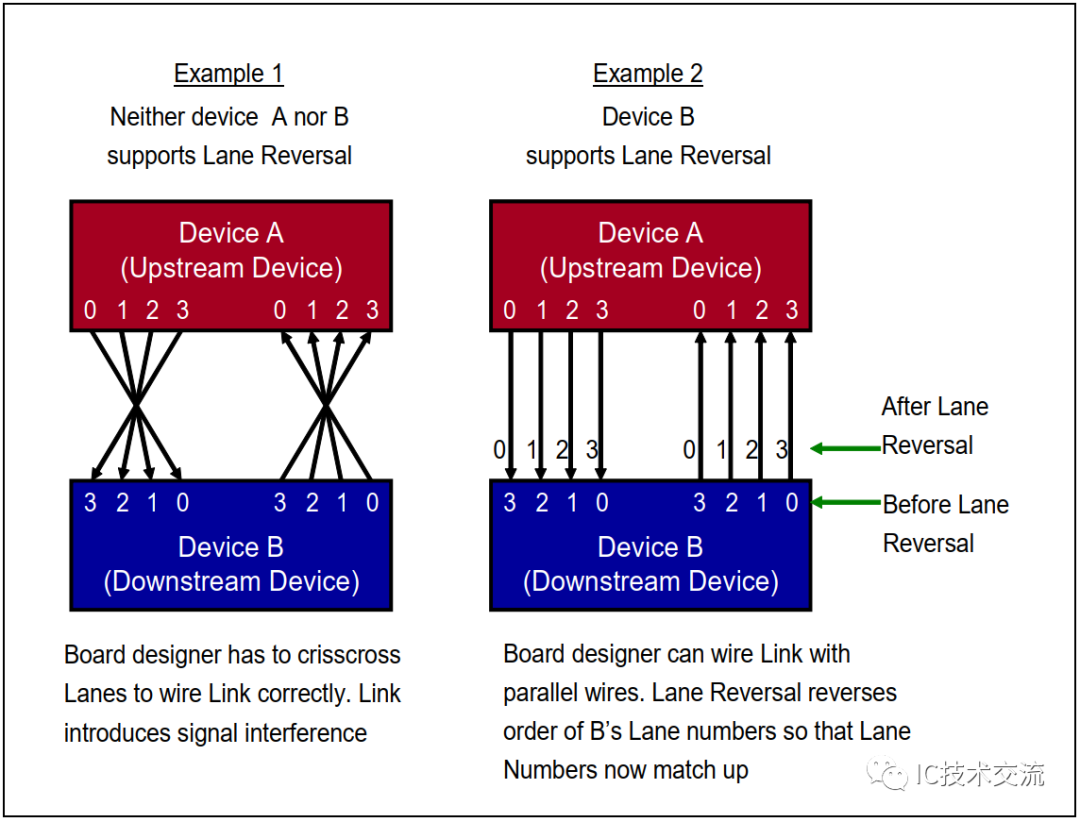

三、PCIE lane翻转和PN翻转

为了方便板子布线,允许lane翻转

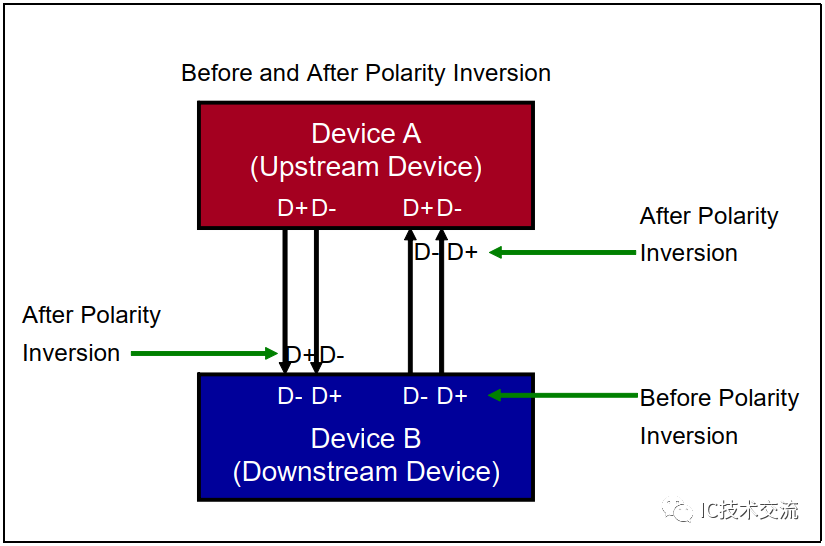

每条lane的差分信号也可翻转。

lane翻转和pn极性翻转有以下要求:

1、PN翻转无限制,可翻转部分lane,也可只翻转TX或RX

2、lane翻转必须全部翻转,不能部分翻转

3、lane翻转TX/RX必须同时翻转,不能只翻转TX或RX

4、lane翻转和PN翻转可以同时存在

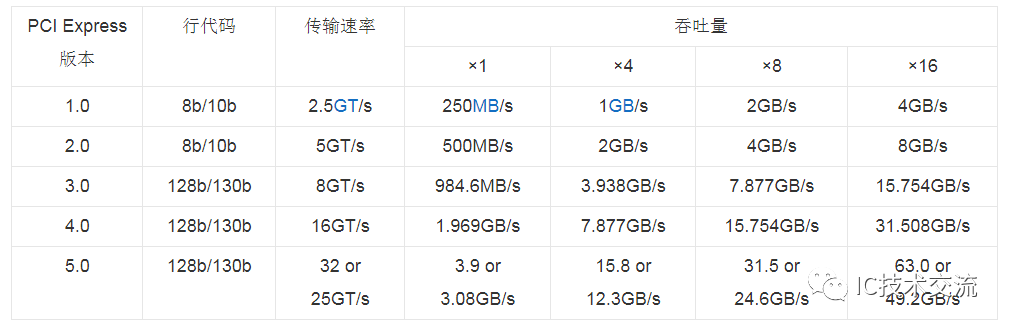

四、吞吐量

PCIE gen1/2使用8b/10b编码,编码效率为0.8

PCIE gen3/4/5使用128b/130b≈0.985

PCIE 5.0x4的速率为:32Gbpsx4x128÷130÷8b/B≈15.754GB/s

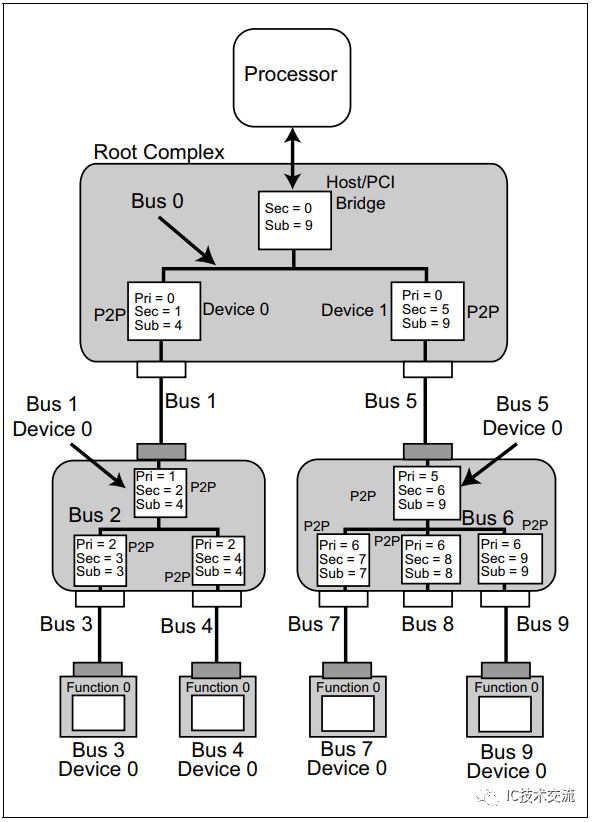

五、PCIE枚举图开机启动时软件会扫描系统中的所有PCIE设备(PCIE枚举),对软件而言,Bus/Device/Function是必不可少的。 Bus:在一个系统中存在1~256个bus; Device:在一条bus中存在1~32个设备; Function:每个设备有1~8个功能;

对于每个中间桥而言,三条Bus必须知道:Primary Bus/Secondary Bus/Subordinate Bus: Primary Bus:上游bus号 Secondary Bus:下游第一级bus号 Subordinate Bus:下游最大的bus号

六、PCIE设备与系统地址映射

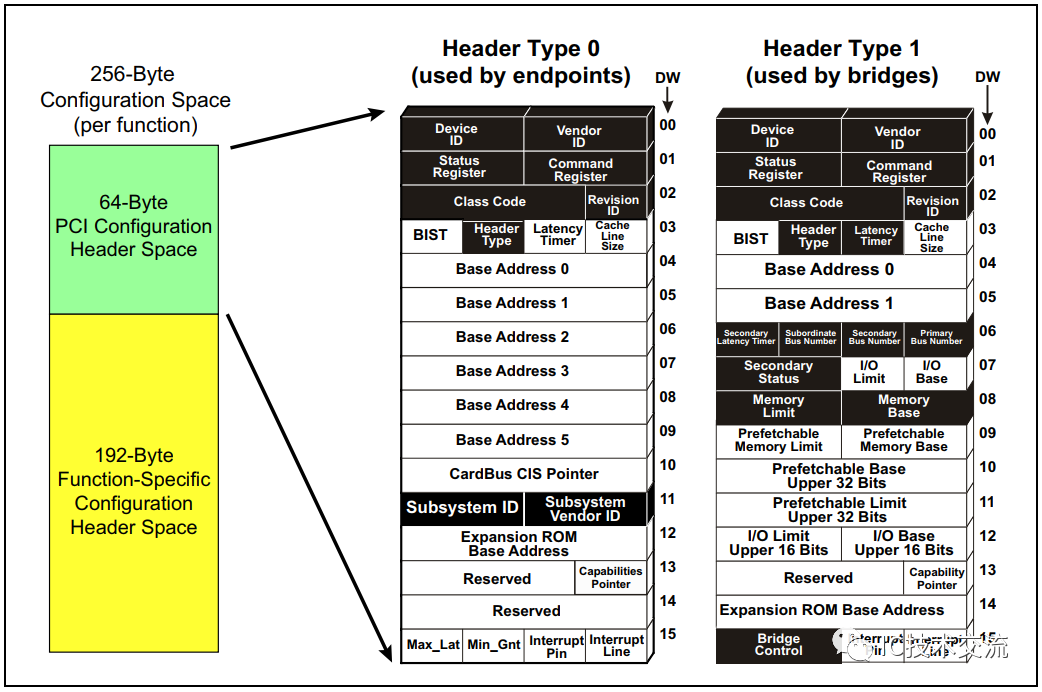

PCIE设备有四种地址空间: 1、Configuration Space配置空间; 2、Memory Space存储空间; 3、I/O Space空间,存在于老的PCI设备; 4、Message Space,PCIE设备新增,包含边带指示信号,比如中断; 这些PCIE总线地址空间需要在初始化时就映射为存储器域的存储器地址空间,方便处理器访问。系统软件对PCIE总线进行配置时,首先获得BAR寄存器的初始化信息,之后根据处理器系统的配置,将合理的基地址写入到相应的BAR寄存器中,这个过程在BIOS运行阶段和OS启动阶段完成。系统软件还可以使用该寄存器获得PCIE设备使用的BAR空间的长度,其方法是向BAR寄存器写入0xFFFF_FFFF后再读取该寄存器。每个PCIE设备在BAR中描述自己需要占用多少地址空间,BIOS或OS通过所有设备的这些信息构建一张完整的地址映射表,描述系统中资源的分配情况,然后再合理地将地址空间配置给每个PCI设备。BAR在bit0来表示该设备是映射到memory还是I/O,BAR的bit0是readonly的,就是说设备寄存器映射到memory还是I/O是由设备制造商决定的,其他人无法修改。

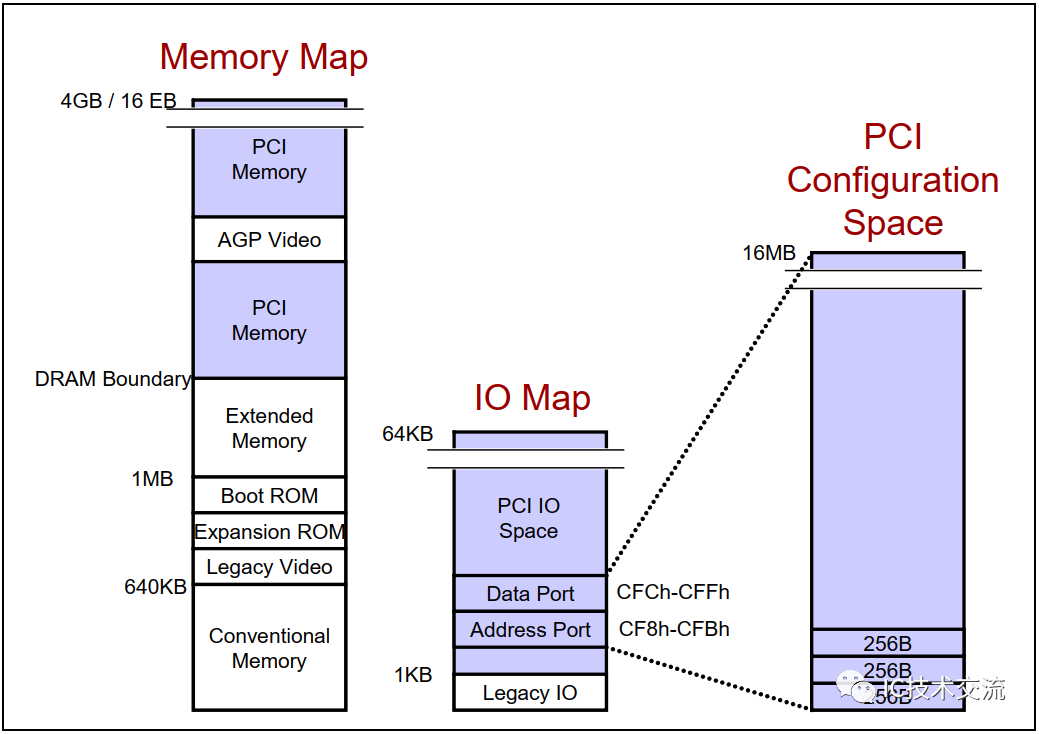

PCI的配置空间如上图所示,每个设备的每个function都有独立的配置空间,大小为256B,前64B为表头,PCIE设备的配置空间拓展为4KB。 所有PCI的配置空间为: 16MB=256Busx32Device/Busx8Function/Devicex256B/Func 所有PCIE的配置空间为: 256MB=256Busx32Device/Busx8Function/Devicex4KB/Func X86架构地址又分为memory space和I/O space。I/O space可以理解为直接寄存器读写地址空间,属于X86早期产物,访问速率较慢。 x86:32bit(4GB) x64:64bit(16EB) I/O space:16bit(64KB)

从上图可知Memory地址前640KB为Conventional Memory,1MB间的为Boot ROM,中间一段为DRAM内存,其余的分配给PCI存储器域。I/O地址中可以通过CF8-CFB和CFC-CFF访问PCI的16MB配置空间,剩下的为各PCI设备映射的I/O地址空间。对于PCIE而言,配置空间通过memory的方式映射(MMIO),不再通过I/O Map的方式访问,这会占用一部分系统内存,也是内存用不满的原因(还有主板上的集成显卡/BIOS等也会占用内存)。

编辑:黄飞

-

基于FPGA的PCIE总线扩展卡的设计2010-10-08 2382

-

PCIe引脚定义和PCIe协议层介绍2023-09-26 27143

-

nvme IP开发之PCIe上2025-05-17 6285

-

采用FPGA实现PCIe接口设计2019-05-21 4458

-

PCIe的技术原理详细说明2021-05-25 7042

-

PCIe AMBA集成指南2023-08-17 1368

-

体验紫光PCIE之使用WinDriver驱动紫光PCIE2023-11-17 1854

-

《IP交换技术协议与体系结构》2006-03-24 1630

-

LTE体系结构2009-06-16 10278

-

一个简化的PCIe总线体系结构2018-04-21 6441

-

讨论SERIALTEK公司发布PCIE GEN5 X16协议分析仪的性能与结构与应用领域2021-03-09 4561

-

微处理器体系结构2021-04-12 1155

-

软件无线电的体系结构2021-05-31 1228

-

无线移动因特网体系结构、协议及业务2023-11-20 507

-

pcie协议规范2024-05-16 1054

全部0条评论

快来发表一下你的评论吧 !