半桥LLC电路中功率管驱动的尖峰

描述

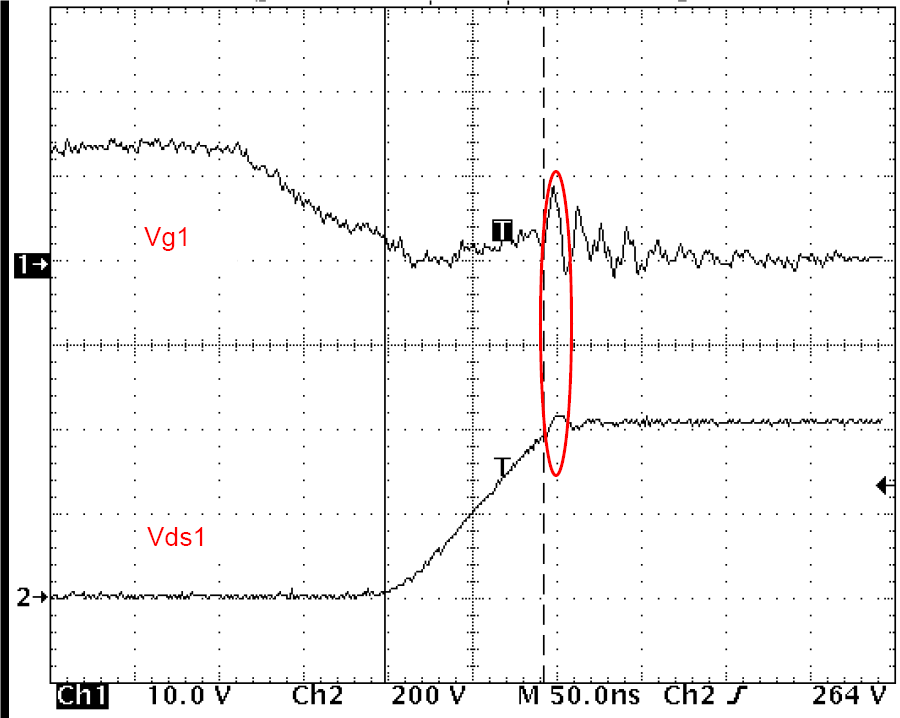

如图19所示,当上管关断后,在上管的驱动Vg1上出现一个电压尖峰,当死区时间减少,下管ZVS开通不完全时,这个电压尖峰会更大,从图20可以看出这个尖峰出现的时刻和Vds1下降的时间是吻合的。

图19 上管关断时Vg1的电压尖峰

图20 上管关断时Vg1和Vds1波形

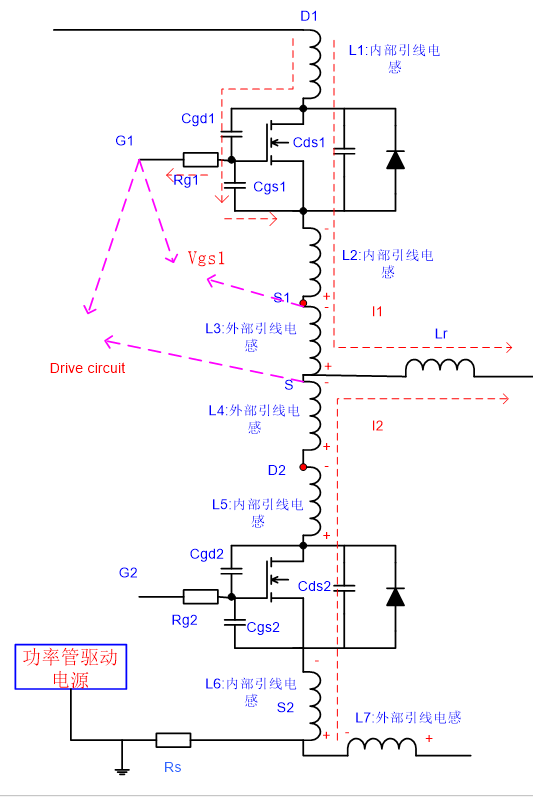

我们将模块上下管用其结构示意图来表示,功率管的D,S极都存在引线电感,而且还有PCB板引入的到S脚的引线电感,我们测试时,测试到的是G1和S1间的电压差Vgs1。

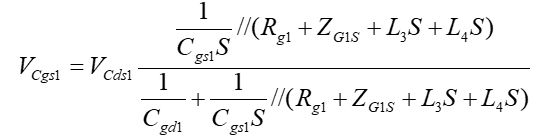

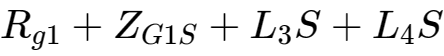

当上管关断时,HO为低电平(驱动电路见图1),Cgs1通过Q305组成的电路放电(等效电阻ZG1S),放到门限电压时,MOSFET关断,此时上下管开始换流,电流 i1减少,i2增加,电感的电流方向如图所示,电容Cds1开始充电,Vds1上升;Cgd1,Cgs1,以及G1到S的驱动阻抗ZG1S,L2,L3组成的电路也开始对Cgd1,充电,所以Cgs1电压开始上升, 测试到的电压

(引线电感的电压上正下负为正方向),

如果由于死区时间的减少,造成下管不能完全的ZVS开通,在下管开通的瞬间,就会有一个较大的冲击电流流过Q1和Q2的极间电容和引线电感,在Cgs1行成一个更高的密勒平台,同时在引线电感L2,L3上造成一个上正下负的电压降,这个电压降叠加在密勒平台上,使驱动VG1S1的电压尖峰更高。

同时:也可以看到,

,如果驱动阻抗越大,VG1S就越大,测试到的电压尖峰也就越大,引线电感L3越大,测试到的电压尖峰也会越大。而功率管是否会导通取决于Cgs1

的电压和持续的时间:

从上面的公式可以看出,如果能让上管关断时

尽可能的减少,就可以降低功率管导通的风险,同时尽量减少功率管G,D之间的耦合电容也可以减少Cgs1上的电压。

图21 半桥电路上下管结构示意图

-

LLC 半桥谐振电路的设计与应用2025-10-22 543

-

功率管的开关波形对尖峰干扰的影响与抑制2023-11-29 1813

-

半桥LLC电路中上管VDS的尖峰2023-03-24 6533

-

半桥LLC电路中模块损耗的影响2023-03-23 5906

-

【干货分享】LLC谐振半桥电路分析与设计2021-07-24 6128

-

LLC谐振半桥电路分析与设计2021-05-13 4532

-

LLC半桥谐振电感设计2021-04-16 2253

-

LLC半桥谐振电路的设计与应用(资料分享)2016-01-15 13335

-

半桥功放电路的直通现象2014-07-25 7677

-

LLC谐振半桥DC-DC电路设计2013-05-27 3683

-

LLC半桥谐振功率级电路图2012-06-07 9056

-

线性LED驱动器半桥LLC电路2011-03-31 2657

全部0条评论

快来发表一下你的评论吧 !